1999 IEEE Workshop Interconnections within High-Speed Digital Systems

## Device and Interconnect Technologies for ~100 GHz mixed-signal ICs

Mark Rodwell University of California, Santa Barbara

rodwell@ece.ucsb.edu 805-893-3244, 805-893-3262 fax

## Device and Interconnect Technologies for ~100 GHz mixed-signal ICs

Two topics:

ICs \*for\* high-frequency interconnects RF/wireless, optical fiber ICs \*needing\* high-frequency interconnects 100 GHz digital logic, GHz ADCs/DACs

The organization:

what are the future applications ? what are the requirements ? what is the state of the art ? challenges for future high speed ICs ...and how my group is attacking them Applications: ICs \*for\* high-frequency interconnects ICs \*needing\* high-frequency interconnects

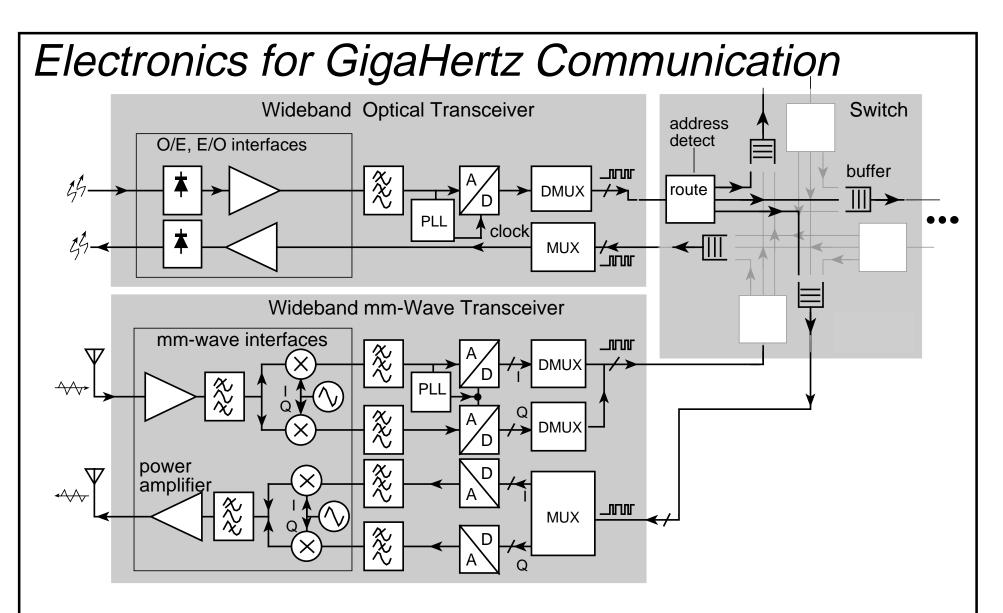

*Transceivers*: very fast digital & mixed-signal ICs *Interfaces*: very wideband analog circuits, optoelectronics, mm-wave power *Switches*: ~10 GHz fast complex digital ICs Why electronic switching remains important

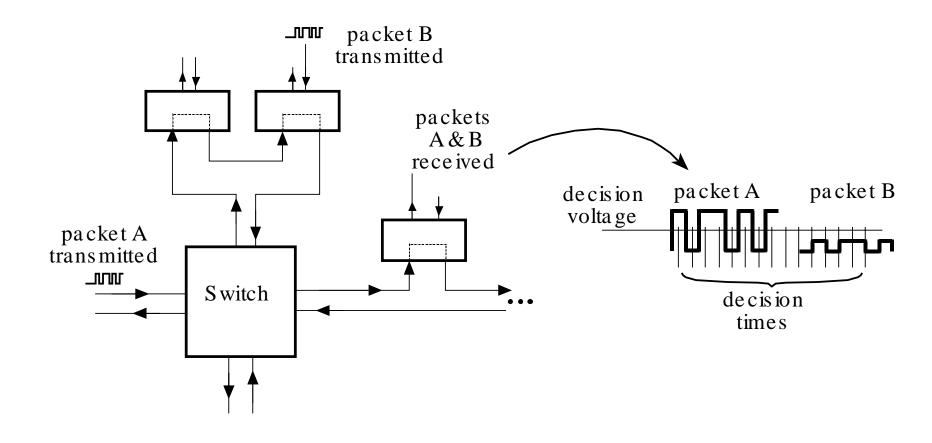

Packet switching in a transparent (optical) switch

Burst errors will arise due to timing and amplitude glitches Fix with digital (electronic) regeneration at switch -> all digital network

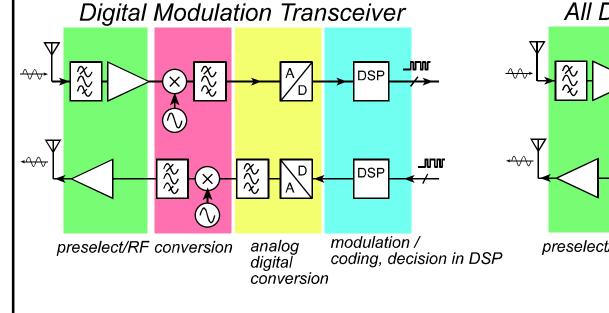

#### RF/Microwave ADCs/DACs/DDS: Towards the "Software Radio"

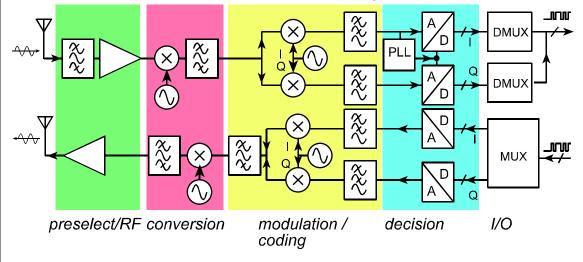

Transceiver: Today

#### Advantages

digital robustness, frequency agility complex modulation (spread spectrum...), simultaneous operation on many bands

#### Challenges

ADC needs \*\*enormous\*\* dynamic range DAC also must have very high SNR Enormous data reduction in DSP: very complex, very fast logic

All Digital Transceiver

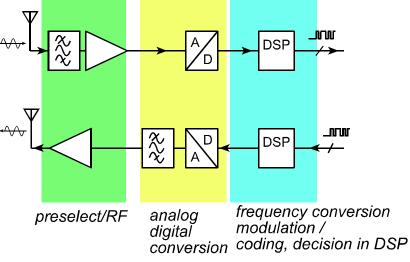

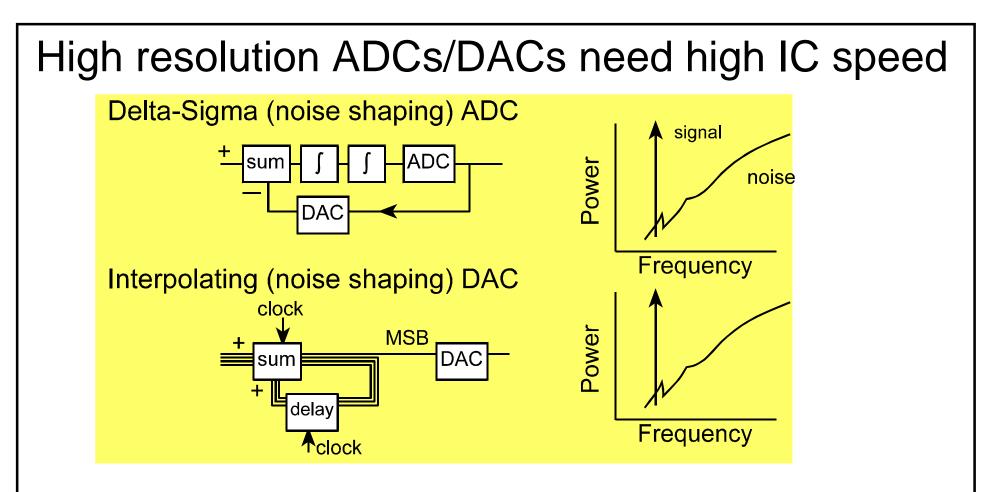

ADCs/DACs for radio:

high dynamic range required (10-18 bits)

Oversampling ADCs/DACs:

high resolution obtained through high oversampling

Microwave ADCs need very fast logic, very fast transistors

### Requirements: 100 GHz clock-rate logic

Fast transistors:

ADCs etc need very high ratio of transistor to signal bandwidth

High performance wiring :

millimeter-wave bandwidths with analog & digital signals ! *microstrip*-lines and ground-planes for signal integrity power delay products and impact of wiring

Outstanding heatsinking:

clock rates will be very high, so wiring delays must be small transistors must be close together ! high performance transistors use high power densities ! power density on die may approach 1 kW/cm<sup>2</sup> !

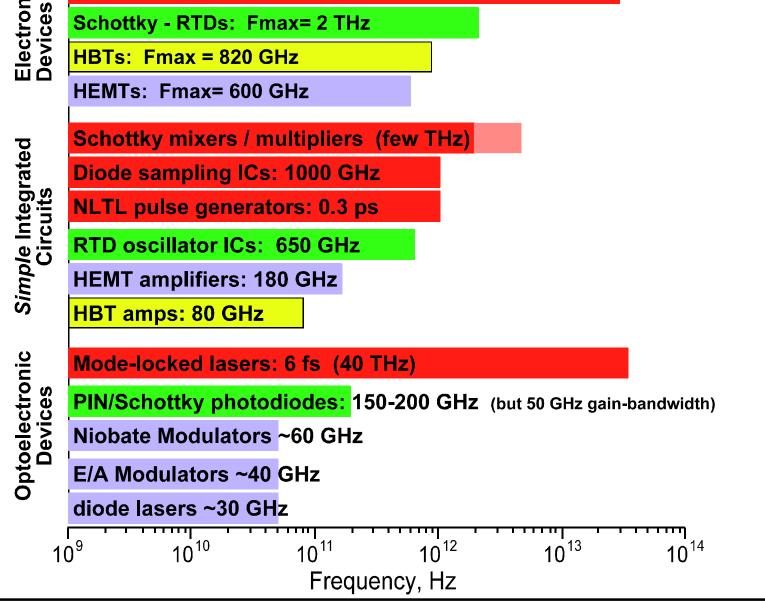

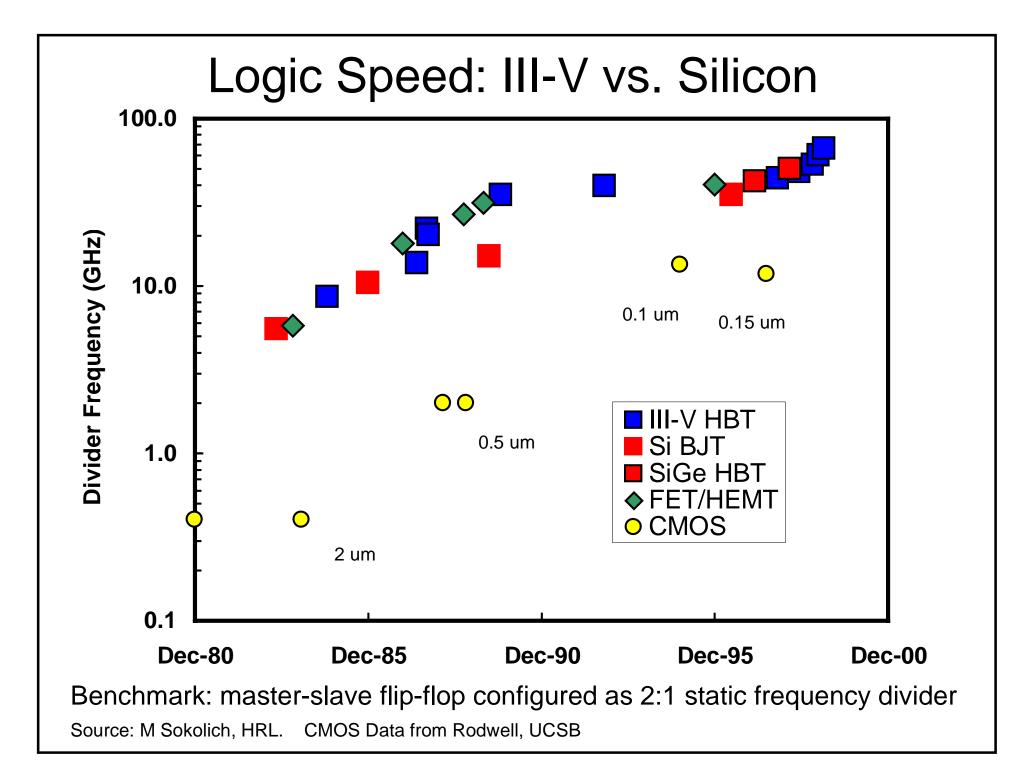

# state of the art

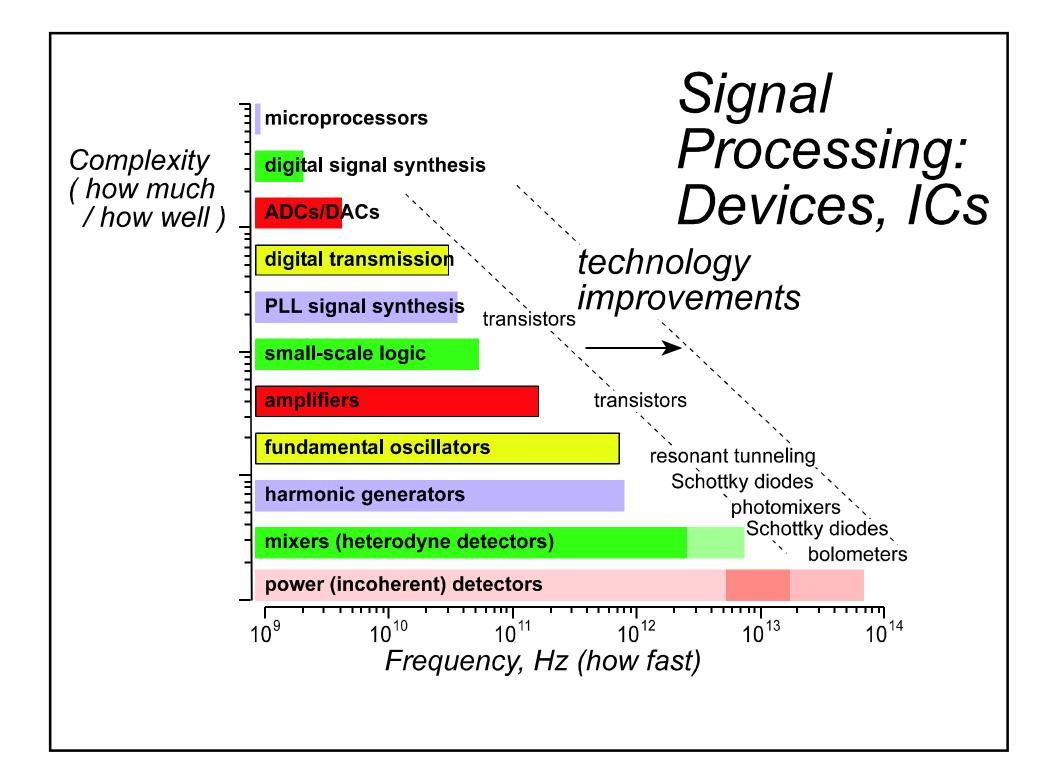

#### Devices and Simple ICs: State of Art, 1999

Electron Devices

Schottky mixer diodes: Fc~ 20 THz

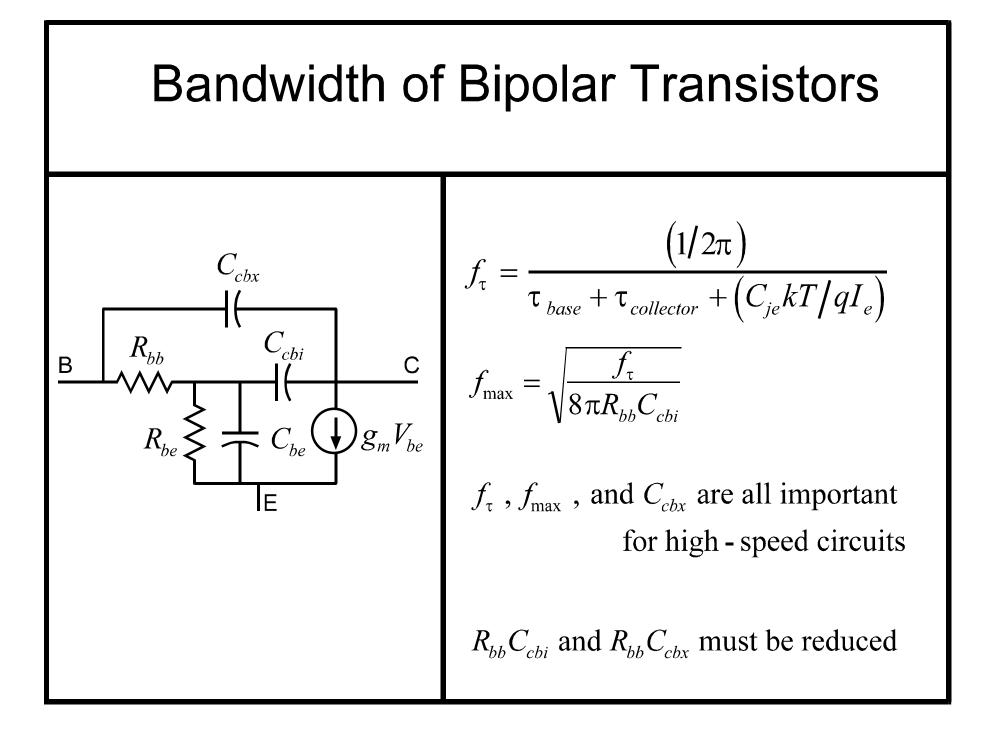

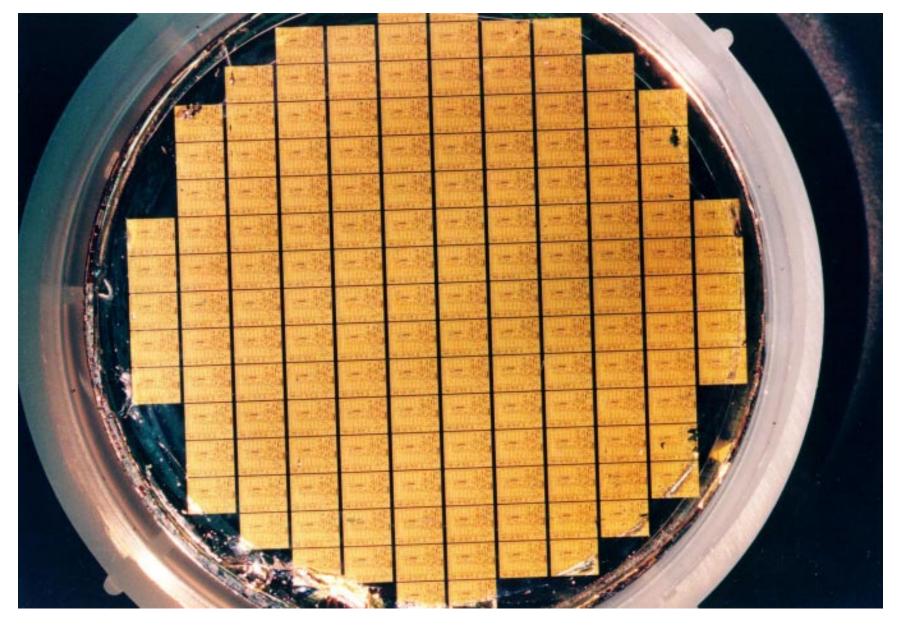

# HBT performance

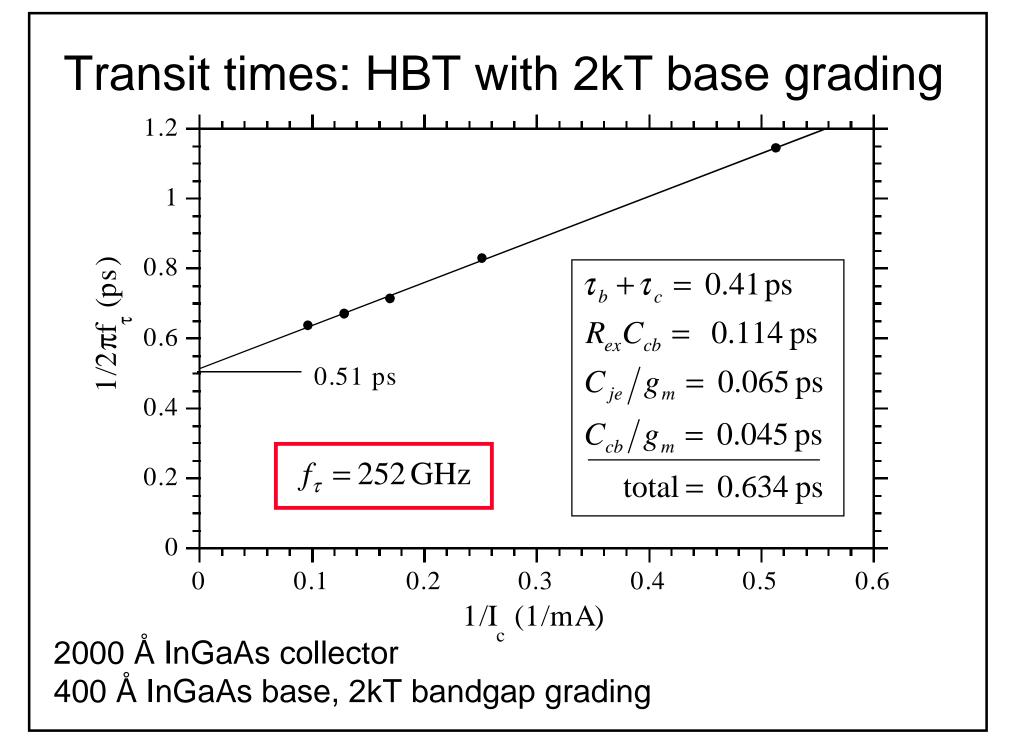

# Current-gain cutoff frequency in HBTs

$$\frac{1}{2\pi f_{\tau}} = \tau_{base} + \tau_{collector} + C_{je} \frac{kT}{qI_E} + C_{bc} \left( \frac{kT}{qI_E} + R_{ex} + R_{coll} \right)$$

$$\tau_{base} \approx T_b^2 / 2D_n \qquad \tau_{collector} \approx T_c / 2v_{sat}$$

Collector velocities can be high: velocity overshoot in InGaAs Base bandgap grading reduces transit time substantially RC terms quite important for > 200 GHz ft devices

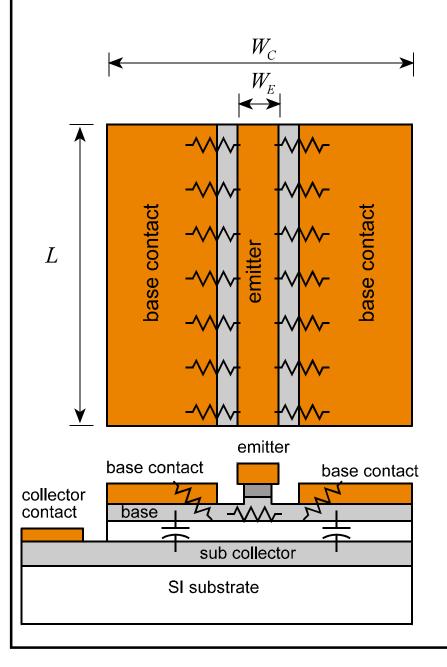

# Fmax in Double-Mesa HBTs

$$R_{bb} = \frac{1}{2L} \rho_{contact,horizontal} + \frac{\rho_{sheet}}{12L} W_{E}$$

$$C_{cb} = \frac{\varepsilon L}{T_{c}} W_{c}$$

Scaling emitter width does reduce base spreading resistance.

– but –

Minimum base resitance set by base contact resistance.

Minimum collector capacitance set by minimum base contact size

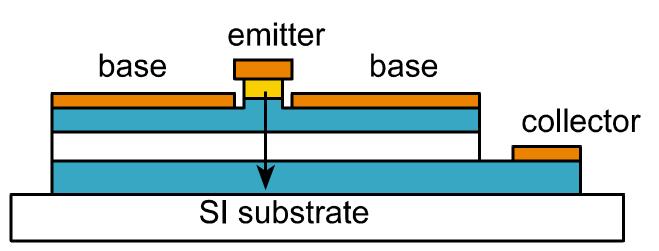

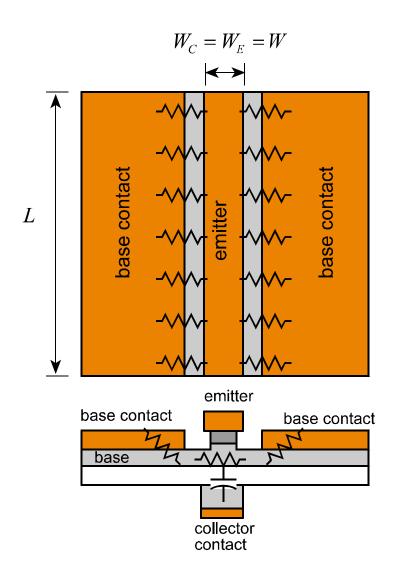

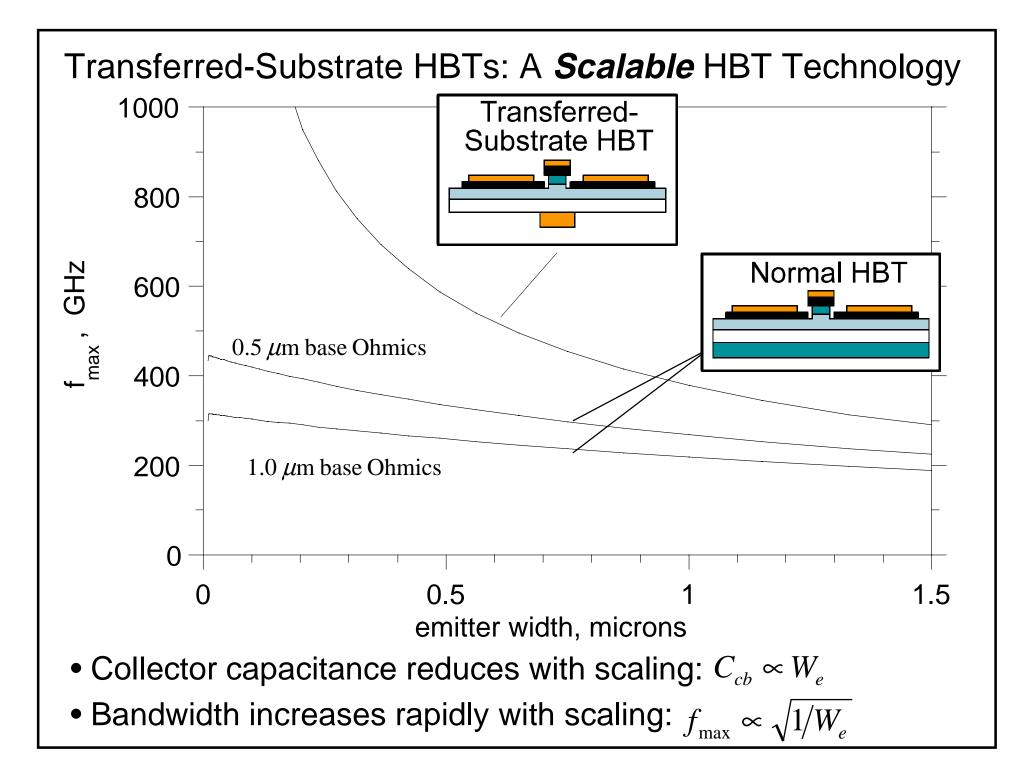

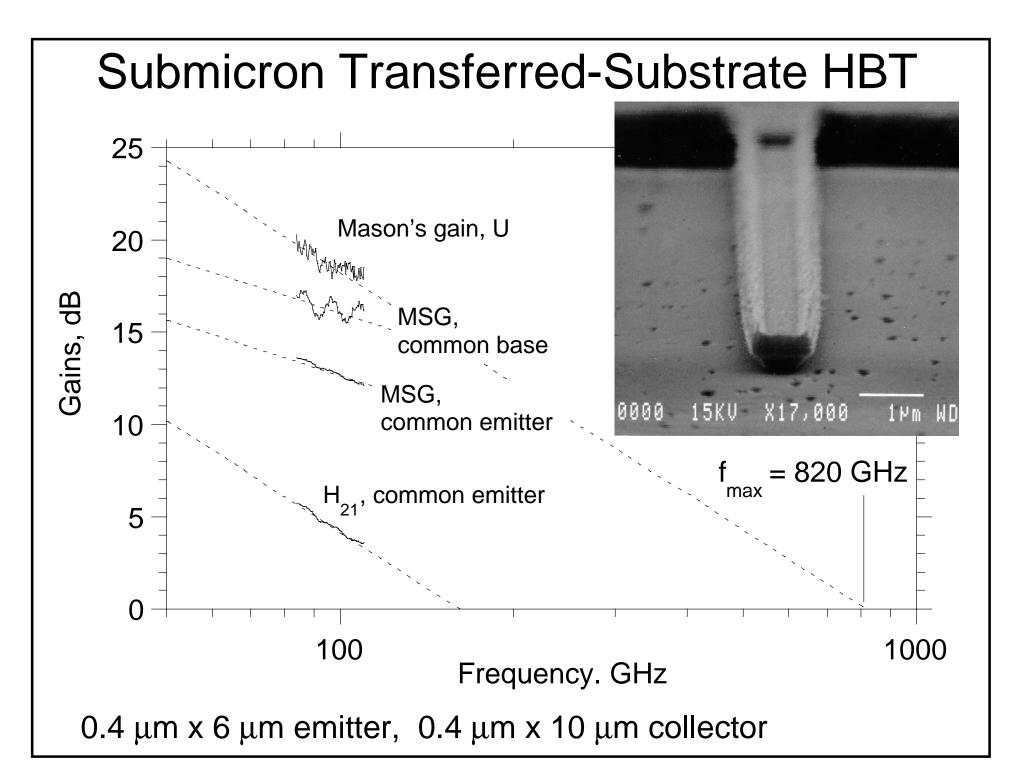

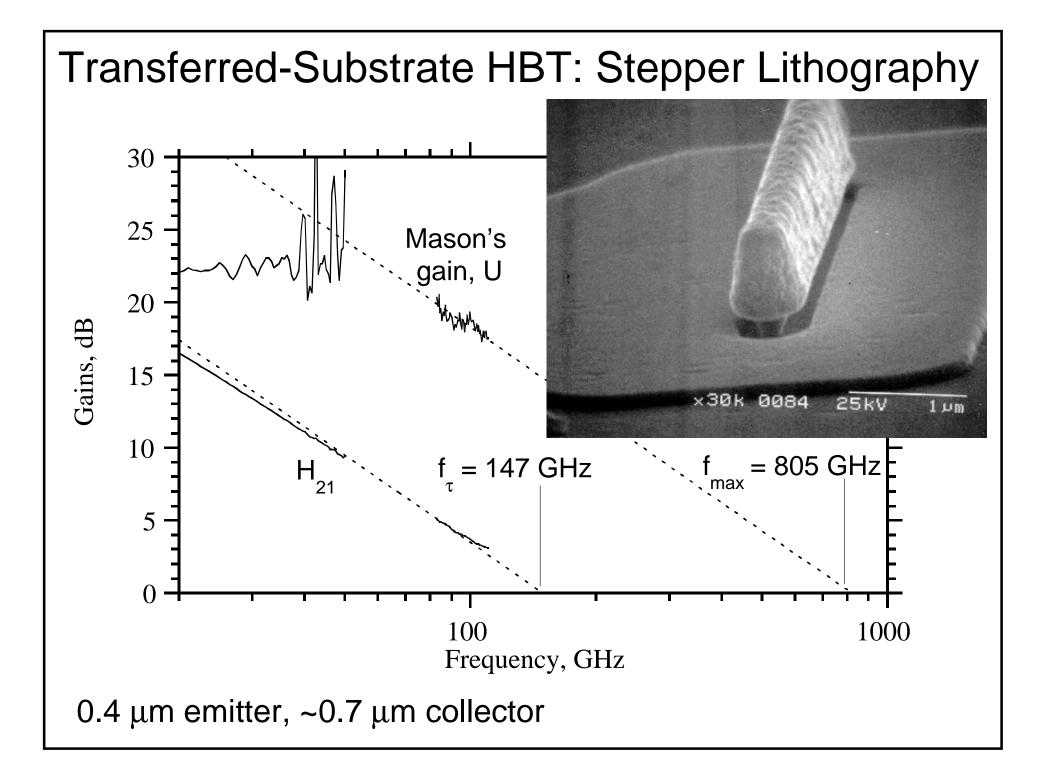

# transferredsubstrate HBTs

## Fmax in Transferred-Substrate HBTs

$$R_{bb} = \frac{1}{2L} \rho_{contact,horizontal} + \frac{\rho_{sheet}}{12L} W$$

$$C_{cb} = \frac{\varepsilon L}{T_c} W$$

$R_{bb}C_{cb}$  reduces rapidly with deep submicron scaling Component due to contacts scales as  $W^1$ Base spreading component

scales as  $W^2$

*F*<sub>max</sub> *increases rapidly with deep submicron scaling*

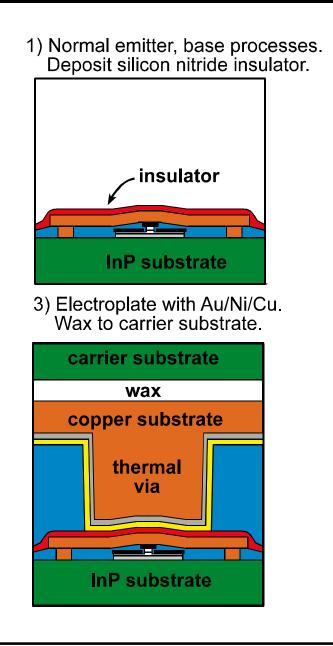

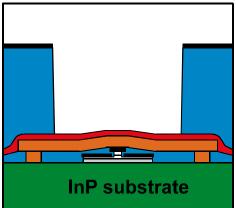

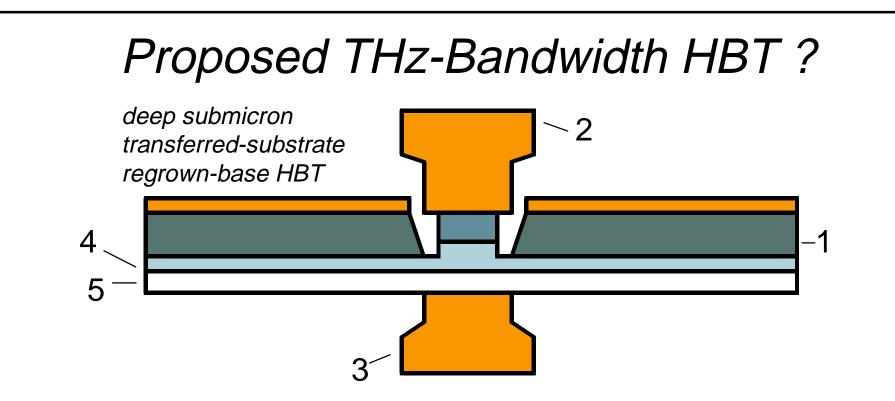

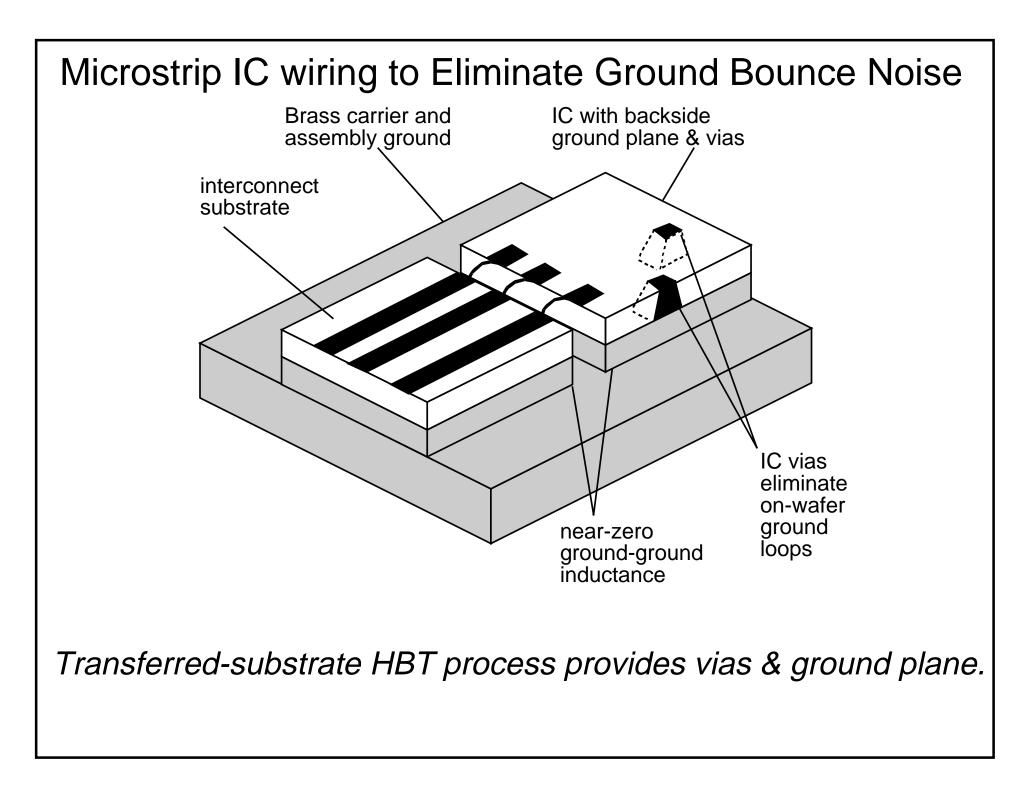

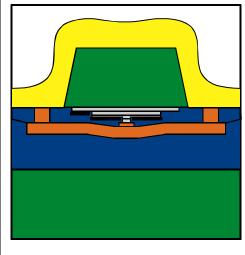

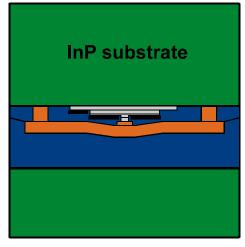

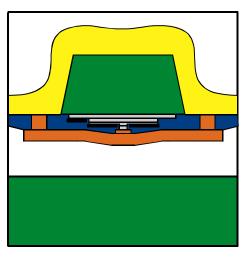

# **Transferred Substrate HBT Process**

#### Objectives:

- 1000 GHz transistor bandwidth

- Thermal management for high power density

- Low wiring & packaging parasitics at 100+ GHz

#### Approach:

- BCB process: standard IC materials

- Metal substrate, thermal vias

- Microstrip wiring: ground vias backside ground plane εr=2.7: low capacitance

2) Coat with BCB polymer. Etch vias.

4) Invert wafer. Remove InP substrate. Deposit collector. Demount from wax.

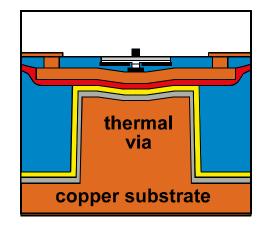

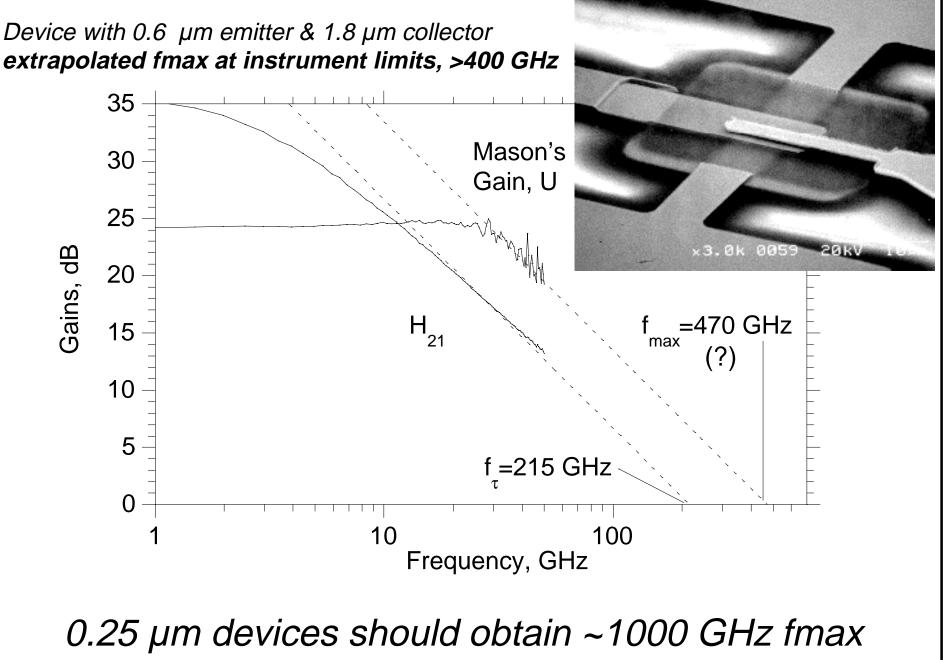

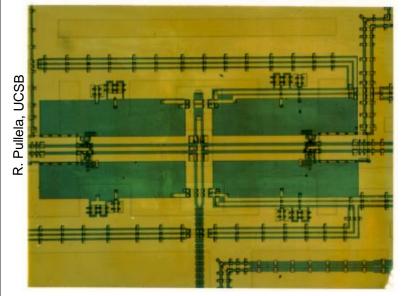

## Transfer of Entire 2" HBT MMIC Wafer

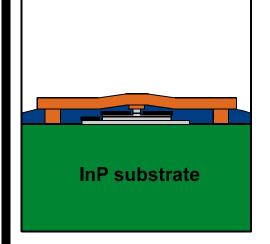

#### Transferred-Substrate Heterojunction Bipolar Transistor

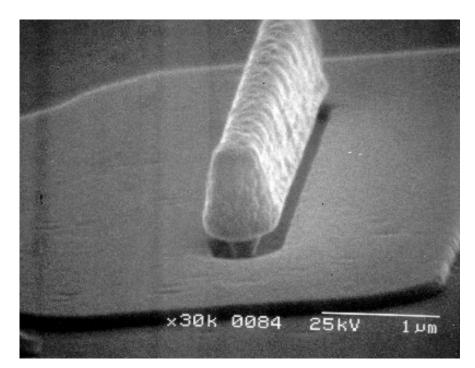

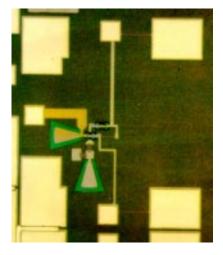

# SEM Photomicrographs of Deep-submicron HBTs 0.15 µm emitter ×50k 0052 22kV 1µm 15KV X17,000 0000 18m WD 0.15 µm emitter base junction $0.4 \ \mu m$ collector

regrown P+++ InGaAs extrinsic base --> ultra-low-resistance

0.05 µm wide emitter --> ultra low base spreading resistance

0.05 µm wide collector --> ultra low collector capacitance

100 Å, carbon-doped graded base --> 0.05 ps transit time

1kÅ thick InP collector --> 0.1 ps transit time.

**Projected Performance:**

Transistor with 500 GHz ft, 1500 GHz fmax

The wiring environment for 100 GHz ICs

# Why is Improved Wiring Essential?

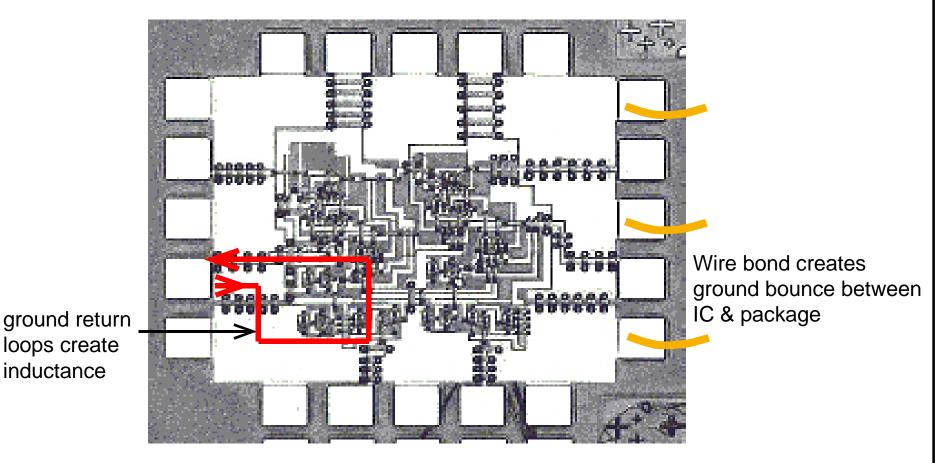

30 GHz M/S D-FF in UCSB - mesa HBT technology

Ground loops & wire bonds: degrade circuit & packaged IC performance

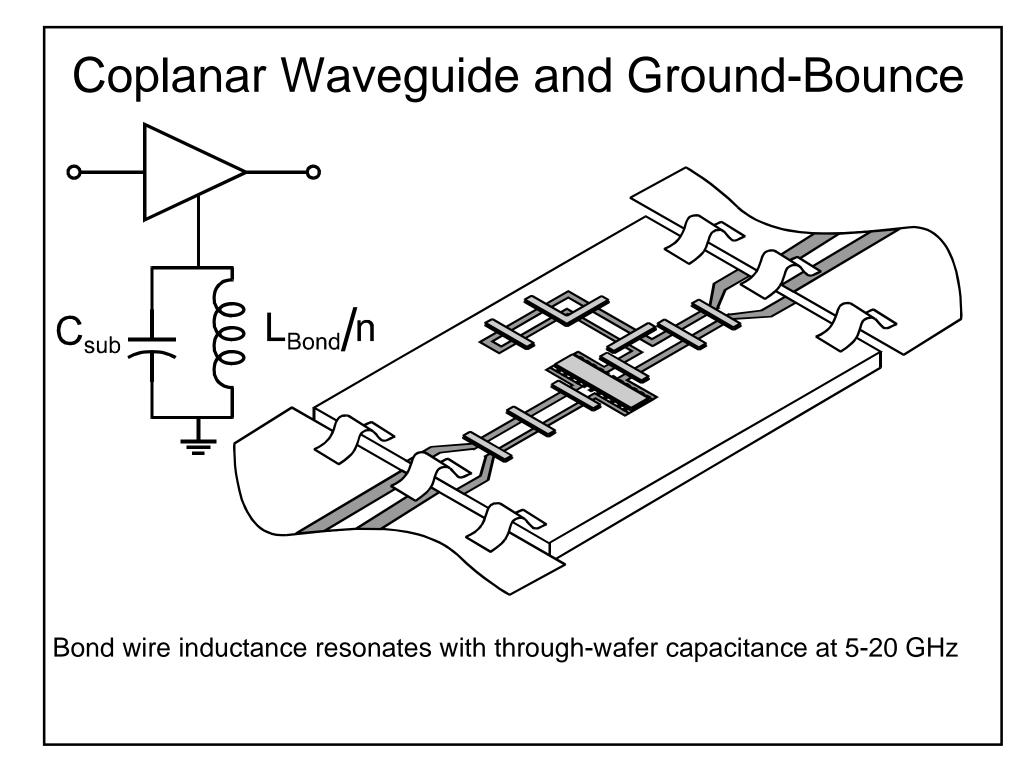

#### > 100 GHz CPW ICs: severe crosstalk & ground bounce

#### 4-channel 100 Gb/s diode-based DMUX

#### active probes for 70-220 GHz network analysis

1-180 GHz HEMT amplifier (with HRL)

B. Agarwal UCSB, M. Matloubian, HRL

O. Wohlgemuth: Fraunhofer / UCSB

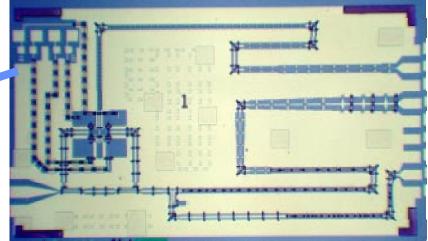

### 70-220 GHz network analyzer chip for active probe

O. Wohlgemuth: Fraunhofer / UCSB

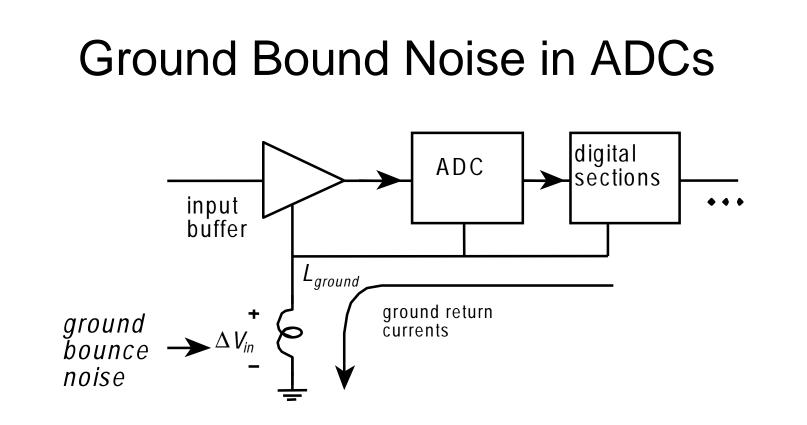

Ground bounce noise must be ~100 dB below full-scale input Differential input will partly suppress ground noise coupling ~ 30 to 40 dB common-mode rejection feasible CMRR insufficient to obtain 100 dB SNR

Eliminate ground bounce noise by good IC grounding

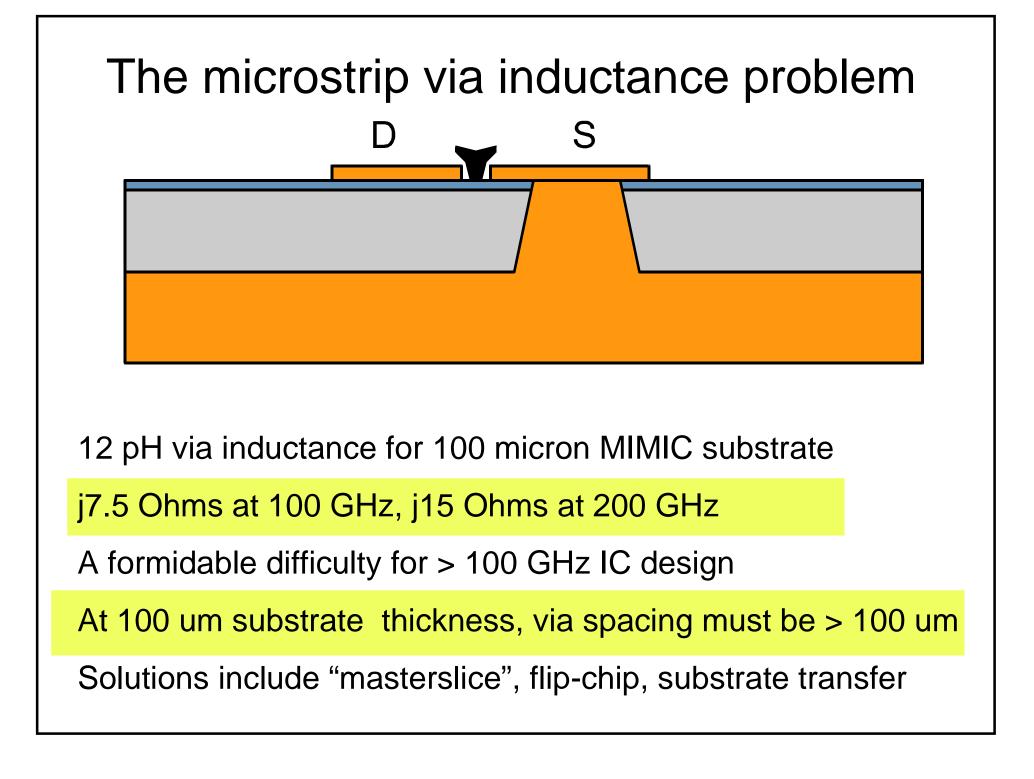

# Standard MMIC Microstrip / Via Process

#### **Objectives:**

ground plane microstrip wiring low via inductance avoid substrate modes

#### Approach: the industry standard

frontside processing wax mounting wafer lapping backside metal wafer release

#### Limitations: for 180 GHz must lap to 35 μm

1) Process complete HBT's passives, interconnect.

3) Back-thin InP, etch and plate vias.

2) Mount HBT wafer to carrier wafer with wax.

4) Peel thinned wafer off carrier.

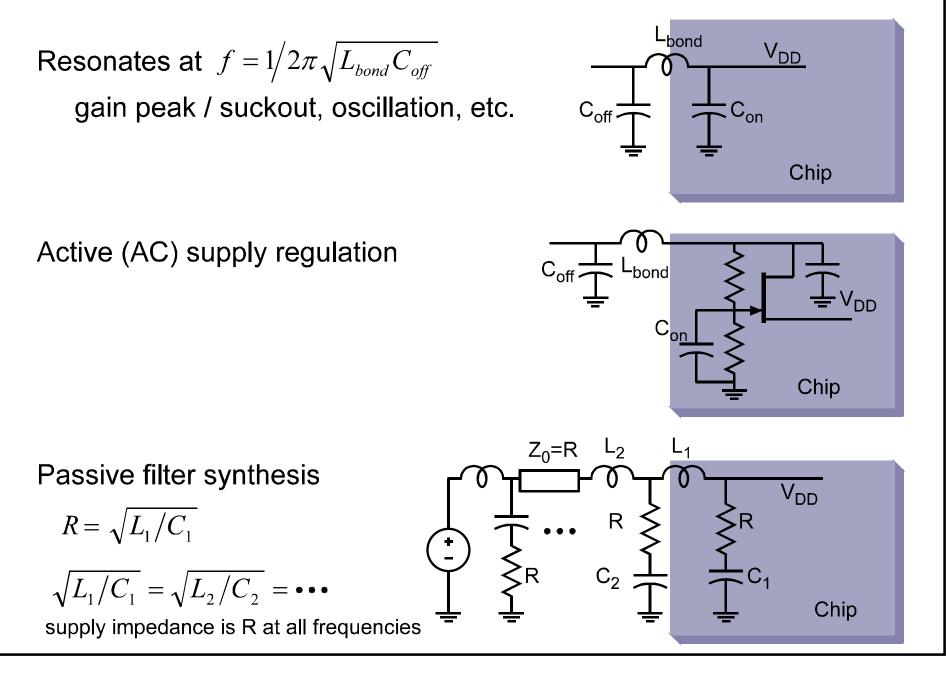

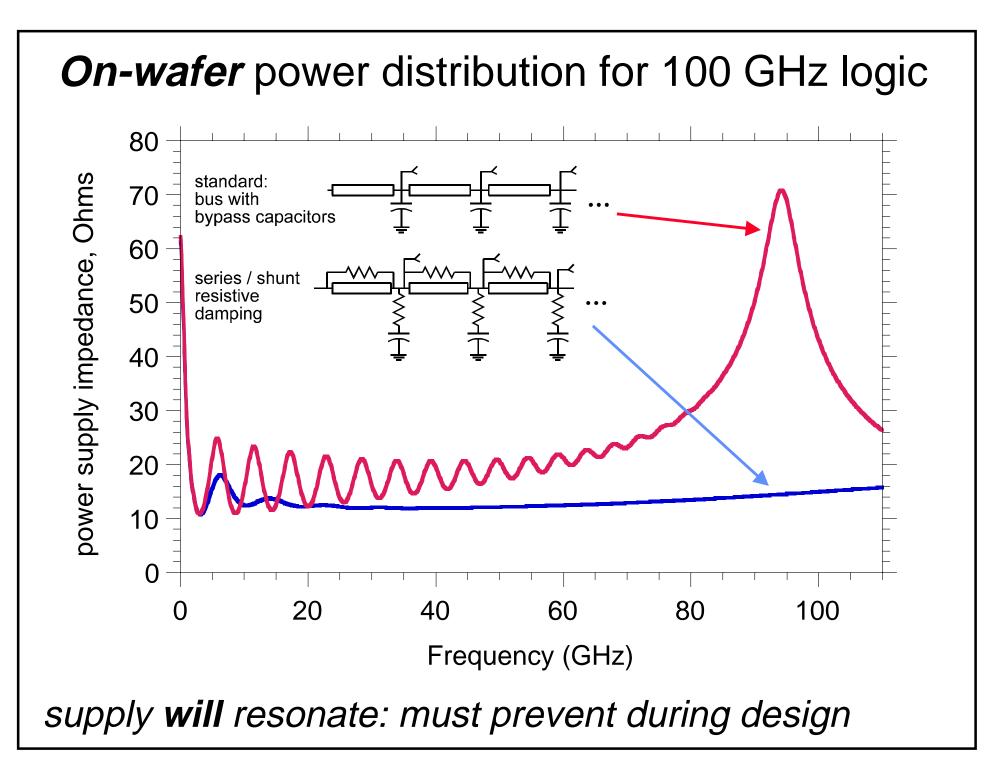

### **Power Supply Resonance**

### Standard cell showing power busses

### Deep submicron HBT logic: *low power ?*

Device sized for 100 Ω load: (200 mV ECL logic swing) 0.15 μm x 6 μm emitter peak speed at 2 mA bias

Shorter stripe length device: 0.15 μm x 0.5 μm emitter *peak speed at 150 μA bias*

Small device is low-power but cannot drive 100  $\Omega$  line. drives line with mismatched impedance: capacitance lower power at higher (wiring-limited) delay

fast low-power logic requires low-voltage-swing-logic

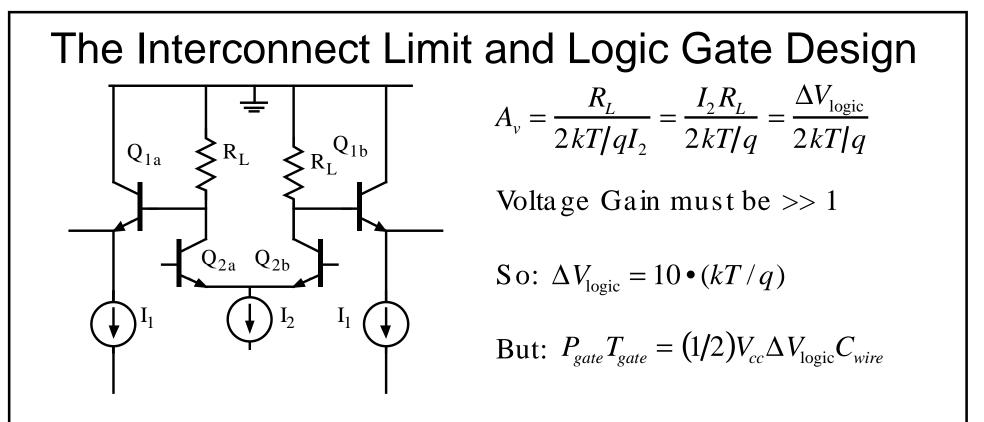

# Power-delay product in interconnect limit $P_{gate} T_{prop} = (1/2) C_{wire} V_{cc} \Delta V_{logic}$ bipolar logic (static power) $P_{gate} / f_{clock} = (1/2)C_{wire}V_{cc}\Delta V_{logic}$ CMOS logic (dynamic power) $(T_{prop} f_{clock})^{-1} \sim$ number gates between latches For fast, low-power logic: reduce $V_{cc}\Delta V_{logic}$

$P_{gate} T_{gate} = (1/2)(1.5 \text{ Volt})(10 \bullet kT/q)C_{wire}$

(power•delay) is constrained by interconnects

a fast transistor doesn't result in a fast IC

conclusion: a better circuit design is needed

Similar derivation for CMOS (Meindl, Proc IEEE, 1995)

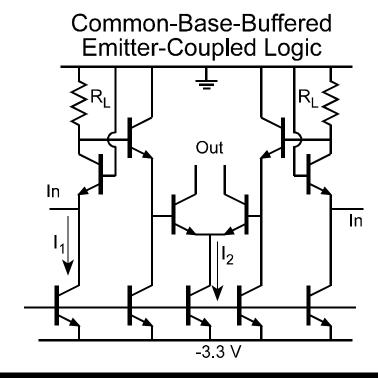

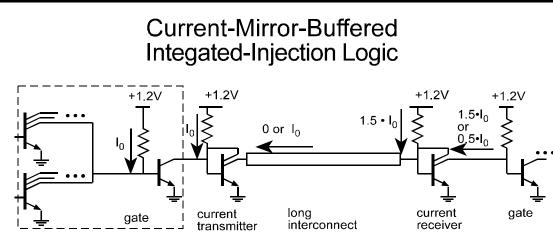

## Low-Voltage-Swing Logic Gates

microwave DDS IC effort: 2000 HBTs @ 50-100 GHz clock dissipation is severe issue

Solution (?): small HBTs + low-voltage logic

Principle: low-impedance input current buffer

Challenge:

not increasing transistor count

#### **Common Feature:**

$$\Delta V_{\text{logic}} = \frac{kT}{q} \ln \left( 1 + \frac{I_{\text{switched}}}{I_{\text{bias}}} \right)$$

### Power Density in 100 GHz logic

Transistors tightly packed to minimize wire delays

10<sup>5</sup> W/cm<sup>2</sup> HBT junction power density.

~10<sup>3</sup> W/cm<sup>2</sup> power density on-chip

--> 75 C temperature rise in 500 µm substrate.

Solutions: thin substrate to < 100  $\mu$ m replace semiconductor with metal

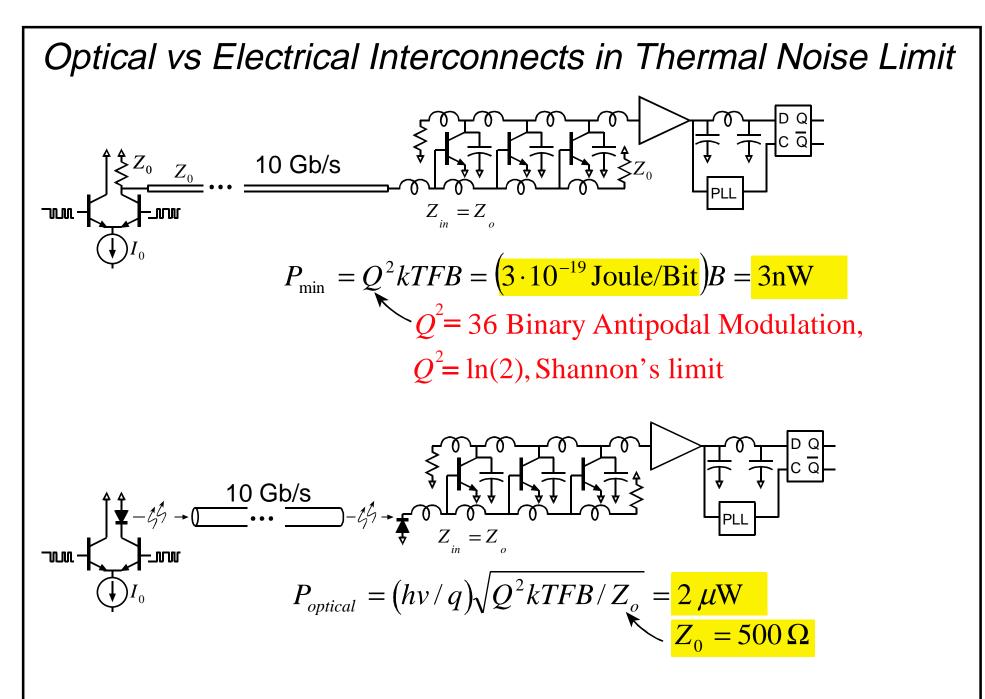

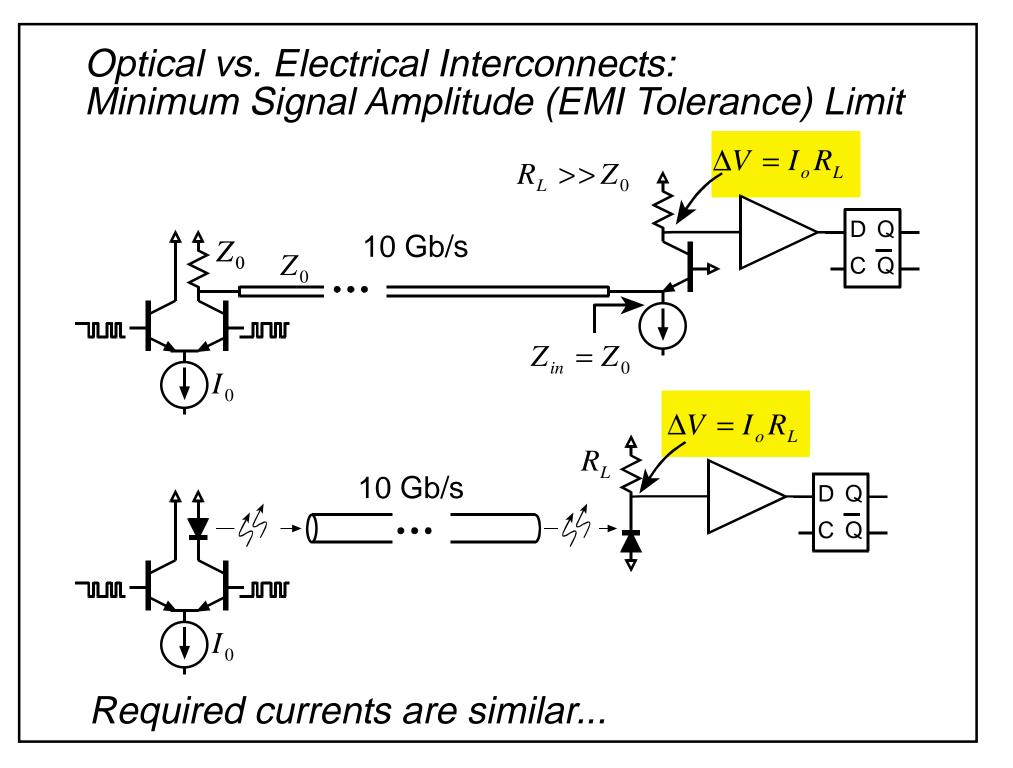

Optical receivers are much less sensitive (square law!)

### So why use optical interconnects ?

Optical fibers are cheap

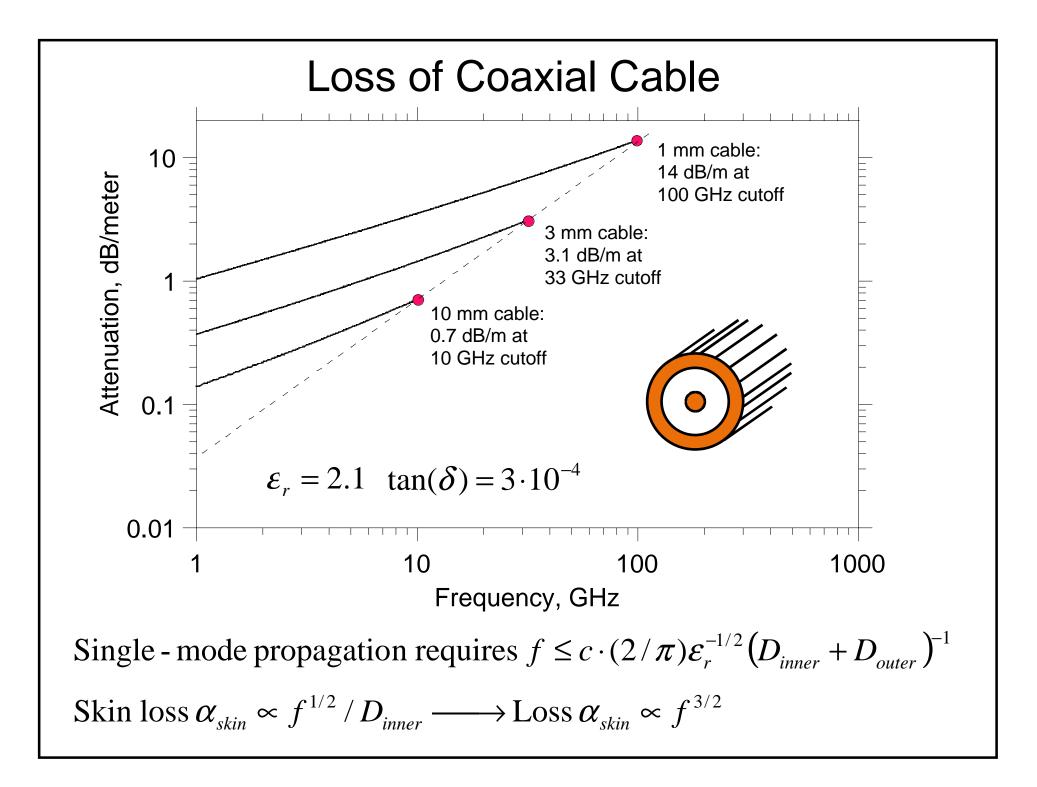

microwave cables, connectors, are expensive but lasers, modulators, detectors must be made cheap

Optical fibers have very low loss microwave cables have high skin effect losses but lasers, modulators have coupling loss

Optical fibers are compact thin electrical conductors have very high losses multi-pin packages must use thin, lossy, conductors

Fiber optics is advantageous because optical fibers have very low attenuation

circuit results: transferredsubstrate technology

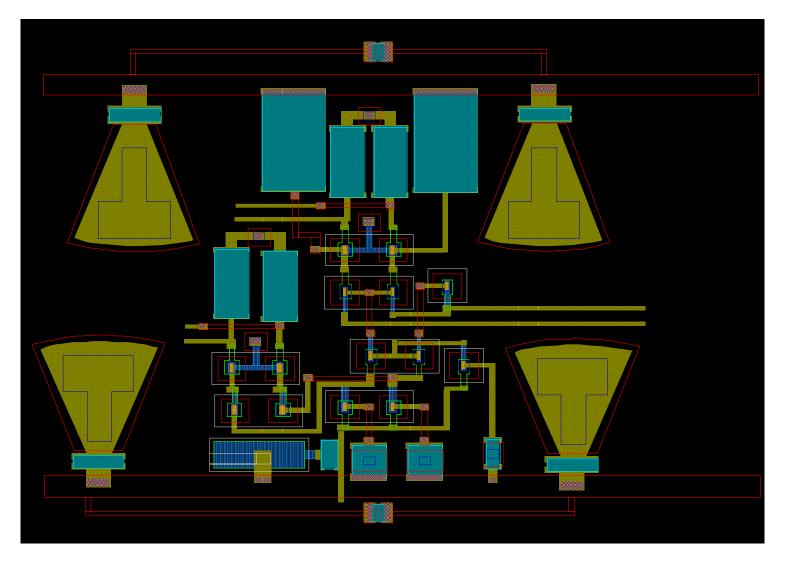

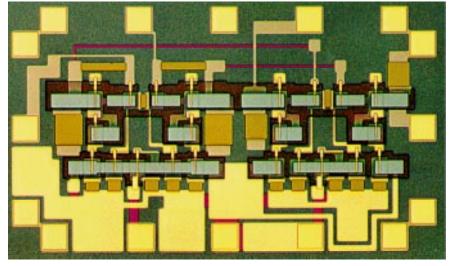

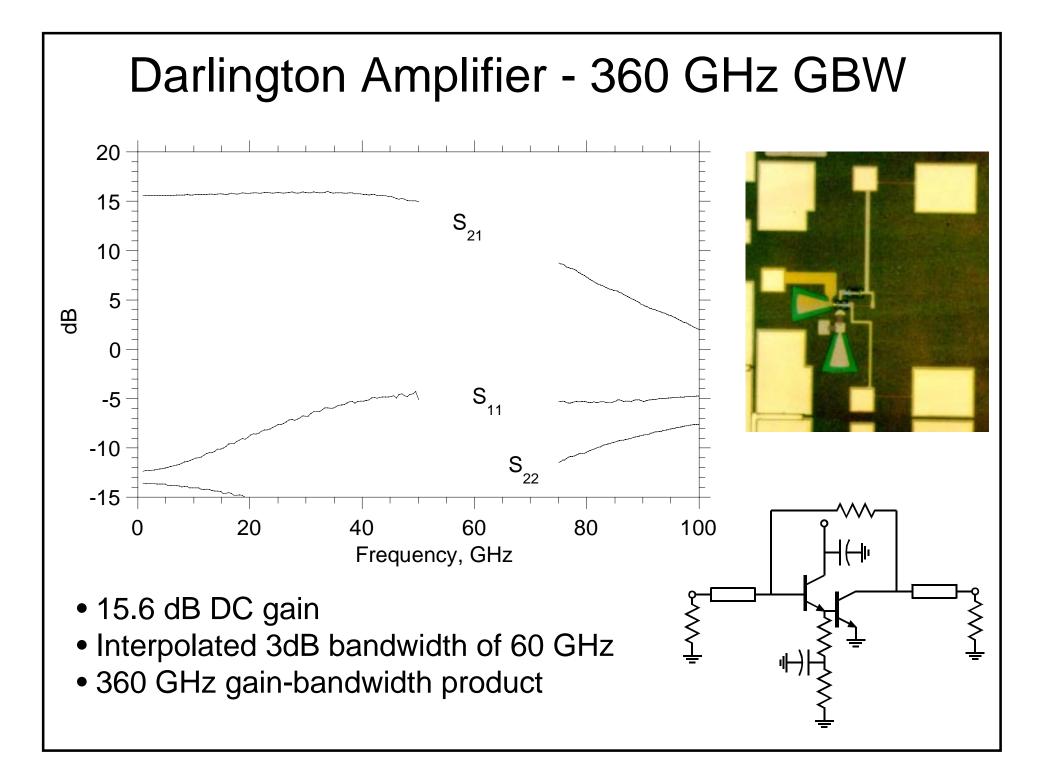

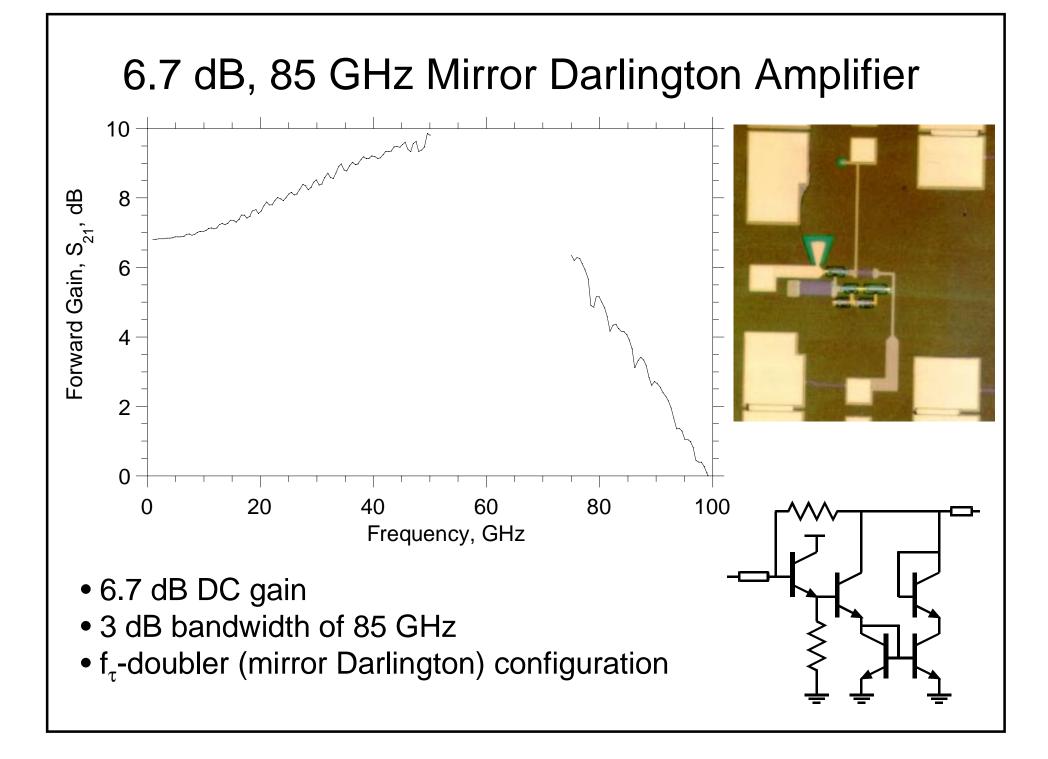

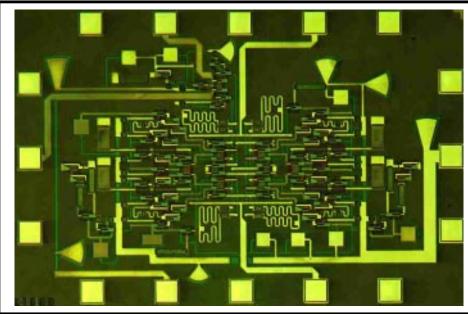

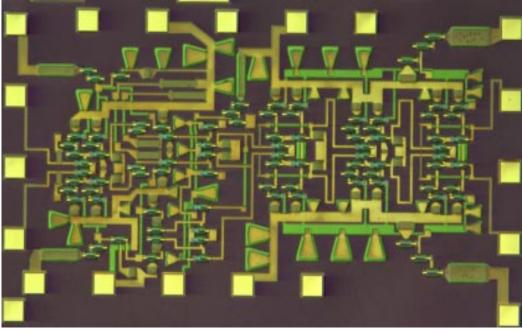

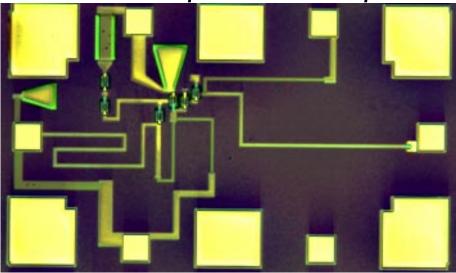

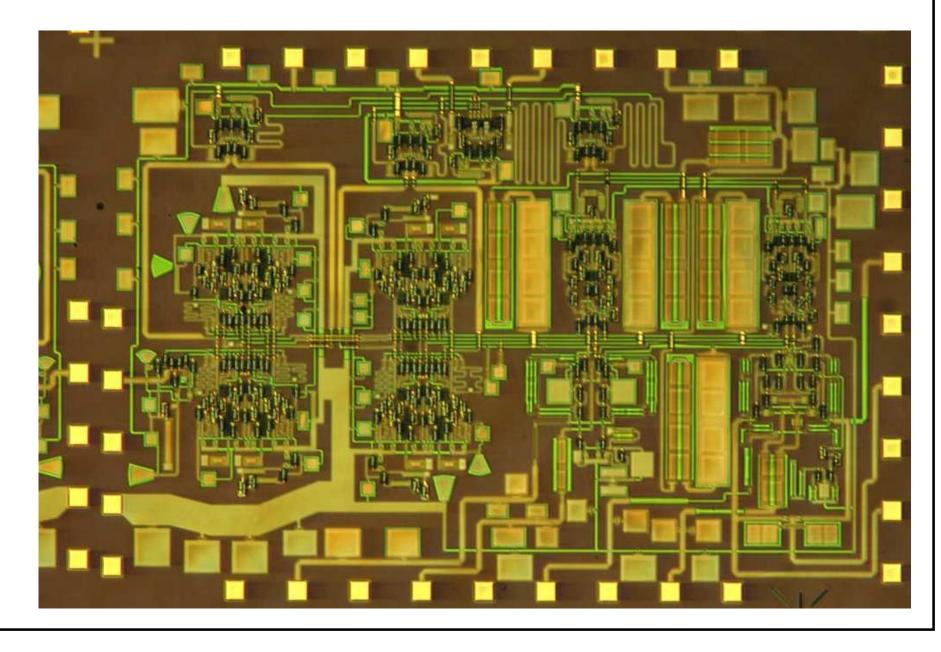

### Transferred-Substrate HBT Integrated Circuits

#### 11 dB, 50+ GHz AGC / limiting amplifier

7 dB, 5-80 GHz distributed amplifier

#### 16 dB, DC-60 GHz amplifier

#### 6.7 dB, DC-85 GHz amplifier

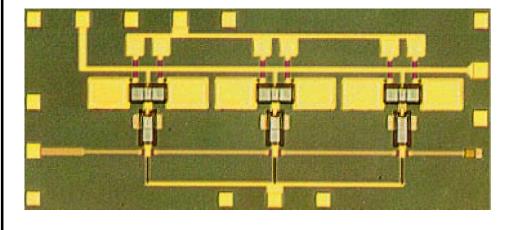

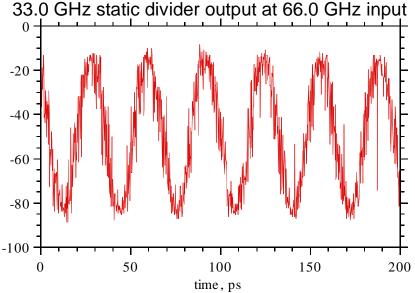

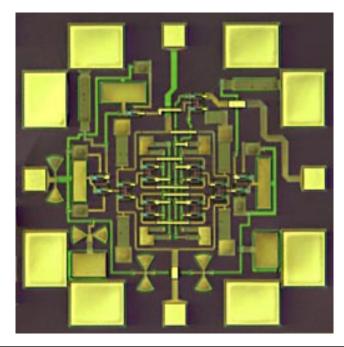

### > 66 GHz HBT master-slave flip-flop

Objectives: 100 + GHz logic

Approach: transferred-substrate HBTs efficient circuit design

Simulations: 95 GHz clock rate in SPICE

#### **Measurements:**

operation to 66 GHz limit of test setup now building 75-110 GHz test setup

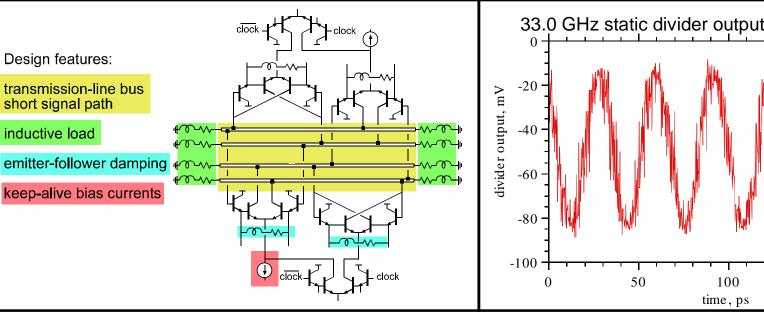

# > 66 GHz HBT master-slave flip-flop clock clock Design features: transmission-line bus short signal path inductive load emitter-follower damping keep-alive bias currents clock clock

# Fiber Optic ICs

not yet tested (design 40 Gb/s)

### AGC / limiting amplifier

### PIN / transimpedance amplifier

### CML decision circuit

### Delta-Sigma ADC (300 HBTs)

## Fast ICs for fast interconnects Fast ICs needing fast interconnects

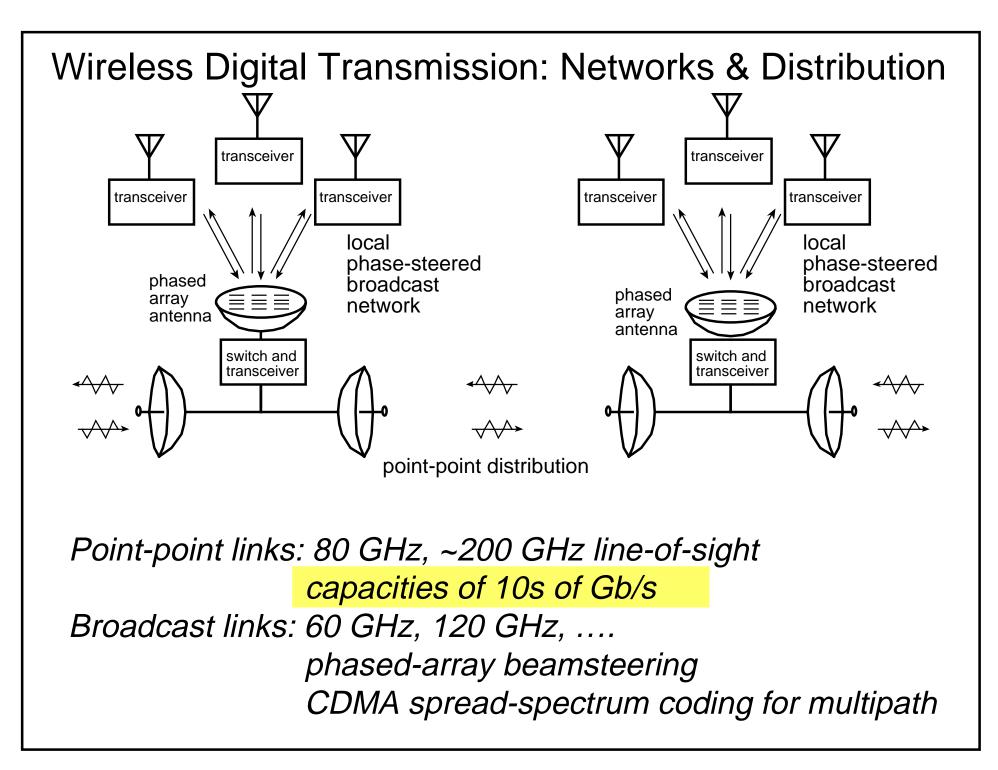

ICs for GHz communications:

Optical fiber transmission to, beyond 40 Gb/s with electronic data switching millimeter-wave (60/90/180 GHz) wireless networks at mm-wave, bandwidth is cheap & plentiful ...but the hardware must become cheap ADCs, DACs for digital processing of RF signals

Challenges for fast ICs

Fast transistors: scaling is key Wiring environment: signal, ground and power integrity Interconnect-limited power-delay products Managing high dissipated power densities