## 0.37 mS/µm In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET with 5 nm channel and Self-aligned Epitaxial Raised Source/Drain

Uttam Singisetti<sup>1\*</sup>, Mark A. Wistey<sup>1,2</sup>, Greg J. Burek<sup>1</sup>, Ashish K. Baraskar<sup>1</sup>, Joël Cagnon<sup>2</sup>, Brian J. Thibeault<sup>1</sup>, Susanne Stemmer<sup>2</sup>, Arthur C. Gossard<sup>1, 2</sup> and Mark J.W. Rodwell<sup>1</sup>

<sup>1.2</sup>ECE and Materials Departments, University of California, Santa Barbara, 93106, CA, USA Eunji Kim, Byungha Shin, Paul C. McIntyre

Materials Science and Engineering Department, Stanford University, Stanford, 94305, CA, USA Yong-Ju Lee

Intel Corporation, Santa Clara, 95054, CA, USA \*Phone: (805) 893-3273, Fax: (805) 893-3262, Email:uttam@ece.ucsb.edu

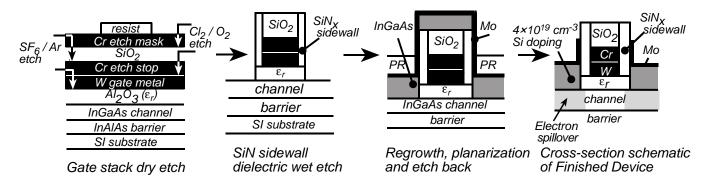

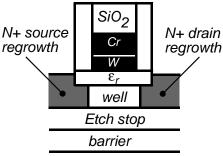

InGaAs has been extensively studied as a potential channel material for sub-22nm gate length VLSI MOSFETs because of its low electron effective mass  $(m^*)$  hence high electron velocity (v). At sub-22 nm gate lengths, a maximum 1 nm EOT dielectric and 5 nm thick channel with strong vertical confinement are required for high subthreshold slope and acceptably low drain induced barrier lowering (DIBL) [1,2]. Most reported InGaAs MOSFETs [3, 4] have  $\geq$  10 nm channel thickness. The source/drain (S/D) junctions must be very shallow (~5nm) with abrupt vertical and lateral profiles, yet extremely low (~ $20\Omega$ –µm) source access resistance and consequently very low (~0.3  $\Omega - \mu m^2$ ) contact and (~500 $\Omega$ ) sheet resistivities are required to minimize degradation of the drive current  $(I_d)$  and transconductance  $g_m$  [1]. Such parameters are difficult to achieve in InGaAs by ion implantation of the N+  $\hat{S}/\hat{D}$ , particularly if an InAlAs bottom confinement layer is used. S/D contacts must be self-aligned to the gate, yet there is no known equivalent of self-aligned silicides in III-V materials. Addressing these requirements, we had reported [5, 6] InGaAs MOSFETs with self-aligned S/D access regions and self-aligned metal contacts formed by MBE regrowth and *in-situ* metal deposition, though these showed low 0.02 mS/µm transconductance. Here we report greatly improved devices with 0.37 mS/ $\mu$ m transconductance at 0.8  $\mu$ m L<sub>g</sub>. Fig. 1 shows the process flow and device schematic cross-section. The device has self-aligned N+ InGaAs

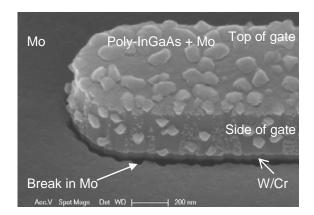

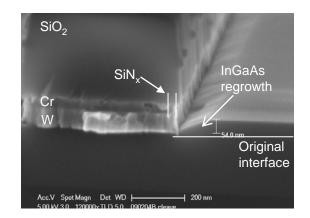

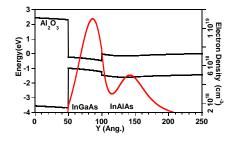

S/D regions formed by MBE regrowth, and self-aligned refractory Mo S/D contacts. *In-situ* Mo contacts to regrown InGaAs have shown very low 2.5  $\Omega$ -µm contact resistivities [7]. The 5 nm In<sub>0.53</sub>Ga<sub>0.47</sub>As channel and an InAlAs bottom barrier were grown by molecular beam epitaxy. To compensate for any surface/interface effects, the InAlAs bottom barrier was pulse doped with Si (Fig. 4). The wafer was capped with arsenic before removal from the MBE chamber. The cap was desorbed in-situ in an atomic layer deposition (ALD) chamber at 480 °C, and 4.7 nm of Al<sub>2</sub>O<sub>3</sub> (~ 2.0 nm EOT) deposited. W(50nm)/Cr(50nm)/SiO<sub>2</sub>(350nm) gates with  $L_g=0.3\mu$ m-10 $\mu$ m were defined in an alternating dry etch scheme (Fig. 1) minimizing etch damage to the thin channel [5]. A 20 nm SiN<sub>x</sub> sidewall was formed by a low power anisotropic RIE etch. The Al<sub>2</sub>O<sub>3</sub> dielectric was then selectively wet etched in dilute KOH, stopping on the InGaAs channel. The wafer was then cleaned by exposure to UV-ozone, followed by a 1 minute dilute HCl treatment and a DI rinse. Following cleaning, the wafer was immediately loaded into the MBE chamber and cleaned with atomic H. A (4×2) surface reconstruction was seen in RHEED before regrowth, indicating an epi-ready surface. 50 nm of  $4\times10^{19}$  Si doped  $n^{++}$  InGaAs was grown at 540 °C by migration enhanced epitaxy. The wafer was then transferred under UHV to an electron beam evaporator and 20 nm of Mo was deposited to form S/D contacts. Because the Mo is also deposited on the gate top surface, the source and drain are short-circuited. The wafer was therefore planarized with photoresist and the Mo on the gate removed with a height-selective etch [8]. S/D pads were then deposited, and devices mesa-isolated. To contact the gates, the silicon dioxide on top of the gate pads was removed by etching in buffered HF.

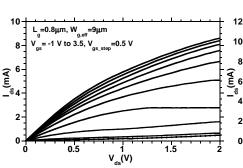

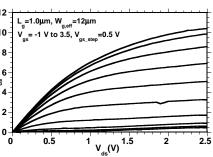

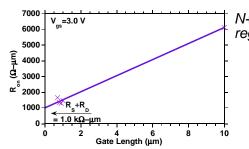

The cross-section SEM (Fig 5.) shows a slope in the regrowth surface next to gate, but no gap is observed between the N+ regrown material and the gate edge. The regrowth is quasi-selective, i.e. material is deposited on the gate top surface, but there is little growth on the gate sidewalls. The DC characteristics of a 0.8  $\mu$ m L<sub>g</sub> FET (Figs. 5,6) show a maximum 0.95 mA/ $\mu$ m I<sub>d</sub> at V<sub>gs</sub>=3.5 V and V<sub>ds</sub>=2.0V. The maximum g<sub>m</sub> is 0.37 mS/ $\mu$ m at V<sub>gs</sub>=0.5V. We believe the gate current (Fig. 7) is dominated by the leakage through the SiN<sub>x</sub> sidewalls. From measurements of zero-bias on-resistance (Fig. 8), a 0.50 k $\Omega$ -µm source resistance is determined. TLMs patterns on the regrown material located far from MOSFET showed 28  $\Omega/\Box$  sheet resistance and 12  $\Omega$ -µm Mo/InGaAs (lateral) contact resistance. The large discrepancy between the source resistance observed in the FET and lateral access resistance observed in TLM patterns may indicate that the regrown InGaAs close to the gate has higher resistivity than in the far field. MBE is a line-of-sight deposition technique, hence growth adjacent to the gate may be disturbed by shadowing. Possible causes of high source resistance include lack of Si doping next to gate, lattice mismatched growth next to gate causing dislocations which deplete electrons, or high defect density at the regrowth interface. Experiments to evaluate the electrical properties of regrowth next to gate are in progress. Any defects induced at Al<sub>2</sub>O<sub>3</sub>/InGaAs interface during regrowth will deplete electrons in the channel under the sidewall. This will also increase the source resistance. A recessed S/D regrowth FET (Fig. 9) where the  $n^{++}$  regrowth reaches below sidewalls can compensate the defects in the channel under the sidewall and thereby reduce the source resistance.

This work was supported by the SRC Non-Classical CMOS Research Program. A portion of this work was performed in the UCSB nanofabrication facility, part of the NSF funded NNIN network.

- 5] U.Singisetti et al, physica status solidi (c), In Press.

- 6] U.Singisetti et al, 21st International Conference on Indium Phosphide and Related Materials, 2009

<sup>1]</sup> M.J.W Rodwell et al, 20th International Conference on Indium Phosphide and Related Materials, 2008., pp.1-6, 25-29 May 2008.

<sup>2]</sup> M. Fischetti et al, IEEE International Electron Devices Meeting, 2007. IEDM 2007., pp.109-112, 10-12 Dec.

<sup>3]</sup> D.A.J. Moran et al, 37th European Solid State Device Research Conference, 2007. ESSDERC 2007., pp.466-469, 11-13 Sept. 2007.

<sup>4]</sup> Y.Xuan et al, IEEE International Electron Devices Meeting, 2008. IEDM 2008., pp.1-4, 15-17 Dec. 2008

<sup>7]</sup> M.Wistey et al, Electronc Materals Conference 2008, pp Z4, Jun 2008

<sup>8]</sup> G.Burek et al, Journal of Crystal Growth, In Press.

Fig. 1: Schematic of the gate process, regrowth and planarization

Fig. 2:Oblique view SEM of MOSFET after regrowth and Mo depostion

Fig. 4: Band diagram of the MOSFET

Fig. 5: Output characteristics of  $L_g$ =0.8  $\mu$ m and  $W_g$ =9  $\mu$ m device

Fig. 6: Output characteristics of  $L_g=1.0$  µm and  $W_g=12$  µm device

$(10^{3} + 10^{4})^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} + 10^{10^{2}} +$

Fig. 7: Measured gate to source leakage

Fig. 8:FET S/D on resistance at Vds=0

Fig. 9: X-section schematic of recess S/D regrowth FET