## Process Technologies For Sub-100-nm InP HBTs & InGaAs MOSFETs

M. J.W. Rodwell<sup>a</sup>, M. A. Wistey<sup>a,b</sup>, U. Singisetti<sup>a</sup>, G. J. Burek<sup>a</sup>, E. Kim<sup>c</sup>, B. J. Thibeault<sup>a</sup>, E. Lobisser<sup>a</sup>, V. Jain<sup>a</sup>, A. Baraskar<sup>a</sup>, J. Cagnon<sup>b</sup>, Y.-J. Lee<sup>d</sup>, S. Stemmer<sup>a</sup>, P. C. McIntyre<sup>c</sup>, A. C. Gossard<sup>a</sup>, B. Yu<sup>e</sup>, P. Asbeck<sup>e</sup>, Y. Taur<sup>e</sup>

<sup>a</sup>U.C. Santa Barbara, <sup>b</sup>Univ. of Notre Dame, <sup>c</sup>Stanford University, <sup>d</sup>Intel, <sup>e</sup>U.C. San Diego.

III-V transistors of ~10 to 100 nm lithographic dimensions are being developed both for THz applications and for use in large-scale digital integrated circuits. Reducing dimensions increases both IC packing density and transistor bandwidth. Increasing bandwidth of an arbitrary circuit by  $\gamma$ :1 requires a  $\gamma$ :1 reduction of transistor capacitances and transit delays while maintaining constant resistances and bias and signal voltages and currents. For bipolar transistors [1], this requires a  $\sim \gamma^1$ :1 reduction in epitaxial dimensions, a  $\gamma^2$ :1 reduction in contact resistivities, and a  $\gamma^2$ :1 reduction in lithographic dimensions. For field-effect transistors [2], such scaling requires again a  $\gamma$ :1 reduction in epitaxial dimensions (dielectric equivalent thickness, wavefunction depth) and a  $\gamma^2$ :1 reduction in contact resistivities, but only requires a  $\gamma^1$ :1 reduction in lithographic dimensions (gate length). Required current densities scale with both transistor types; for HBTs, emitter current density ( $mA/\mu m^2$ ) varies as  $\gamma^2$ , though current per unit emitter stripe length remains fixed, while for FETs, current per until gate width  $(mA/\mu m)$  varies as  $\gamma^1$ , but current per unit source and drain Ohmic contact area  $(mA/\mu m^2)$  varies as  $\gamma^2$ . To build multi-THz HBTs and HEMTs, and to build sub-22-nm InGaAs MOSFETs, we must fabricate self-aligned contacts and junctions of 10-100 nm dimensions. We must develop Ohmic contacts of  $\sim 1 \Omega - \mu \text{m}^2$  contact resistivity; this resistivity must not increase when operating ~25-250 mA/µm<sup>2</sup> current density, nor can the contact metals diffuse under such high current and thermal stress through device junctions only ~5-10 nm below the surface. We here describe our efforts to develop such fabrication processes for both InP-based FETs and HBTs.

First, consider in more detail FET scaling in the constant-voltage, constant-velocity limit. Vertical dimensions  $(T_{well}, T_{eq})$  must be reduced in proportion to gate length to maintain a constant  $g_m/G_{ds}$  ratio and to maintain a constant ratio of the parallel-plate  $(C_{g-ch})$  to the fringing  $(C_{gs,f}, C_{gd})$  components of the device input capacitance; in the absence of vertical scaling, drain-induced barrier lowering increases, output conductance degrades, and the input capacitance becomes dominated by gate fringing fields. As a consequence of vertical scaling, on-state current density  $I_d/W_g$  increases as  $\gamma^1$ . It is well understood that difficulties in reducing  $T_{eq}$  (gate leakage by tunneling) and in increasing  $C_{DoS}$  [3] will impede constant-voltage FET scaling; note also that  $T_{im}$  must scale as  $\gamma^{-1}$ , requiring thinner wells or stronger vertical fields,  $(R_s + R_d)/W_g$  must scale as  $\gamma^{-1}$ , requiring both lower  $\rho_c$  and increased carrier concentrations in access regions, and on-state inversion charge density  $n_s$  must scale as  $\gamma^{-1}$ , requiring increased gate barrier height. Further, device self-heating scales as  $\gamma^{-1}$ , a serious concern for normally-on circuits such as sub-mm-wave amplifiers. These scaling considerations apply to equally to InGaAs FETs in development for VLSI and for sub-mm-wave/THz applications; device design goals include low access resistance, high drive current density, thin wells, high sheet carrier density, and gate barriers that are both thin and high in energy. Future sub-mm-wave FETs may well use high-K gate dielectrics to permit small  $T_{eq}$  and large  $n_s$ ; note that moderately high interface charge density  $D_u$  will not impair device gain at frequencies well above the inverse of the interface trap lifetimes.

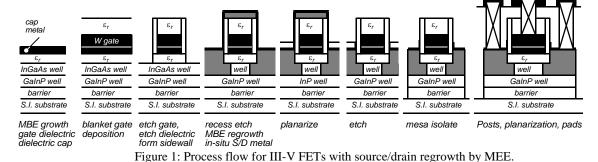

Established III-V HEMT structures do not well address these scaling requirements. We have therefore developed a fully self-aligned InGaAs MOSFET process flow [4] (fig. 1). In this flow, 4.7 nm Al<sub>2</sub>O<sub>3</sub> gate dielectric is deposited by ALD on a 5 nm In<sub>0.53</sub>Ga<sub>0.47</sub>As channel, the gate is formed by blanket W/Cr/SiO<sub>2</sub> deposition and RIE etching, and thin ~25 nm Si<sub>x</sub>N<sub>y</sub> gate sidewalls formed. After etching the Al<sub>2</sub>O<sub>3</sub>, self-aligned S/D InAs N+ regions (50 nm thick,  $8 \times 10^{19}$  cm<sup>-3</sup>, 23  $\Omega$  sheet resistance) are formed by migration enhanced epitaxy, and self-aligned S/D contacts formed by in-situ blanket evaporation of Mo (3.5  $\Omega - \mu$ m<sup>2</sup> contact resistance) and a subsequent height-selective etch [5]. Mesa isolation and back-end metal completes the process. Unlike HEMTs, no gate barrier is present in the S/D regions, the source and drain are fully self-aligned to the gate, and carrier densities in the S/D access regions are high (~1.5×10<sup>13</sup> cm<sup>-2</sup>). Figure 3 shows measured  $I_D$  for a 200-nm- $I_V$  device.

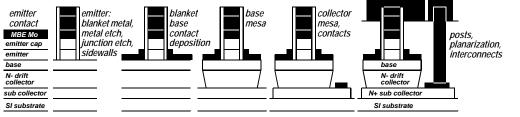

We are developing similar processes to fabricate InP HBTs with 64 nm and 128 nm  $W_e$  (fig. 4). In-situ Mo emitter contacts [6] provide  $1.1\pm0.4~\Omega-\mu\text{m}^2$  contact resistivity. The emitter metal is dry-etched Mo or W to withstand high target current densities. Emitter and base contacts are separated by thin  $\text{Si}_{x}\text{N}_{y}$  sidewalls, and base contacts are sputter-deposited refractory metals.

- 1] M. Rodwell et al, IEEE Proceedings, February 2008.

- 2] M. Wistey et al, Proceedings, Electrochemical Society Annual Meeting, May 2009.

- 3] P. M. Solomon, S. E. Laux, 2001 IEEE IEDM

- 4] U. Singisetti *et al*, Physica Status Solidi (c), Volume 6 Issue 6; M. Rodwell *et al* 2008 IEEE Indium Phosphide and Related Materials Conference; U. Singisetti *et al*, submitted to IEEE EDL; M. Wistey et al, 2009 Electronics Materials Conference.

- 5] G.J. Burek et al, Journal of Crystal Growth Volume 311, Issue 7, 15 March 2009, Pages 1984-1987

- 6] A. Baraskar et al, 2009 Physics and Chemistry of Surfaces and Interfaces Conference (to be published, JVST)

**Table 1:** HBT scaling laws: changes required for  $\gamma$ :1 increased bandwidth in an arbitrary circuit

| parameter                                                | law              | parameter                                             | law                 |

|----------------------------------------------------------|------------------|-------------------------------------------------------|---------------------|

| emitter junction length, $L_{\scriptscriptstyle e}$ (nm) | $\gamma^{\rm o}$ | contact resistivities $\rho_c$ ( $\Omega - \mu m^2$ ) | $\gamma^{-2}$       |

| emitter junction width, $W_{_{e}}$ (nm)                  | $\gamma^{-2}$    | emitter current density ( mA/ $\mu$ m <sup>2</sup> )  | $\gamma^2$          |

| collector junction width (nm)                            | $\gamma^{-2}$    | emitter current density ( mA/μm )                     | γ°                  |

| collector depletion thickness (nm)                       | $\gamma^{-1}$    | temperature rise (one device, K)                      | $\sim \ln(L_e/W_e)$ |

| base thickness (nm)                                      | ~ \chi^{-1/2}    |                                                       | ·                   |

**Table 2:** Constant-voltage / constant-velocity FET scaling laws: changes required for  $\gamma:1$  increased bandwidth in an arbitrary circuit

| $\leftarrow L_{S/D} \longrightarrow$ | $ \longleftarrow L_g \longrightarrow  $ | $L_{S/D} \longrightarrow  $ | $T_{ox} T_{well}$ |

|--------------------------------------|-----------------------------------------|-----------------------------|-------------------|

|                                      | gate                                    |                             | _                 |

| source                               | ネネン                                     | drain                       |                   |

|                                      | 000,000                                 |                             |                   |

|                                      |                                         |                             |                   |

|                                                                  |                                 |                                                                            | . Т                             |

|------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------|---------------------------------|

| parameter                                                        | law                             | parameter                                                                  | law                             |

| gate length $L_{_{\rm g}}$ , source-drain contact lengths        | $\gamma^{-1}$                   | gate-channel capacitance                                                   | $\gamma^{-1}$                   |

| $L_{S/D}$ (nm)                                                   |                                 | $C_{g-ch} = [1/C_{ox} + 1/C_{semi} + 1/C_{DOS}]^{-1}$ (fF)                 |                                 |

| gate width $W_{g}$ (nm)                                          | $\gamma^{-1}$                   | transconductance $g_m \sim C_{g-ch} v_{injection} / L_g \text{ (mS)}$      | $\gamma^{\rm o}$                |

| equivalent oxide thickness                                       | $\gamma^{-1}$                   | gate-source, gate-drain fringing capacitances                              | $\gamma^{-1}$                   |

| $T_{eq} = T_{ox} \varepsilon_{SiO_2} / \varepsilon_{oxide}$ (nm) |                                 | $C_{gs,f} \propto \varepsilon W_g$ , $C_{gd} \propto \varepsilon W_g$ (fF) | '                               |

| dielectric capacitance                                           | $\gamma^{-1}$                   | S/D access resistances $R_s$ , $R_d(\Omega)$                               | $\gamma^{0}$                    |

| $C_{ox} = \varepsilon_{SiO_2} L_g W_g / T_{eq} (fF)$             |                                 | S/D contact resistivity $R_s/W_g$ , $R_d/W_g$ ( $\Omega - \mu m$ )         | $\gamma^{-1}$                   |

| inversion thickness $T_{inv} \sim T_{well} / 2$ (nm)             | $\gamma^{-1}$                   | S/D contact resistivity $\rho_c (\Omega - \mu \text{m}^2)$                 | $\gamma^{-2}$                   |

| semiconductor capacitance                                        | $\gamma^{-1}$                   | drain current $I_d \sim g_m(V_{es} - V_{th})$ (mA)                         | γ°                              |

| $C_{semi} = \varepsilon_{semi} L_g W_g / T_{inv} \text{ (fF)}$   |                                 |                                                                            |                                 |

| DOS capacitance $C_{DOS} = q^2 nm^* / 2\pi\hbar^2$ (fF)          | $\gamma^{-1}$                   | drain current density ( mA/μm )                                            | $\gamma^{\scriptscriptstyle 1}$ |

| electron density $n_s$ (cm <sup>-2</sup> )                       | $\gamma^{\scriptscriptstyle 1}$ | temperature rise (one device, K)                                           | ~ W <sub>g</sub> <sup>-1</sup>  |

top of gate

side of gate

Mo S/D metal with

N+ InAs underneath

Act / SpelMage De WO | 200 mm

100 NV 30 100000 TILD 51 0000000 ME E.000C.00

0.8 L = 200 nm W = 8 µm

0.7- W = 200 nm W = 8 µm

0.5- V = 0.6 V = 0.5 V steps

0.4- V = 0.4- V

Figure 2: Regrown S/D InGaAs FET, oblique view & cross-section.

Figure 3: Common-source characteristics.

Figure 4: Refractory-contact /dry-etched process flow for 128 nm /64 nm InP HBTs.