## III-V FET Channel Designs for High Current Densities and Thin Inversion Layers

Mark Rodwell<sup>1</sup>, W. Frensley<sup>2</sup>, S. Steiger<sup>4</sup>, E. Chagarov<sup>3</sup>, S. Lee<sup>4</sup>, H. Ryu<sup>4</sup>,

Y. Tan<sup>4</sup>, G. Hegde<sup>4</sup>, L Wang<sup>3</sup>, J. Law<sup>1</sup>, T. Boykin<sup>5</sup>, G. Klimek<sup>4</sup>, P. Asbeck<sup>3</sup>, A. Kummel<sup>3</sup>, J. N. Schulman<sup>6</sup>

<sup>1</sup>ECE Department, University of California, Santa Barbara, 93106, USA, <sup>2</sup>University of Texas, Dallas,

University of California, San Diego, <sup>4</sup>Purdue University, <sup>5</sup>University of Alabama, Huntsville, <sup>6</sup>The Aerospace Corporation, El Segundo phone: 805-893-3244, fax 805-893-3262, rodwell@ece.ucsb.edu

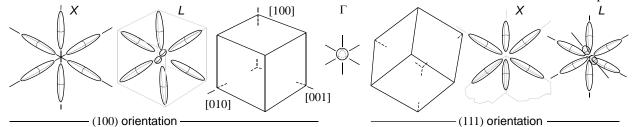

III-V FETs are being developed for potential application in 0.3-3 THz systems and VLSI. To increase bandwidth, we must increase the drive current  $I_d = qn_s v_{inj} W_g$  per unit gate width  $W_g$ , requiring both high sheet carrier concentrations  $n_s$  and high injection velocities  $v_{inj}$ . Present III-V NFETs restrict control region transport to the single isotropic  $\Gamma$  band minimum. As the gate dielectric is thinned,  $I_d$  becomes limited by the effective mass  $m^*$ , and is only increased by using materials with increased  $m^*$  and hence increased transit times. The deep wavefunction also makes  $\Gamma$ -valley transport in low- $m^*$  materials unsuitable for < 22-nm gate length ( $L_g$ ) FETs. Yet, the L-valleys in many III-V materials have very low transverse  $m_i$  and very high longitudinal mass  $m_i$ . L-valley bound state energies depend upon orientation, and the directions of confinement, growth, and transport can be chosen to selectively populate valleys having low mass in the transport direction  $^{3,4}$ . The high perpendicular mass permits placement of multiple quantum wells spaced by a few nm, or population of multiple states of a thicker well spaced by  $\sim$ 10-100 meV. Using combinations of  $\Gamma$  and L valleys,  $n_s$  can be increased,  $m^*$  kept low, and vertical confinement improved, key requirements for <20-nm  $L_g$  III-V FETs.

Consider FET scaling. To increase bandwidth  $\gamma: \mathring{\Gamma}$ , capacitances and transit delays must be reduced  $\gamma: 1$  while maintaining constant voltages, currents, and resistances. In short-  $L_g$  FETs, the gate-source  $C_{gs,f} \propto \varepsilon W_g$  and gate-drain  $C_{gd} \propto \varepsilon W_g$  fringing capacitances are a significant fraction of the total capacitance, and limit  $f_\tau$ .  $C_{gs,f}$  and  $C_{gd}$  are only weakly dependent on lateral geometry, hence the  $(C_{gs,f} + C_{gd})\Delta V/I_d$  delay is reduced  $\gamma:1$  only if  $I_d/W_g$  is increased  $\gamma:1$ .  $I_d$  is determined by the sheet carrier concentration  $n_s = (C_{g-ch}/L_gW_g)(V_{gs}-V_{fh})/q$ , where the gate-channel capacitance  $C_{g-ch} = [1/C_{ox}+1/C_{depth}+1/C_{DOS}]^{-1}$  is the series combination of dielectric  $C_{ox} = \varepsilon_{Sio_2}L_gW_g/T_{eq}$ , wavefunction depth  $C_{depth} = \varepsilon_{semi}L_gW_g/T_{inv}$  ( $T_{inv}$  is the wavefunction mean depth) and density of states  $C_{dos} = q^2 \cdot dn_s/dE_f$  capacitances. In the ballistic case,  $C_{dos} = q^2 g(m_\parallel m_\perp)^{1/2}L_gW_g/2\pi\hbar^2$ , where g is the # of populated valleys, and  $m_\parallel$  and  $m_\perp$  the effective masses parallel and perpendicular to transport; near equilibrium,  $C_{dos}$  is 2:1 larger. Given ballistic transport S and S are reduced S and S

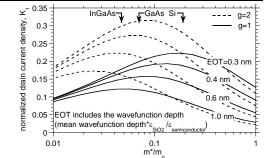

At a given dielectric thickness  $T_{equiv}$ , there is an optimum  $m^*$  maximizing  $I_d$ . We find  $I_d/W_g=J_0\cdot K_1\cdot ((V_{gs}-V_{th})/1\mathrm{V})^{3/2}$ , where  $J_0=(4/3\pi)(2q/m_0)^{1/2}(1\mathrm{V})^{3/2}(q^2m_0/2\pi\hbar^2)=84$  mA/ $\mu$ m and  $K_1=n\cdot (m_\perp/m_o)^{1/2}(1+(C_{doso}/C_{equiv})\cdot g\cdot (m_\perp^{1/2}m_\parallel^{1/2}/m_o))^{-3/2}$  is the normalized current density.  $C_{equiv}=[1/C_{ox}+1/C_{inv}]^{-1}$  where the normalized delay is  $K_2=(m_\parallel/m_0)^{1/2}(1+C_{doso}g(m_\perp m_\parallel)^{1/2}/m_0C_{equiv})^{1/2}$  and  $V_0=(4/3\pi)\cdot (2q\cdot (1\mathrm{Volt})/m_0)^{1/2}=2.5\cdot 10^7$  cm/s. Given one isotropic valley  $(m_\perp=m_\parallel=m^*,\ g=1)$  and 1 nm total equivalent dielectric thickness EOT (i.e.  $C_{equiv}=\varepsilon_{r,SiO_2}L_gW_g/(1\mathrm{nm})$ ), highest current is obtained for  $m^*/m_0=0.05$ , while for 0.3 nm EOT, peak  $I_d$  is obtained at  $m^*/m_0=0.2$ ; given one isotropic valley, low  $m^*$  gives low  $I_d$  in nm FETs<sup>1</sup>, though low  $m^*$  reduces  $\tau_{ch}$  for any EOT. Note that for Si  $\{100\}$  FETs<sup>6</sup>,  $m^*/m_0=0.19$  and g=2.

Given a  $\{100\}$ -oriented FET and  $\Gamma$ -valley transport, the vertical confinement mass  $m_q$  and transport mass  $m_{\parallel}$  are equal. For good FET electrostatics,  $T_{\text{inv}}$  must be less than  $\sim L_g/10$ , and  $E_{\text{well}}-E_{\Gamma} \approx \pi^2\hbar^2/2m_qT_{\text{well}}^2 \approx \pi^2\hbar^2/8m_qT_{\text{inv}}^2$ , and is large for small  $L_g$ . Noting that  $E_F-E_{\text{well}}=n_s(dn_s/dE_f)^{-1}=n_s(2\pi\hbar^2/gm_{\perp}^{1/2}m_{\parallel}^{1/2})$  also is large, once  $(E_F-E_{\Gamma}) \geq (E_L-E_{\Gamma})$  the L valleys populate and  $v_{\text{inj}}$  decreases. High  $n_s$  cannot be obtained in the  $\Gamma$  valleys in low-m\* materials, nor is  $L_g < 20$  nm feasible; such FETs can no longer scale.

Thin wells with high carrier concentrations show increased transport mass from nonparabolic bands. Assuming  $E(1+\alpha E)=\hbar^2 k^2/2m^*$ , the effective mass  $m^*!=m^*(1+2\alpha(E_{well}-E_{\Gamma}))$  of the bound state increases from confinement, and then further increases from the channel charge density. Further, with thin wells, and low  $m_q$ , the wavefunction extends into the barriers, further increasing the in-plane masses  $m_{\perp}$  and  $m_{\parallel}$ .

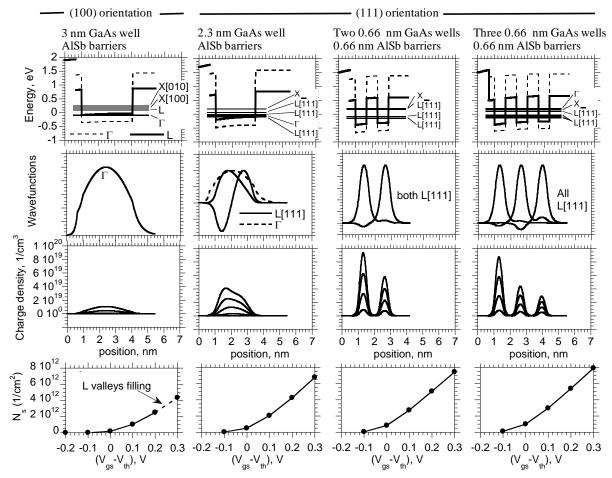

Consider a 3 nm (100) GaAs well with strained AlSb barriers. The L bound states lie 177 meV above that of  $\Gamma$ . Equilibrium (not ballistic transport) analysis uses Schrödinger-Poisson, the effective mass approximation, and parabolic bands. 0.66 nm Al $_2$ O $_3$  and 0.34 nm AlSb lie between the well and gate, giving  $T_{eq}$  =0.37 nm. Under strong inversion  $C_{g-d}/L_gW_g \cong 2.4~\mu\text{F/cm}^2$ , far below  $C_{ox}/L_gW_g = 9~\mu\text{F/cm}^2$ , and the high-mass L-valleys fill for  $n_s > 2.4 \cdot 10^{12}~\text{cm}^{-2}$ . Under ballistic transport,  $C_{dos}$  and the maximum  $n_s$  would both decrease 2:1.

Increased  $C_{dos}$  and low  $m_{\parallel}$  can be obtained by using L valley minima alone or combined with the  $\Gamma$  valley. The InGaAs, GaAs, and GaSb L-valleys have low  $m_{\scriptscriptstyle l}/m_{\scriptscriptstyle o}$  (0.062-0.1) and high  $m_{\scriptscriptstyle l}/m_{\scriptscriptstyle o}$  (1.23-1.9). The L-valleys have  $\langle 111 \rangle$  orientations, and transport in a (100) channel includes contributions from the high  $m_{\scriptscriptstyle l}$ . Using instead a (111)

wafer, the L[111] valley is oriented vertically, and shows low transport masses ( $m_{\parallel}=m_{\perp}=m_{_l}$ ) and high confinement mass ( $m_{_q}=m_{_l}$ ). The L[111],[111], and [111] minima show high<sup>6</sup> transport mass ( $m_{_l}+8m_{_l}$ )/9 in one in-plane direction, but low confinement mass<sup>6</sup>  $m_{_q}=9m_{_l}m_{_l}/(m_{_l}+8m_{_l})$ . The X valleys have  $\langle 100 \rangle$  orientations, in bulk InGaAs, GaAs, and GaSb have minima well above  $\Gamma$  and L, and in a (111) well have low  $m_{_q}=3m_{_l}m_{_l}/(m_{_l}+2m_{_l})$  quantization mass. In appropriate thin wells, the X and L[111], [111], and [111] quantized states are driven to high energies and depopulated.  $T_{well}$  can be selected to place  $\Gamma$  and L[111] at similar energies, doubling  $C_{dos}$ , or  $\Gamma$  driven in energy above L[111], and transport provided in multiple L[111] valleys.

Consider a 2.3 nm (111) GaAs well with strained AlSb barriers.  $m_g$  is large, thus the first two L [111] states are separated by only 84 meV. The  $\Gamma$  state lies 41 meV above the lower L [111] state; 3 valleys are populated over a 300mV range of  $V_{gs}$ . L [111], [111], and [111] and X lie 175 and 288 meV above the lower L [111] state. In equilibrium simulation  $n_s = 7 \cdot 10^{12}$  cm<sup>-2</sup> with  $V_{gs} - V_{dt} = 300$  mV, and moderately higher  $n_s$  does not populate heavy valleys. In inversion,  $C_{g-ch}/L_gW_g \cong 4~\mu\text{F/cm}^2$ . The benefit over the (100) design is larger in the ballistic case. In InGaAs, GaAs, and GaSb, the L-valley  $m_t$  is >25:1 larger than the  $\Gamma$ -valley mass, hence  $T_{well}$  can be made

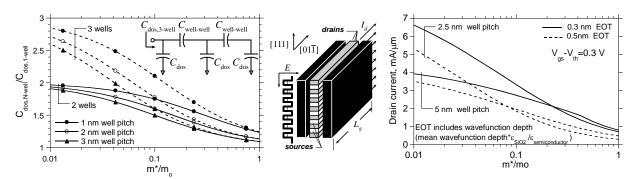

In InGaAs, GaAs, and GaSb, the L-valley  $m_l$  is >25:1 larger than the  $\Gamma$ -valley mass, hence  $T_{well}$  can be made 5:1 smaller for a given quantization energy.  $m_q$  is high in the barriers, hence multiple wells can be placed between ~ 1 nm barriers without significant well coupling hence energy redistribution. Multiple L[111] quantum wells can stacked to increase g hence  $C_{dos}$ . Consider a FET with two 0.66 nm (2 ML) (100) GaAs wells separated by strained 0.66 nm AlSb barriers. Given zero field, the two L[111] states split in energy by < 40 meV; for  $V_{gs} - V_h = 300$  mV the separation is 56 meV. L[111],[111], and [111] and X lie 322 and 346 meV above the lower L[111] state. The  $\Gamma$  state is driven to high energy. In equilibrium,  $n_s$  is driven to  $7.8 \cdot 10^{12}$  cm<sup>-2</sup> with  $V_{gs} - V_h \sim 300$  mV; moderately higher  $n_s$  does not populate heavy valleys.  $C_{g-ch}/L_gW_g \cong 4 \mu F/\text{cm}^2$ . The advantage over  $\Gamma$  {100} is greater for ballistic transport. A triple- well L[111] design gives similar results. In these FETs, the upper wells charge most strongly because of charge division between the wells'  $C_{dos}$  and the well-well capacitance  $C_{well} = \varepsilon L_g W_g / T_{pixh}$ , where  $T_{pixh}$  is the well pitch. With thin wells, and low  $m_t$ ,  $C_{dos}$  can be increased 1.5:1 to 2.2:1. In these FETs, the X and L[111], [111], and [111] valleys play a similar role to the L and X valleys in {100}

In these FETs, the X and L[111], [111], and [111] valleys play a similar role to the L and X valleys in {100}  $\Gamma$ -transport FETs. For high  $v_{inj}$  it is sufficient to avoid populating high- $m_{\parallel}$  valleys in the low-field control region; scattering into these valleys in the drain high-field region increases the drain delay but does not reduce  $I_d$ .

High  $I_a/W_g$  can be obtained from a FINFET with multiple (111) wells forming an array with many conduction channels per unit width. Because the L[111] vertical mass  $m_q$  is large, the well pitch can be made small (2-5 nm) while maintaining small well coupling hence small vertical eigenstate energy splitting. Transport is thus 1-D with each well having L[111] valley minima energies  $E_n = \hbar^2 \pi^2 n^2 / 2 m_i T_{pitch}^2$  and per-state current  $I_n = gq(E_f - E_n)/\pi \hbar$  and charge  $Q_n = qg(2m^*(E_f - E_n))^{1/2}L_g/\pi \hbar$ . From  $Q_n$  and the specified EOT, the dielectric voltage drop is found and  $I_a/V_g$  computed. At  $V_{gs} - V_{fn} = 0.3$  V,  $T_{pitch} = 2.5$  nm,  $m_i/m_0 = 0.06$ , and  $C_{equiv} = \varepsilon_{r,SiO_2} L_g W_g/(0.3 \text{ nm})$ , we find  $I_a/W_g \sim 4$  mA/ $\mu$ m per gate. We assume a P-doped fin with separate inversion layers for each gate. Inversion layer confinement raises the L[111] states' energies relative to other minima, hence the inversion layer should be thicker than  $T_{pitch}$  and the fins oriented as  $[01\bar{1}]$  for the most rapid increase in L  $[11\bar{1}]$  and  $[1\bar{1}1]$  energies with lateral confinement. L[ $\bar{1}11$ ] has low  $m_i$  and is populated without degrading  $v_{ini}$ .

A final design uses a planar (110)-oriented channel, with the L[111] and [111] minima projecting into the transport plane with a low transport mass  $m_{\parallel} = m_{r}$  in the [110] direction, a high perpendicular  $m_{\perp} = (m_{r} + 2m_{r})/3$  in the [001] direction, and moderate  $m_{q} = 3m_{r}m_{r}/(m_{r} + 2m_{r}) \approx 3m_{r}$ . The L[111] and [111] minima have higher  $3m_{r}m_{r}/(m_{r} + 2m_{r})$  mass in the [110] direction, and have low  $m_{q} = m_{r}$ . Quantization favors population of the desired [111], [111] minima, but the separation in energy of the undesired valleys is only moderate.

Several designs above use very thin wells and barriers. We must determine whether such layers can be grown and whether mobility is acceptable. We must refine the energy calculations. 2-4 ML GaSb and InAs wells<sup>7,8</sup> have been grown. Preliminary tightbinding calculations using an sp3d5s\* basis<sup>9</sup> conducted for triple 1.1nm GaSb wells with 1.1nm AlSb barriers confirm the symmetry of the lowest state manifold and its expected transverse dispersion. Excited states are slightly lower than predicted by effective mass, but the design still appears viable.

We acknowledge extensive discussions with H. Kroemer, A. C. Gossard, B. Brar, and J. Albrecht. J.N.S. was supported by the Internal Research & Development program of The Aerospace Corporation.

<sup>&</sup>lt;sup>1</sup> P. M. Solomon, S. E. Laux, 2001 IEEE IEDM, 2-5 Dec., Technical Digest, pp. 5.1.1 - 5.1.4

<sup>&</sup>lt;sup>2</sup> I. Vurgaftman, J. R. Meyer, L. R. Ram-Mohan, J. Appl. Phys, Vol. 89, 11, pp 5815-5875.

<sup>&</sup>lt;sup>3</sup> S.E. Laux, 2004 IEDM, Technical Digest, December, pp.135 - 138

<sup>&</sup>lt;sup>4</sup> A. Rahman, G. Klimeck, T. B. Boykin, M. Lundstrom, 2004 IEDM, Dec. 13-15, Tech. digest pp. 139 - 142

<sup>&</sup>lt;sup>5</sup> K. Natori, J. Appl. Phys., vol. 76, no. 8, pp. 4879–4890, 1994. .

<sup>&</sup>lt;sup>6</sup> F. Stern, W. E. Howard, Physical Review, Vol. 163, No. 3, 15 Nov 1967, pp. 816-835

<sup>&</sup>lt;sup>7</sup> B. Brar, et al, Appl. Phys. Lett. 62 (25), pp 3303-3305, also: J. of Crystal Growth 127 (1993) 752-754

<sup>&</sup>lt;sup>8</sup> T. B. Boykin, Appl. Phys. Lett. 64 (12), 21 March 1994, pp. 1529-1531

<sup>&</sup>lt;sup>9</sup> G Klimeck, et al, IEEE Transactions on Electron Devices, Vol. 54, 2079 (2007)

**Table 1:** Constant-voltage / constant-velocity FET scaling laws: changes required for  $\gamma$ :1 increased bandwidth in an arbitrary circuit

|   | L_S/D  | $T_{ox} T_{well}$ |       |     |

|---|--------|-------------------|-------|-----|

|   |        | gate              |       | _ ↓ |

|   | source | <b>ネ ホ</b>        | drain | ↓   |

| П |        | 0 00 000          |       |     |

| parameter                                                                                 | law           | parameter                                                                        | law                            |

|-------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------|--------------------------------|

| gate length $L_{g}$ , source-drain contact                                                | $\gamma^{-1}$ | electron density                                                                 | γ¹                             |

| lengths $L_{S/D}$ (nm)                                                                    |               | $n_s = (C_{g-ch}/L_gW_g)(V_{gs}-V_{th})/q \text{ (cm}^{-2})$                     |                                |

| gate width $W_g$ (nm)                                                                     | $\gamma^{-1}$ | injection velocity (m/s)                                                         | $\gamma^{0}$                   |

| equivalent oxide thickness                                                                | $\gamma^{-1}$ | $v_{injection} = (4/3\pi)(2qC_{g-ch}(V_{gs}-V_{th})/m_{\parallel}C_{dos})^{1/2}$ |                                |

| $T_{eq} = T_{ox} \mathcal{E}_{SiO_2} / \mathcal{E}_{oxide} $ (nm)                         |               | drain current $I_d = qn_s v_{injection}$ (mA)                                    | γ°                             |

| dielectric capacitance                                                                    | γ-1           | drain current density $I_a/W_g$ ( mA/ $\mu$ m )                                  | γ¹                             |

| $C_{ox} = \varepsilon_{SiO_2} L_g W_g / T_{eq} (fF)$                                      |               | transconductance $\partial I_d / \partial V_{gs}$ (mS)                           | $\gamma^{0}$                   |

| wavefunction mean depth $T_{inv}$ (nm)                                                    | $\gamma^{-1}$ | gate-source, gate-drain fringing capacitances                                    | $\gamma^{-1}$                  |

| wavefunction depth capacitance                                                            | $\gamma^{-1}$ | $C_{gs,f} \propto \varepsilon W_g$ , $C_{gd} \propto \varepsilon W_g$ (fF)       |                                |

| $C_{depth} = \mathcal{E}_{semi} L_{g} W_{g} / T_{inv} 	ext{ (fF)}$                        |               | S/D access resistances $R_s$ , $R_d(\Omega)$                                     | $\gamma^{0}$                   |

| DOS capacitance (ballistic case)                                                          | $\gamma^{-1}$ | S/D access resistivities $R_s W_g$ , $R_d W_g (\Omega - \mu m)$                  | $\gamma^{-1}$                  |

| $C_{dos} = q^2 g (m_{\parallel}^* m_{\perp}^*)^{1/2} L_g W_g / 2\pi \hbar^2 \text{ (fF)}$ |               | S/D contact resistivities $\rho_c (\Omega - \mu \text{m}^2)$                     | $\gamma^{-2}$                  |

| gate-channel capacitance                                                                  | $\gamma^{-1}$ | temperature rise (one device, K)                                                 | ~ W <sub>g</sub> <sup>-1</sup> |

| $C_{e-ch} = [1/C_{ox} + 1/C_{depth} + 1/C_{DOS}]^{-1} (fF)$                               |               |                                                                                  |                                |

1.5 EOT includes wavefunction depth term (mean wavefunction depth\*  $\epsilon_{SiO2}/\epsilon_{semiconductor}$ ) 1.0 nm 0.6 nm 0.4 nm 0.4 nm 0.4 nm 0.4 nm 0.5 nm\*/m<sub>o</sub>

Figure 1: FET normalized drive current  $K_1$  where  $I_a/W_g=(84~\text{mA/}\mu\text{m})\cdot K_1\cdot ((V_{gs}-V_{\text{th}})/1\text{V})^{3/2}$ , and g is the # of valley minima.

Figure 2: FET normalized transit time  $K_2$  where  $au_{ch} = Q_{ch}/I_D = K_2 \cdot (L_g/2.5 \cdot 10^7 \text{ cm/s}) \cdot (1 \text{V}/(V_{gs} - V_{th}))^{1/2}$ . EOT includes dielectric thickness and wavefunction depth.

Figure 3:  $\Gamma$ , L, and X-valley orientations for (100)- and (111)-oriented wafers

Table 2: Parameters of  $\Gamma$ , L, and X-valleys for several suitable semiconductors

|                                        |           | Γ valley | X valleys* |               |                      | L valleys                                                  |               |                                                          |

|----------------------------------------|-----------|----------|------------|---------------|----------------------|------------------------------------------------------------|---------------|----------------------------------------------------------|

| material                               | substrate | $m*/m_0$ | $m_l/m_0$  | $m_{t}/m_{0}$ | $E_{_X}-E_{_\Gamma}$ | $m_l/m_0$                                                  | $m_{t}/m_{0}$ | $E_{\scriptscriptstyle L}-E_{\scriptscriptstyle \Gamma}$ |

| In <sub>0.5</sub> Ga <sub>0.5</sub> As | InP       | 0.045    | 1.29       | 0.19          | 0.83 eV              | 1.23                                                       | 0.062         | 0.47 eV                                                  |

| InAs                                   | InP       | 0.026    | 1.13       | 0.16          | 0.87 eV              | 0.65                                                       | 0.050         | 0.57 eV                                                  |

| GaAs                                   | GaAs      | 0.067    | 1.3        | 0.22          | 0.47 eV              | 1.9                                                        | 0.075         | 0.28 eV                                                  |

| GaSb                                   | GaSb      | 0.039    | 1.51       | 0.22          | 0.30 eV              | 1.3                                                        | 0.10          | 0.07 eV                                                  |

| Si                                     | Si        |          | 0.92       | 0.19          | (negative)           | *Si minima at $\Delta \sim 0.85 \cdot \langle 100 \rangle$ |               |                                                          |

Figure 3. Simulation of  $\Gamma$ ,  $\Gamma$ -L, and multiple-L valley FETs: quantized states, wavefunctions, charge density, and sheet carrier concentrations vs. bias. Well energies and charge densities calculated using the effective mass approximation and assuming parabolic bands. The gate dielectric is 0.3 nm  $Al_2O_3$ . Well charge densities are computed assuming thermal equilibrium; in the ballistic limit,  $C_{does}$  is 2:1 smaller than in equilibrium, and multiple-valley FET channels provide a proportionally larger improvement in  $N_s$ . 0.66 nm is 2 monolayers.

Figure 4: Increase in density of states for 2-L-well and 3-L-well FET channels as a function of carrier effective mass and well-well pitch.

Figure 5: Computed drain current drain current density, per gate, of a FINET with (111)-oriented multiple quantum wells as a function of carrier effective mass and well-well pitch.