## 60 nm gate length Al<sub>2</sub>O<sub>3</sub> / In<sub>0.53</sub>Ga<sub>0.47</sub>As gate-first MOSFETs using

InAs raised source-drain regrowth

Andrew D. Carter, J. J. M. Law, E. Lobisser, G. J. Burek, W. J. Mitchell,

B. J. Thibeault, A. C. Gossard, and M. J. W. Rodwell

ECE Department, University of California, Santa Barbara, CA 93106-9560

Phone: 805-893-3273, Fax: 805-893-3262, Email: adc@ece.ucsb.edu

Given adequately low source/drain (S/D) access resistivity and dielectric interface trap density ( $R_{access} < 50 \Omega - \mu m$ ,<sup>1</sup> and  $D_{\mu} < 2 \cdot 10^{12} \text{ cm}^{-2} \text{ eV}^{-1}$ ,<sup>2</sup> respectively), InGaAs MOSFETs will provide greater on-state current than silicon MOSFETs at the same effective oxide thickness (EOT). The access resistance must be obtained in a self-aligned structure with a contacted gate pitch ~4 times the physical gate length ( $L_g$ ), e.g. 116 nm at 32 nm  $L_g$ ,<sup>3</sup> while control of short channel effects demands that the S/D region depth be only a fraction of gate length; low-resistance, ultra-shallow fully self-aligned III-V MOS processes must therefore be developed. Here we report a 60 nm  $L_g$  In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET fabricated in a gate-first process with self-aligned raised InAs S/D access regions formed by MBE regrowth. The devices have a peak drive current of 1.36 mA/µm at  $V_{ds} = 1.25$  V and  $V_{gs} = 3$  V and an  $R_{on} = 341$  ohm-µm. To our knowledge this is the lowest  $R_{on}$  and smallest  $L_g$  reported to date for In<sub>0.53</sub>Ga<sub>0.47</sub>As surface channel MOSFETs.<sup>4</sup>

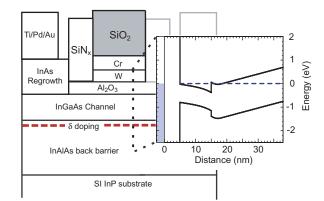

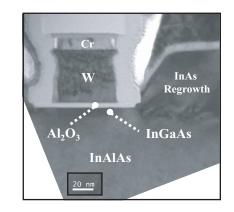

The epitaxial layer structure, grown by molecular beam epitaxy (MBE), has a semi-insulating Fe doped InP substrate, 300 nm not intentionally doped (NID)  $In_{0.52}Al_{0.48}As$ , 3 nm  $In_{0.52}Al_{0.48}As$  n-type Si-doped at  $3 \cdot 10^{19}$  cm<sup>-3</sup>, and 10nm NID  $In_{0.53}Ga_{0.47}As$ . Prior to atomic layer deposition (ALD) growth of the ~5 nm Al<sub>2</sub>O<sub>3</sub> gate dielectric, the surface was treated by repeated hydrogen plasma / trimethylaluminum (TMA) cycles. A 60 nm sputtered W/15 nm electron beam evaporated Cr/400 nm PECVD SiO<sub>2</sub>/15 nm electron beam evaporated Cr gate stack was blanket-deposited. Gate lengths between 60 nm to 1.3 µm were defined by patterning the upper Cr layer with a combination of electron beam and optical lithography. A high power inductively coupled (ICP) plasma SF<sub>6</sub>/Ar etch defined vertical pillars in the SiO<sub>2</sub> layer. Cl<sub>2</sub>/O<sub>2</sub> ICP etched the Cr, and a SF<sub>6</sub>/Ar ICP etched the W gate. Etch undercuts in the W and Cr layers are less than 10 nm. 25nm SiN<sub>x</sub> was deposited by PECVD and etched in a CF<sub>4</sub>/O<sub>2</sub> ICP, defining gate sidewalls. After gate oxide removal in AZ400K, the semiconductor surface was oxidized by exposure to UV ozone and a subsequent removal of this oxide by a 10:1 DI H<sub>2</sub>O:HCl etch prior to MBE loading. Regrowth of ~50 nm InAs n-type Si-doped at ~1·10<sup>20</sup> cm<sup>-3</sup> (~5·10<sup>19</sup> cm<sup>-3</sup> active doping) was done as outlined in ref. <sup>5</sup>. 20 nm Ti / 60 nm Pd/120 nm Au was lifted off for source-drain metallization, and devices were isolated in a 1:1:25 H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:DI H<sub>2</sub>O solution.

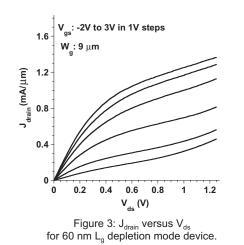

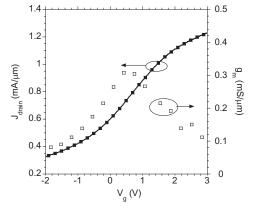

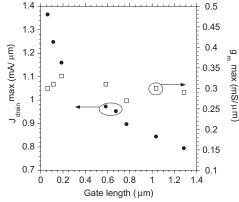

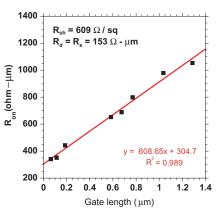

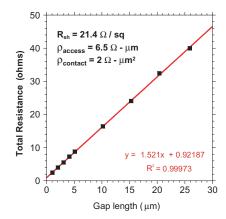

Devices were characterized using an Agilent 4155C semiconductor parameter analyzer. A 60 nm  $L_g / 9 \mu m$   $W_g$  device has a peak drain current density of 1.36 mA/µm at  $V_{ds} = 1.25$  V and  $V_{gs} = 3$  V and an  $R_{on} = 341$  ohm-µm. Extrapolated source and drain resistances  $R_S = R_D = 153$  ohm-µm for these devices. Short channel effects and large delta doping underneath the channel prevent complete channel depletion. Heavy pulse doping (~1·10<sup>13</sup> cm<sup>-2</sup>) was used to overcome  $D_{it}$ -induced channel depletion underneath the ungated sidewall regions, which in turn increased device source to drain leakage. The ~60 nm  $L_g$  device has a DC transconductance  $g_m$  of 0.3 mS/µm at a  $V_{GS} = 0.7$  V. Gate leakage current is < 20 nA/µm at all gate biases. The extracted  $R_S = (6.5 \text{ mS/µm})^{-1}$  is too low to explain the measured  $g_m = 0.3$  mS/µm; suggesting that the transconductance is instead limited by the thick oxide and large  $D_{it}$ . In conclusion, we have shown a 60 nm  $L_g$  Al<sub>2</sub>O<sub>3</sub>/InGaAs MOSFET with low  $R_{on}$  and low access resistance. Future work will include scaling the gate dielectric EOT, reducing process-damage-induced<sup>6</sup>  $D_{it}$ , and reduced width and increased carrier concentration in the sidewall regions surrounding the gate.

Acknowledgements: This research was supported by the SRC Non-classical CMOS Research Center (Task 1437.006). A portion of this work was done in the UCSB nanofabrication facility, part of NSF funded NNIN network and MRL Central Facilities supported by the MRSEC Program of the NSF under award No. MR05-20415.

<sup>&</sup>lt;sup>1</sup>M. J. W. Rodwell, et al, 2010 Device Research Conference, Notre Dame, Indiana.

<sup>&</sup>lt;sup>2</sup>A.D. Carter, et al, Jpn. J. Appl. Phys., to be submitted.

<sup>&</sup>lt;sup>3</sup>S. Natarajan, *et al*, IEDM 2008.

<sup>&</sup>lt;sup>4</sup> M. Radosavljevic, *et al*, IEDM 2009 and 2010, T. Kanazwa, *et al*, IPRM 2010, Y.Q. Wu, *et al*, IPRM 2010, and U. Singisetti, *et al*, IEEE Electron Device Lett. **30** (2009).

<sup>&</sup>lt;sup>5</sup>M.A. Wistey, *et al*, North American MBE Conference 2009.

<sup>&</sup>lt;sup>6</sup> G. Burek, et al, submitted to Applied Physics Letters.

Figure 1: Schematic cross section of the gate first MOSFET. Inset: Energy band diagram across the gated channel region of the device.

Figure 2: TEM cross section of a gate first MOSFET.

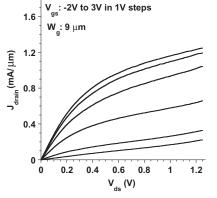

Figure 4:  $J_{\rm drain}$  versus  $V_{\rm ds}$  for 115 nm  $L_g$  depletion mode device.

Figure 6: Measured  $J_{drain}$  versus  $V_{gs}$  ( $V_{ds}$  = 1 V) and DC transconductance for the 60 nm gate length device. Transconductance data is 5% weighting smoothed from raw data.

Figure 7: Maximum drain current density and DC transconductance versus gate length for 9μm gate width devices.

Figure 5:  $R_{on}$  as a function of gate length for 9  $\mu$ m gate width devices, measured at  $V_{qs}$  = 3 V,  $V_{ds}$  = 0 to 0.1 V.

Figure 8: Transmission line measurement for 14 μm gap width of source-drain metalization and InAs regrowth.