# 40Gbit/s Coherent Optical Receiver Using a Costas Loop

H. Park, M. Lu, E. Bloch, T. Reed, Z. Griffith, L. Johansson,

L. Coldren, and M. Rodwell

University of California at Santa Barbara

### Introductions

# Motivations

- Higher Spectral Efficiency QPSK / multi-level QAMs

- Higher Data Rates 40Gbit/s, 100Gbit/s, and even higher

- Higher Receiving Sensitivity

# **Recent Coherent Optical Communication**

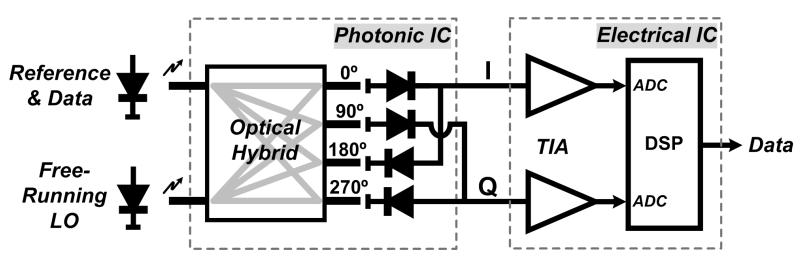

- Coherent detection based on DSP

- Local oscillator (LO) laser

- Polarization diversity 90° optical hybrid

- Balanced detectors

- High speed analog to digital convertor (ADC)

- High speed digital signal processing (DSP)

# **Coherent Optical Communications**

# **Coherent Optical Receiver – I**

- Advantages:

- Multi-level constellations

- High data rate

- Phase managements

- Polarization managements

- Dis-advantages:

- Electrical circuit complexity

- Speed limitations

- Cost issues

- Power consumptions

## **Coherent Optical Communications**

# **Coherent Optical Receiver – II**

- Homodyne OPLL based coherent receiver <u>Costas Loop</u>

- Optical carrier recovering technique

**Requiring Stable OPLL**

# **Coherent Optical Communications**

# **Coherent Optical Receiver – II**

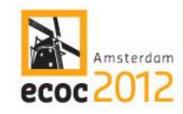

- Challenges:

- Long loop delays (\*1ns)

- Narrow loop bandwidth (\*100MHz)

- Transmitting and LO lasers' linewidth

- Sensitive by external variations

- Solutions:

- Integrated circuits (photonic IC, electrical IC)

- Feed-forward loop filter topology

- Minimizing Interconnection delays

- Digitally operating feedback system

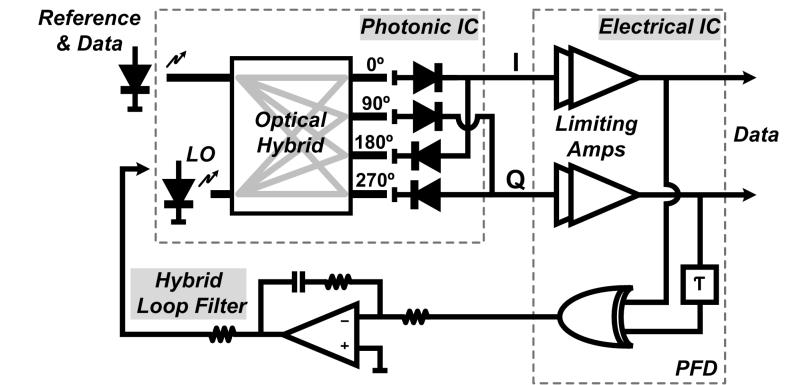

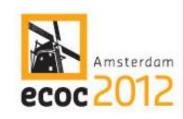

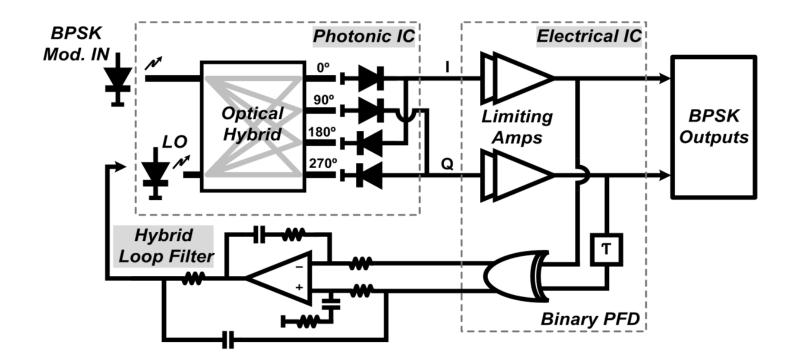

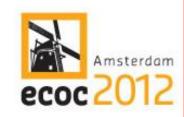

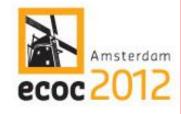

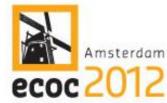

# Homodyne OPLL + Costas Loop

- Three blocks: photonic IC, electrical IC, and hybrid loop filter

- High speed BPSK data demodulations

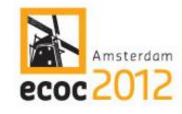

# **Photonic IC**

- SG-DBR laser 40nm tunable ranges

- 90° optical hybrid

- 4 un-balance photodiodes 30GHz bandwidth

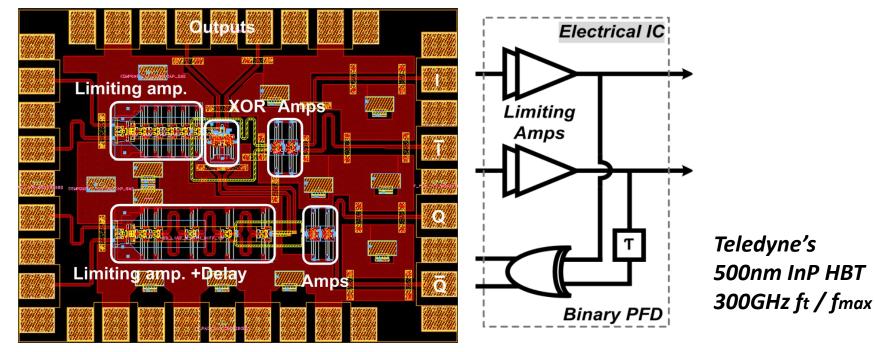

# **Electrical IC**

- Limiting amplifiers

- Phase / frequency detector (PFD) XOR + delay line

- Main path by integrator high gain at DC and low frequencies

- Feed-forward path passive capacitor component

# **Integration on a Single Carrier board**

- Compact chip size of 10 x 10mm<sup>2</sup>

- Total delay (120ps)=PIC (40ps)+EIC (50ps)+Interconnection (30ps)

**1GHz Loop Bandwidth is feasible**

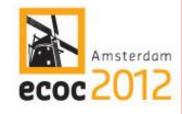

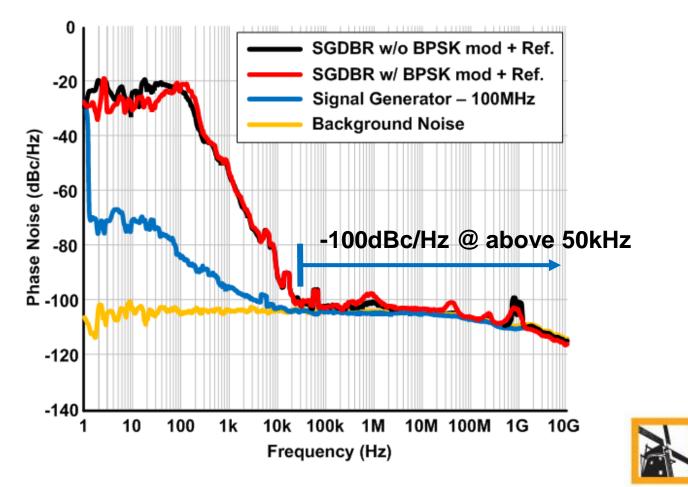

Beating spectrum: locked SG-DBR + Ref. with 100MHz mod.

1.1GHz closed loop bandwidth

#### **Cross correlation between SG-DBR and reference lasers**

#### <u>-100dBc/Hz @ above 50kHz</u>

Amsterdam

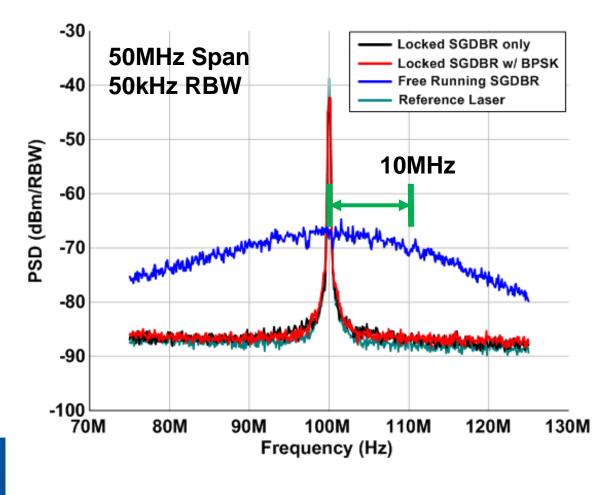

Linewidth using self-heterodyne with 25km optical fiber

<u>10MHz linewidth</u> for free-running SG-DBR

UCSB

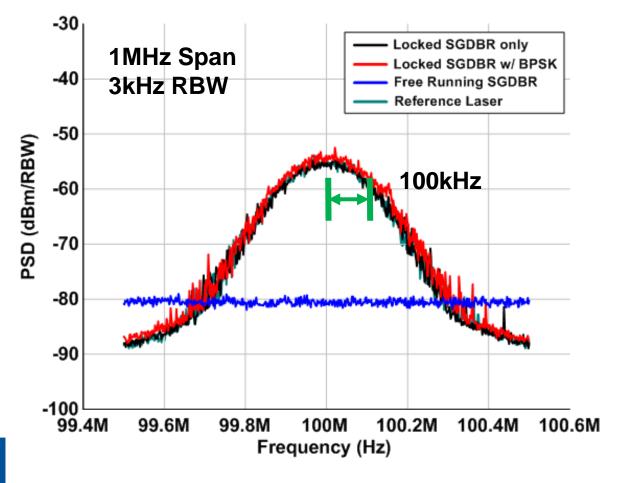

#### **Reference laser (Koshin) linewidth 100kHz**

#### 100kHz linewidth for locked SG-DBR laser

JCSB

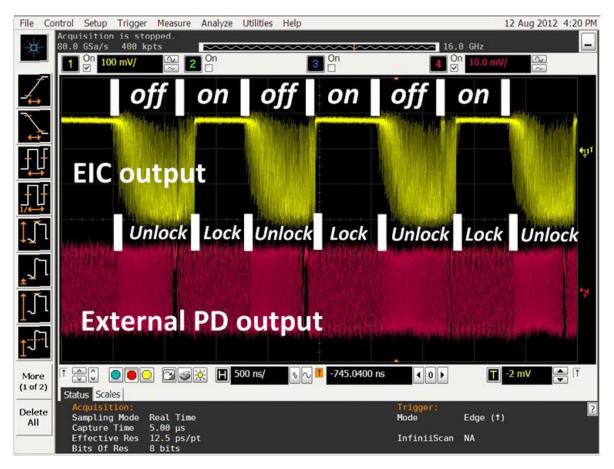

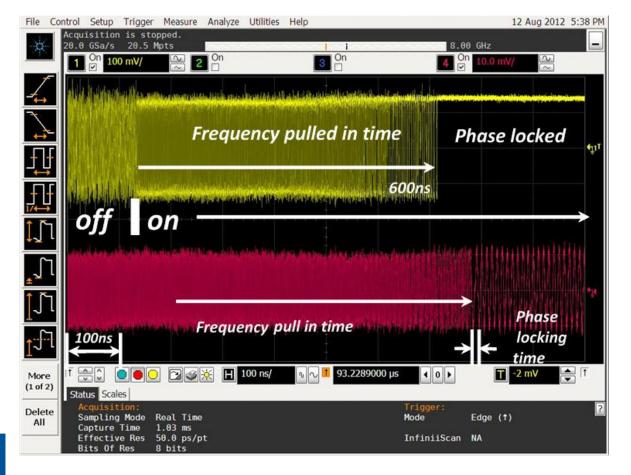

#### 400MHz/512bits ON-OFF laser

#### Locking conditions: EIC output – <u>DC</u>, External PD output – <u>100MHz</u>

#### Frequency pull-in time ~600ns

#### Phase lock time <10ns

#### \* Worst conditions

### **Test Results – BPSK Receiver**

#### PRBS 2<sup>31</sup>-1 signals – up to 40Gb/s BPSK data

#### **Open eye diagrams for 25Gb/s and 40Gb/s**

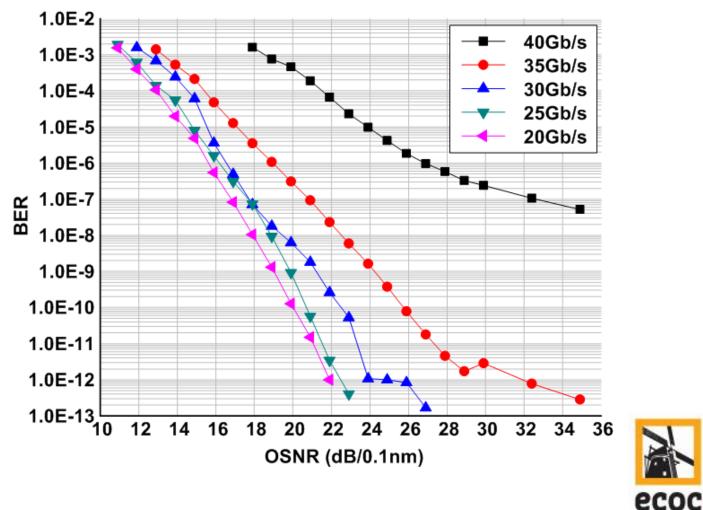

### **Test Results – BPSK Receiver**

#### BER vs. OSNR (20Gb/s to 40Gb/s)

#### Error-free up to 35Gb/s , < 1.0E-7 @ 40Gb/s

Amsterdam

# **Conclusions**

- The first demonstration highly integrated optical Costas loop receiver

- Integrated PIC, integrated EIC, and feed-forward loop filter

- The receiver is Integrated within 10x10mm<sup>2</sup>

- A stable homodyne OPLL by 120ps delay and 1.1GHz loop bandwidth

- 40Gbit/s BPSK coherent optical receiver (BER < 1.0e-7)

- Error-free (BER < 1.0e-12) up to 35Gbit/s

- Future works: QPSK receivers / long haul tests / dispersion compensations / polarization managements

### Thank you for your attention !