# Scaling of InGaAs/InAlAs HBTs for High Speed Mixed-Signal and mm-Wave ICs.

M.J.W. Rodwell, M. Urteaga, Y. Betser \*, T. Mathew, P. Krishnan, D. Scott, S. Jaganathan D. Mensa, J. Guthrie<sup>†</sup>, R. Pullela <sup>‡</sup>, Q. Lee<sup>§</sup>, B. Agarwal <sup>¶</sup>, U. Bhattacharya <sup>||</sup>, S. Long Department of Electrical and Computer Engineering, University of California Santa Barbara, CA 93106, U.S.A.

and

S.C. Martin, R. P. Smith\*\*

NASA Jet Propulsion Labs, California Institute of Technology

Pasadena, CA, USA

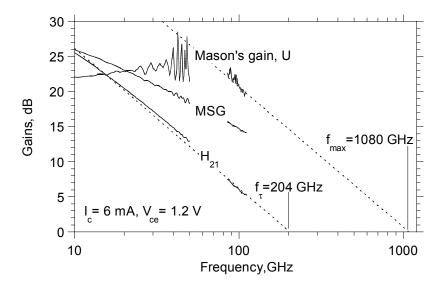

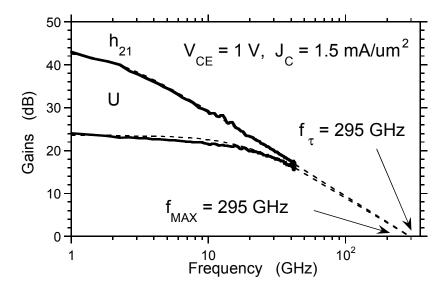

High bandwidths are obtained with heterojunction bipolar transistors by thinning the base and collector layers, increasing emitter current density, decreasing emitter contact resistivity, and reducing the emitter and collector junction widths. In mesa HBTs, minimum dimensions required for the base contact impose a minimum width for the collector junction, frustrating device scaling. Narrow collector junctions can be obtained by using substrate transfer processes, or -if contact resistivity is greatly reduced - by reducing the width of the base Ohmic contacts in a mesa structure. HBTs with submicron collector junctions exhibit extremely high  $f_{max}$  and high gains in mm-wave ICs. Logic gate delays are primarily set by depletion-layer charging times, and neither  $f_{\tau}$  nor  $f_{max}$ is indicative of logic speed. For high speed logic, epitaxial layers must be thinned, emitter and collector junction widths reduced, current density increased, and emitter parasitic resistance decreased. Transferred-substrate HBTs have obtained 21 dB unilateral power gain at 100 GHz. If extrapolated at -20 dB/decade, the power gain cutoff frequency  $f_{max}$ is 1.1 THz. Transferred-substrate HBTs have obtained 295 GHz  $f_{\tau}$ . Demonstrated ICs include lumped and distributed amplifiers with bandwidths to 85 GHz, 66 GHz masterslave flip-flops, and 18 GHz clock rate  $\Delta - \Sigma$  ADCs.

#### 1. Introduction

Research in wide bandwidth heterojunction bipolar transistors (HBTs)  $^{1}$   $^{2}$  is driven by applications in high-frequency communications and radar. In optical fiber communications, integrated circuits for 40 Gb/s transmission are now in development  $^{5}$ ,  $^{6}$ . Emergence of 160 Gb/s transmission equipment in the near future must rely on a timely and substantial improvement in the bandwidth of semiconductor elec-

<sup>\*</sup>Y. Betser is now with Anadigics Corp., Israel.

$<sup>^{\</sup>dagger}\mathrm{J}.$  Guthrie is now with Nortel Networks, Inc.

<sup>&</sup>lt;sup>‡</sup>D. Mensa, R. Pullela, and S. Jaganathan are now with Gtran, Inc

<sup>§</sup>Q. Lee is now with Lucent Technologies

<sup>¶</sup>B. Agarwal is now with Conexant Corp.

U. Bhattacharya is now with Intel Corp.

<sup>\*\*</sup>R. P. Smith is now with Cree Research, Inc.

tronics. 160 Gb/s fiber transmission will require amplifiers with flat gain and linear phase over a  $\sim$  DC-110 GHz bandwidth and master-slave latches <sup>3</sup> (used in decision circuits, multiplexers, and phase-lock loops) operable at 80 GHz or 160 GHz clock frequency.

A second set of driving applications are wideband, high-resolution analog-digital converters, digital-analog converters, and direct digital frequency synthesizers <sup>8</sup>. Increased bandwidths of these mixed-signal ICs will increase the bandwidth and frequency agility of military radar and communications systems <sup>4</sup>. In ADCs and DACs, very high resolution is obtained using oversampling techniques <sup>7,9</sup>, with clock frequencies  $\sim 100 \times$  the signal bandwidths. In high resolution ADCs, to avoid metastability errors in latched comparators driven by small input signals, the circuit time constants must be much smaller than the periods of the clock signals employed. Similar design constraints apply to high-resolution DACs. High resolution ADCs and DACs consequently require transistor bandwidths  $10^2:1$  to 10<sup>4</sup>: 1 larger than the signal frequencies involved. Transistors with several hundred GHz  $f_{\tau}$  and  $f_{max}$  would enable high-resolution microwave mixed-signal ICs.

A third driving application is in monolithic millimeter-wave integrated circuits (MIMICs). In microwave and millimeter-wave receivers, the low-noise RF preamplifier, several stages of amplification, and frequency conversion (a mixer), are typically implemented as small-scale monolithic circuits. Similar MIMICs are used in the transmitter. The operating frequency is set by the application, but progressive improvements in transistor bandwidths permit the evolution of radar and communications ICs to progressively higher frequencies. A transistor with a 1 THz power-gain cutoff frequency would provide useful gain over the full 30-300 GHz millimeter-wave band. This would permit e.g. digital radio links with millimeterwave carrier frequencies and 1-10 Gb/s channel capacities. Until recently, III-V high-electron-mobility field-effect-transistors (HEMTs) have shown  $f_{max}$  superior to that of HBTs, and have dominated in MIMICs. With recent work on scaling of HBTs to submicron dimensions <sup>43</sup>, HBT power-gain cutoff frequencies now exceed those of HEMTs, and HBTs can compete for application in MIMICs.

In high-speed digital and mixed-signal applications, III-V HBTs must compete with their silicon counterparts. The primary advantage of III-V HBTs is superior bandwidth, and the primary disadvantage the relative immaturity of the technology, with consequently higher cost and lower scales of integration. There are several factors contributing to the superior bandwidth of III-V HBTs. For HBTs grown on GaAs or InP substrates, available lattice-matched materials allow use of an emitter whose bandgap energy is much larger than that of the base <sup>1</sup>. This allows the base doping to be increased to the limits of incorporation in growth,  $\sim 10^{20}/\mathrm{cm}^3$ , and results in very low base sheet resistance.  $600 \Omega/\text{square}$  sheet resistance and 0.15 psbase transit time is readily obtained in a Be-doped InGaAs base of 400 Å thickness. In contrast, constraints of allowable lattice mismatch in Si/SiGe HBTs limit the allowable Ge:Si alloy ratio. The emitter-base bandgap energy difference is then much smaller than in III-V HBTs, and base dopings are consequently lower. 4-8

$k\Omega$ /square base sheet resistivity is typical of SiGe HBTs <sup>13</sup>. High electron velocities are a second significant advantage of III-V HBTs. In InAlAs/InGaAs HBTs with  $0.2-0.3~\mu\mathrm{m}$  collector thickness, effective collector electron velocities exceed  $4\times10^7$ cm/s, approximately 4:1 higher than observed in Si. This high electron velocity results in high current-gain cutoff frequencies.

With the exception of transferred-substrate HBTs (discussed subsequently), best reported results of InP-based HBTs include 225 GHz  $f_{\tau}$  and 300 GHz  $f_{max}$  <sup>35</sup>, <sup>14</sup>. Si/SiGe HBTs  $^{10}$ ,  $^{11}$  have obtained 156 GHz  $f_{\tau}$ . Thus, despite the advantages of III-V HBTs provided by superior materials properties, Si bipolar junction transistors (BJTs) and Si/SiGe HBTs remain highly competitive. The high bandwidths of Si/SiGe HBTs arise in part from aggressive submicron scaling. In devices with  $0.14~\mu\mathrm{m}$  emitter-base junction widths, 92 GHz  $f_{\tau}$  and 108 GHz  $f_{max}$  have been reported <sup>12</sup>. Self-aligned polysilicon contacts reduce both the parasitic collectorbase capacitance and the base resistance. In marked contrast to the aggressive submicron scaling and aggressive parasitic reduction employed in Si/SiGe HBTs, III-V HBTs are typically fabricated with 1–2  $\mu$ m emitter junction widths and 3–5  $\mu$ m collector-base junction widths. This is remarkable in an era when commodity microprocessors are available with tens of millions of transistors at 0.13  $\mu$ m gate lengths. Deep submicron scaling will improve the bandwidth of III-V heterojunction bipolar transistors, and is critical to their continued success.

To obtain improved HBT bandwidths by scaling, transit times are reduced by decreasing the thicknesses of the base and collector epitaxial layers. Important RC charging times are reduced by laterally scaling the base and collector junction widths. Most significant among several limits to HBT submicron scaling is the extrinsic (parasitic) collector-base junction lying under the base Ohmic contacts. The required minimum size for the base Ohmic contacts places a lower limit on the size of the collector-base junction, preventing submicron junction scaling. We have developed a substrate transfer process which allows fabrication of HBTs with submicron emitter-base and collector-base junctions lying on opposing sides of the base epitaxial layer. With this device,  $f_{max}$  increases rapidly with scaling. With transferred-substrate HBTs, 1.1 THz extrapolated power-gain cutoff frequencies and 295 GHz current-gain cutoff frequencies have been obtained. Further improvements in  $f_{\tau}$  requires further epitaxial scaling, together with increased operating current density and greatly improved emitter parasitic resistance.

### 2. HBT scaling

In HBTs, thinning the base and collector epitaxial layers reduces the carrier transit times but increases the base resistance and the collector-base capacitance. These can be subsequently reduced by reducing the lithographically-defined widths of the emitter-base and collector-base junctions. To simultaneously obtain both high  $f_{\tau}$ and high  $f_{max}$ , device epitaxial and lithographic dimensions must be concurrently scaled. Below we examine the limits to HBT scaling.

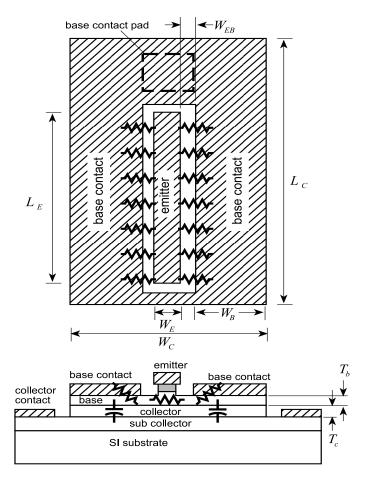

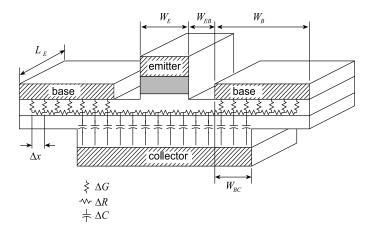

Figure 1 shows a simplified cross-section of a mesa HBT. To form the transis-

Figure 1: Plan and cross-section of a typical mesa HBT. The emitter-base junction has width  $W_e$ , length  $L_e$  and area  $A_e = L_e W_e$ , while the collector-base junction has width  $W_c$ , length  $L_c$  and area  $A_c = L_c W_c$

tor, the emitter, base, and collector layers first grown by molecular-beam epitaxy (MBE) or metal-organic chemical vapor deposition (MOCVD) on a semi-insulating substrate. The HBT junctions are formed by a series of patterned etches, and contacts formed by depositing metal. This results in a device structure where the collector-base junction must lie under the full area of the base Ohmic contacts. There is also a parasitic collector-base junction lying under the area of the base contact pad. In this device structure, the collector-base junction must be substantially larger than the emitter dimensions. At the sides of the emitter stripe, the base Ohmic contact must be at least one Ohmic contract transfer length  $L_{\rm contact}$  in order to obtain low contact resistance. In an InGaAs-base HBT with 400 Å base thickness and  $5 \times 10^{19}/\mathrm{cm}^3$  doping,  $L_{\mathrm{contact}} \simeq 0.4 \ \mu\mathrm{m}$ . Lithographic alignment tolerances between emitter and collector also constrain the minimum collector-base junction dimensions. Dependent upon the process minimum feature size and the length of the emitter stripe, the base contact pad area can contribute as much as 50 % of the total collector-base capacitance.

#### 2.1. Factors determining $f_{\tau}$

Before examining scaling for high cutoff frequencies, relevant HBT parameters must first be calculated. The current-gain cutoff frequency is

$$\frac{1}{2\pi f_{\tau}} = \tau_b + \tau_c + \frac{kT}{qI_c} \left( C_{je} + C_{cb} \right) + \left( R_{ex} + R_c \right) C_{cb}, \tag{1}$$

where  $R_{ex}$  and  $R_c$  are the parasitic emitter and collector resistances,  $C_{cb}$  is the collector junction capacitance, and  $I_c$  the collector current.

First examine the base transit time  $\tau_b$ . If a linear grading of the base semiconductor bandgap energy with position is used to reduce  $\tau_b$ , then <sup>15</sup>

$$\tau_b = \frac{T_b^2}{D_n} \left(\frac{kT}{\Delta E}\right) - \frac{T_b^2}{D_n} \left(\frac{kT}{\Delta E}\right)^2 \left(1 - e^{-\Delta E/kT}\right) + \frac{T_b}{v_{exit}} \left(\frac{kT}{\Delta E}\right) \left(1 - e^{-\Delta E/kT}\right) ,$$

(2)

where  $\Delta E$  is the grading in the base bandgap energy and  $T_b$  the base thickness. The base exit velocity  $v_{exit}$  is of the order of  $(kT/m^*)^{1/2}$  for an ungraded base <sup>15</sup>, and is somewhat larger with base bandgap grading.  $D_n$  is the base minority carrier diffusivity and  $m^*$  the electron effective mass. Equation 2 is derived from the driftdiffusion relationship, and is accurate only if the predicted  $\tau_b$  is large in comparison with the momentum relaxation time  $\tau_m = D_n m^* / kT^{16}$ . Using the parameters of an InGaAs base at  $5 \times 10^{19}/\text{cm}^3$  doping  $(D_n = 40 \text{ cm}^2/\text{sec}, v_{exit} \sim 3 \times 10^7 \text{ cm/s},$  $\tau_m{=}35$  fs), we note that 52 meV bandgap grading is sufficient to reduce  $\tau_b$  by  $\sim$ 2:1. For a thick base layer or a large  $v_{exit}$ ,  $\tau_b \propto T_b^2$ ; with InGaAs base layers below  $\sim 400$  Å thickness, the exit velocity term in eqn. 2 adds a significant correction.

The collector transit time  $\tau_c$  is the mean delay of the collector displacement current, and is given by <sup>17</sup>, <sup>18</sup>

$$\tau_c = \int_0^{T_c} \frac{(1 - x/T_c)}{v(x)} dx \equiv \frac{T_c}{2v_{\text{eff}}},\tag{3}$$

where v(x) is the position-dependent electron velocity in the collector drift region and  $v_{\rm eff}$  an effective electron velocity.  $\tau_c$  is most strongly dependent upon the electron velocity in the proximity of the base, and becomes progressively less sensitive to the electron velocity as the electron passes through the collector <sup>18</sup>. At low collector-base bias voltages, electrons must traverse a significant fraction of the collector drift region before acquiring sufficient kinetic energy (0.55 eV for InGaAs <sup>19</sup>, 0.6eV for InP <sup>20</sup>) to undergo  $\Gamma$ -L scattering <sup>17</sup>, <sup>18</sup>, and v(x) is fortuitously highest near the base. In thin InGaAs or InP layers,  $v_{\rm eff} = 3-5 \times 10^7$  cm/s. For scaling analysis, we will take  $\tau_c \propto T_c$ .

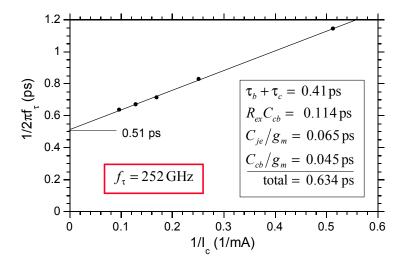

In InAlAs/InGaAs HBTs with  $T_b \cong 400$  Å and  $T_c \cong 0.2 \ \mu\text{m}$ ,  $f_\tau \simeq 250 \ \text{GHz}$ , and the RC charging terms in eqn. 1 comprise 35% of the total forward delay. These terms must be considered in detail.

First consider the charging time  $[kT/qI_c]C_{cb}$ . This term has a major impact upon digital circuit delay (section 3.1) and is reduced by increasing the collector current density to limits set by collector space-charge screening (the Kirk effect <sup>21</sup>). If the collector doping  $N_d$  is chosen so as to obtain a fully-depleted collector at zero bias current and the applied  $V_{cb}$ , we must have

$$V_{cb} + \phi = qN_d T_c^2 / 2\epsilon , \qquad (4)$$

while base pushout occurs at a current density  $J_{max}$  satisfying

$$V_{cb} + \phi = \left(J_{max}/v_{sat} - qN_d\right)T_c^2/2\epsilon , \qquad (5)$$

hence the maximum collector current before base pushout is

$$I_{c,max} = A_e(V_{cb} + \phi)4\epsilon v_{sat}/T_c^2 \propto A_e/T_c^2, \tag{6}$$

where  $v_{sat}$  is an (assumed) uniform electron velocity within the collector. With undoped collectors,  $I_{c,max}$  is 2:1 smaller than in eqn. 6. The collector capacitance is  $C_{cb} = \epsilon A_c/T_c$ . With the HBT biased at  $I_{c,max} \propto 1/T_c^2$ ,  $(kT/qI_C)C_{cb} \propto T_c$   $(A_c/A_e)$ . This delay term is thus minimized by scaling (reducing  $T_c$ ), but bias current densities must increase in proportion to the square of the desired fractional improvement in  $f_\tau$ .

The emitter charging time  $(C_{je}[kT/qI_c])$  in eqn. 1) is a significant determinant of  $f_{\tau}$ , and also plays a major role in ECL logic delay (section 3.1). If we were to assume that  $C_{je}$  were simply a depletion capacitance, it would be reasonable to expect that this charging time could be minimized simply by making the emitter-base depletion region very thick, by use of very low emitter doping, combined with a thick bandgap grading region in the base-emitter heterojunction. Clearly, this

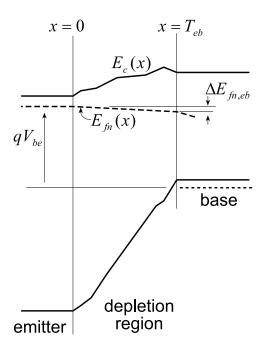

Figure 2: Band diagram of the HBT emitter-base junction. If the base-emitter junction thickness  $T_{eb}$  is excessive, HBT performance will be degraded by either stored charge or by excessive potential drops in the depletion layer.

approach must fail somehow in the limit of very large depletion thicknesses. We must examine design of the emitter-base junction in detail to determine the limits to the emitter-base depletion thickness, and to understand how the junction design must be modified as the transistor is scaled for increased device bandwidth.

In order to support a high emitter current density without a substantial potential drop in the emitter-base depletion layer, a high electron density n(x) must be present within the emitter-base junction. In high speed HBTs the thickness  $T_{eb}$  of the emitter-base depletion layer must then be small if significant charge storage effects are to be avoided. Figure 2 shows a band diagram of the base-emitter depletion region.  $n(x) = N_c \exp[-q(E_c(x) - E_{f,n}(x))/kT]$ , where  $N_c$  is the conduction band effective density of states,  $E_c(x)$  is the conduction-band energy and  $E_{f,n}(x)$  the electron quasi-Fermi level. An arbitrary conduction-band profile  $E_c(x)$  can be obtained through combined bandgap grading and doping. Under modulation of  $V_{be}$ ,  $\partial n(x)/\partial V_{be} = n(x)(q/kT)(x/T_{e,b})$ . The ideality factor N is defined by the relationship  $I_c \propto e^{qV_{be}/NkT}$ ; gradients in  $E_{fn}$  in the emitter-base depletion region result in N greater than unity, with

$$N = 1 + \frac{1}{q} \frac{\partial \left(\Delta E_{fn,eb}\right)}{\partial V_{be}} \ . \tag{7}$$

In the base-emitter depletion region,  $dE_{fn}/dx = -J/\mu_{n,eb}n(x)$ , while in the base  $J_n = qn(T_{eb})D_n/T_b\Gamma$ . Here,  $\mu_{n,eb}$  is the electron mobility in the junction (due to the low doping in the grade, this mobility is significantly larger than that of the base) and  $\Gamma = kT/\Delta E - (kT/\Delta E - D_n/v_{exit}T_b)e^{-\Delta E/kT}$  is a factor involving the base bandgap grading ( $\Gamma \simeq 1$  for an ungraded base). Combining these relationships, the ideality factor is

$$N = 1 + \frac{T_{eb}}{T_b} \frac{\mu_n}{\Gamma \mu_{n,eb}} \int_0^1 \frac{n(T_{eb})}{n(\zeta T_{eb})} (1 - \zeta) d\zeta,$$

(8)

Where  $\zeta = x/T_{eb}$  is a normalized position variable, and  $\mu_n$  is the electron mobility in the base. To obtain a low ideality factor,  $T_{eb}/T_b$  must not be large, and the electron density n(x) in the junction must be kept high. Unless  $T_{eb}/T_b$  is kept small, the high n(x) will result in significant charge storage. Using methods similar to those used to derive the collector transit time <sup>17</sup>, <sup>18</sup> (eqn. 3),

$$C_{je}/A_e = \epsilon/T_{eb} + \frac{\partial}{\partial V_{be}} \left[ \int_0^{T_{eb}} (x/T_{eb}) \, qn(x) dx \right]. \tag{9}$$

The term  $(kT/qI_c)C_{je}$  in eqn. 1 can be then written as

$$(kT/qI_c)C_{je} = \left(\frac{\epsilon A_e}{T_{eb}}\right) \left(\frac{kT}{qI_c}\right) + \frac{\Gamma T_{eb}T_b}{D_n} \int_0^1 \frac{n(\zeta T_{eb})}{n(T_{eb})} \zeta^2 d\zeta.$$

$$(10)$$

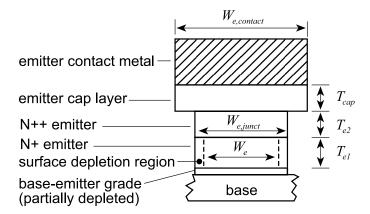

Figure 3: Cross-section of the emitter layers within a typical HBT, comprising an a heavily-doped semiconductor contact ("cap") layer, a low-resistance N++ emitter layer, and the N+ emitter. Lateral depletion of the N+ emitter can be significant in submicron devices.

The first term in eqn. 10 results from the depletion-layer capacitance, and is minimized using high bias current densities  $J_e = I_e/A_e$ ; the second term reflects storage of mobile electron charge within the depletion layer, and is minimized by reducing  $T_{eb}T_b$ .

In eqn. 1, the delay term  $R_{ex}C_{cb}$  is a major limit to HBT scaling for high  $f_{\tau}$ . Further,  $R_{ex}$  contributes significantly to ECL logic delay. Because of the relative sizes of the emitter and collector Ohmic contacts, in a well-designed submicron HBT,  $R_c$  is 4:1 to 10:1 smaller than  $R_{ex}$  and  $R_cC_{cb}$  can be neglected in a first analysis.  $R_{ex}$  must first be calculated. The emitter layer structure of a typical HBT (fig. 3) contains a heavily-doped and narrow-bandgap contact ("cap") layer, and a heavily-doped N++ wide-bandgap emitter layer. A portion of the emitter layer may be more lightly (N+) doped for reduced junction capacitance, and may be of several hundred A thickness to avoid dopant diffusion from the N++ layer into the emitter-base junction. If heterointerfaces are properly graded to avoid conduction-band barriers between layers, the parasitic emitter resistance is

$$R_{ex} = \rho_{c,e}/L_eW_{e,contact} + \rho_{cap}T_{cap}/L_eW_{e,contact} + \rho_{e2}T_{e2}/L_eW_{e,junct} + \rho_{e1}T_{e1}/L_eW_e,$$

(11)

where  $\rho_{c,e}$  is the emitter specific Ohmic contact resistivity, and  $\rho_{cap}$ ,  $\rho_{e2}$ , and  $\rho_{e1}$ are the bulk resistivities of the cap, N++, and N+ emitter layers. For submicron emitters, the junction width  $W_{e,junct}$  is significantly smaller than the contact width We,contact due to lateral undercutting of the emitter during etching of the emitterbase junction, and the electrically-active emitter width  $W_e$  can be significantly smaller than  $W_{e,junct}$  because of the presence of surface (edge) depletion regions of width  $(2\epsilon\phi/qN_{e1})^{1/2}$ , where  $N_{e1}$  is the N+ layer doping and  $\phi$  is the bandbending due to pinning of the Fermi energy at the surface. For simplicity in scaling analysis, we will approximate

$$R_{ex} \simeq \rho_e / A_e \tag{12}$$

where  $\rho_e$  is a fitted parameter, approximately  $50\Omega - \mu \text{m}^2$  for submicron InAlAs/InGaAs HBTs fabricated to date at UCSB. In InAlAs/InGaAs HBTs we have fabricated,  $\rho_{c,e} = 20\Omega - \mu \text{m}^2$  when InGaAs contacts at  $10^{19}/\text{cm}^3$  doping are employed, and  $\rho_{c,e} = 4\Omega - \mu \text{m}^2$  for contacts to InAs layers at  $2 \times 10^{19}/\text{cm}^3$  doping. The  $\rho_{e1}T_{e1} = 5.5\Omega - \mu \text{m}^2$  resistance of the N+ InAlAs layer (8 ×  $10^{17}/\text{cm}^3$  doping, 700 Å thickness) is significant in submicron devices for which  $W_e$  is 2:1 to 4:1 smaller than  $W_{e,contact}$ . To avoid such emitter size effects, deep submicron HBTs should use  $\gg 10^{18}/\text{cm}^3$  emitter doping.

The  $R_{ex}C_{cb}$  charging time can now be examined. Since  $C_{cb} = \epsilon A_c/T_c$ ,

$$R_{ex}C_{cb} = \left(\frac{\epsilon\rho_e}{T_c}\right)\left(\frac{A_c}{A_e}\right) = 28 \text{ fs} \times \left(\frac{A_c}{A_e}\right),$$

(13)

if  $\rho_e = 50~\Omega - \mu \mathrm{m}^2$  and  $T_c = 0.2~\mu \mathrm{m}$ . This a significant delay. In HBTs we have fabricated with 275 GHz peak  $f_{\tau}$ , the substrate transfer process allows  $A_c/A_e$  to be kept small at 2.3:1, yet  $R_{ex}C_{cb}$  still constitutes 11% of the total  $1/2\pi f_{\tau} = 0.58$  ps forward delay. In mesa HBTs (fig. 1)  $A_c/A_e$  is often larger than 2.3:1 and hence  $R_{ex}C_{cb}$  will contribute a larger delay. Because  $R_{ex}C_{cb} \propto 1/T_c$ , thinning the collector to reduce  $\tau_c$  also increases  $R_{ex}C_{cb}$ .

To increase HBT current gain cutoff frequencies, the base and collector layers must be thinned and the bias current density increased. Thinning the collector increases  $R_{ex}C_{cb}$ , imposing a limit to scaling. Limits to bias current density imposed by device reliability, and loss in breakdown voltage with reduced collector thickness, are two further potential limits to scaling. Finally, unless the device structure of fig. 1 is laterally scaled, vertical HBT scaling for increased  $f_{\tau}$  will result in reduced power-gain cutoff frequencies  $f_{max}$ .

#### **2.2.** Lithographic scaling for high $f_{max}$

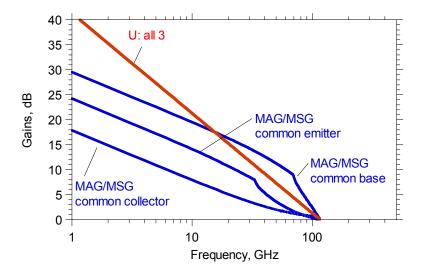

Regardless of the value of  $f_{\tau}$ , transistors cannot provide power gain at frequencies above  $f_{max}$ . Independent of  $f_{\tau}$ ,  $f_{max}$  defines the maximum usable frequency of a transistor in either narrowband reactively-tuned or broadband distributed circuits  $^{22}$ . In more general analog and digital circuits (section 3.1), all transistor parasitics play a significant role. The  $f_{\tau}$  and  $f_{max}$  of a transistor are then cited to give a first-order summary of the device transit delays and of the magnitude of its dominant parasitics.

In an HBT with base resistance  $R_{bb}$  and collector capacitance  $C_{cb}$ , the power-gain cutoff frequency is approximately  $f_{max} \simeq (f_{\tau}/8\pi R_{bb}C_{cbi})^{1/2}$ . The base-collector junction is a distributed network, and  $R_{bb}C_{cbi}$  represents an effective, weighted time constant.

The base resistance (fig. 1)  $R_{bb}$  is composed of the sum of contact resistance  $R_c$ , base-emitter gap resistance  $R_{qap}$ , and spreading resistance under the emitter  $R_{spread}$ . With base sheet resistance  $\rho_s$ , and specific (vertical) contact access resistance  $\rho_c$ , we have

$$R_{bb} = R_{b,cont} + R_{gap} + R_{spread}$$

$$R_{b,cont} = \sqrt{\rho_s \rho_c} / 2L_e$$

$$R_{gap} = \rho_s W_{eb} / 2L_e$$

$$R_{spread} = \rho_s W_e / 12L_e.$$

(14)

To compute  $f_{max}$ , we must find  $C_{cbi}$ . Because the base-collector junction parasitics are distributed, calculation of  $R_{bb}C_{cbi}$  is complex, and will be deferred until section 2.3. As a first (and very rough) approximation, we will first compute  $R_{bb}C_{cb}$ , e.g. the product of the base resistance and the full capacitance  $C_{cb} = \epsilon A_c/T_c$  of the collector-base junction,

$$R_{bb}C_{cb} = \left[ \left( \sqrt{\rho_s \rho_c} + \rho_s W_{eb} \right) \left( \frac{\epsilon}{2} \right) \left( \frac{L_c}{L_e} \right) \right] \left[ \frac{W_c}{T_c} \right] + \left[ \left( \frac{\rho_s \epsilon}{12} \right) \left( \frac{L_c}{L_e} \right) \right] \left[ \frac{W_c W_e}{T_c} \right].$$

(15)

Consider the influence of device scaling on the time constant  $R_{bb}C_{cb}$ . Decreasing the base thickness to reduce  $\tau_b$  increases the base sheet resistivity  $\rho_c$ , increasing  $R_{bb}C_{cb}$ . Decreasing the collector thickness  $T_c$  to reduce  $\tau_c$  directly increases  $R_{bb}C_{cb}$ , as is shown explicitly in eqn. 15.

Low  $R_{bb}C_{cb}$ , and consequently high  $f_{max}$ , is obtained by scaling the emitter and collector junction widths  $W_e$  and  $W_c$  to submicron dimensions. Reducing the emitter width  $W_e$  alone reduces towards zero the component of  $R_{bb}C_{cb}$  associated with the base spreading resistance (the second term in eqn. 15). In the normal triple-mesa HBT (fig. 1), the base Ohmic contacts must be at least one contact transfer length  $(L_{\text{contact}} = (\rho_c/\rho_s)^{1/2})$ , setting a minimum collector junction width  $W_c$ . The component of  $R_{bb}C_{cb}$  associated with the base contact resistance (the first term in eqn. 15) has a minimum value, independent of lithographic limits. Consequently,  $f_{\text{max}}$  does not increase rapidly with scaling. Given this minimum  $R_{bb}C_{cb}$ , attempts to obtain high  $f_{\tau}$  by thinning the collector have resulted in decreased  $f_{max}$ , frustrating efforts to improve HBT bandwidths.

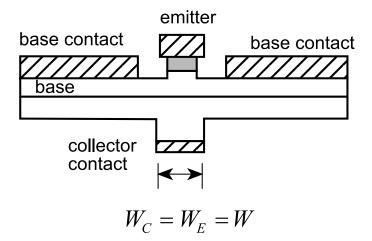

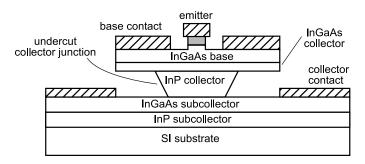

If the parasitic collector-base junction is eliminated,  $f_{max}$  will instead increase rapidly with scaling. The collector-base junction need only be present where current flows, e.g. under the emitter. We have fabricated such a device (figure 4) using substrate transfer processes. The emitter and collector junctions can be of equal

Figure 4: Cross-section of an idealized HBT with the collector-base junction lying only under the emitter. Such device structures can be formed using substrate transfer processes.

width, hence  $W_c = W_e$ . The base-collector time constant becomes

$$R_{bb}C_{cb} = \left[ \left( \sqrt{\rho_s \rho_c} + \rho_s W_{eb} \right) \left( \frac{\epsilon}{2} \right) \left( \frac{L_c}{L_e} \right) \right] \left[ \frac{W_e}{T_c} \right]$$

$$+ \left[ \left( \frac{\rho_s \epsilon}{12} \right) \left( \frac{L_c}{L_e} \right) \right] \left[ \frac{W_e^2}{T_c} \right].$$

(16)

With submicron scaling of the emitter and collector junction widths, the first term in eqn. 16 dominates, and  $f_{max}$  increases as the inverse square root of the process minimum feature size.

Figure 5: Distributed model of the HBT base-collector junction for accurate calculation of  $R_{bb}C_{cbi}$ . With mesh spacing  $\Delta x$ ,  $\Delta G = L_e\Delta x/\rho_c$ ,  $\Delta R = \rho_s\Delta x/L_e$ , and  $\Delta C = \epsilon L_e \Delta x / T_c$

## 2.3. Secondary Effects in $f_{max}$

The formulas developed above are highly simplified and significantly underestimate the HBT  $f_{max}$ . Two significant corrections must be applied. First, the simple lumped RC model of the base-collector junction must be re-examined. Secondly, differential space-charge effects substantially reduce the collector-base capacitance under high-current conditions.

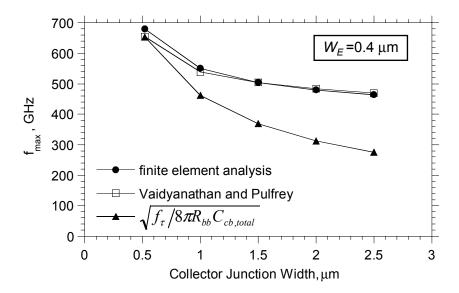

The HBT base-collector network is distributed, and is represented by the model of fig. 5. Using a small grid spacing, we have entered the resulting network into a microwave circuit simulator (HP-EESOF <sup>23</sup>) to calculate –without approximation– the HBT  $f_{max}$ . Alternatively, analytic expressions for  $f_{max}$  can be developed from hand analysis of the distributed network of fig. 5. Among these is the model of Vaidyanathan and Pulfrey <sup>24</sup>, which provides good physical insight. The model of reference <sup>24</sup> is derived for a triple-mesa HBT; the authors of <sup>25</sup> have recently generalized the model to the case of transferred-substrate and lateral-etched-undercut collector <sup>30</sup> HBTs. We describe the Vaidyanathan / Pulfrey model below, and examine its predicted performance for HBTs with submicron emitter and collector junction widths.

Referring to fig. 5, define three capacitances.  $C_{cb,e} = \epsilon L_e W_e / T_c$  is the capacitance of the collector junction lying under the emitter.  $C_{cb,gap} = 2\epsilon L_e W_{eb}/T_c$  is the capacitance of the collector junction lying under the gap between the emitter and the base contact.  $C_{cb,ext} = 2\epsilon L_e W_{cb}/T_c$  is the capacitance of the collector lying under the base Ohmic contacts. Components of the base resistance are as defined in eqn. 14.

The collector-base capacitance under the emitter stripe  $C_{cb,e}$  is charged through a resistance  $(R_{b,cont} + R_{gap} + R_{spread})$ . The collector-base capacitance under the gap between the emitter and the base Ohmic contacts is charged through a resistance  $(R_{b,cont} + R_{gap}/2)$ .

The charging time constant associated with the collector-base junction capacitance  $C_{cb,ext}$  lying under the base Ohmics requires more detailed scrutiny.  $C_{cb,ext}$  can be charged by currents passing vertically through the base Ohmic contact above it; this path has a resistance  $R_{b,cont,1} = \rho_c/2L_eW_{cb}$ . Alternatively,  $C_{cb,ext}$  can be charged by currents passing laterally from the base contact region lying outside the perimeter of the collector contact; this path has a resistance  $R_{b,cont,0} = (\rho_s \rho_c)^{1/2} \coth((W_b - W_{bc})/L_{contact})$ , where  $L_{contact} = (\rho_c/\rho_s)^{1/2}$  is the base Ohmic contact transfer length.

In the limit of zero collector series resistance, Vaidyanathan and Pulfrey's model,  $^{24},\,^{25}$  reduces to

$$f_{max} = \sqrt{\frac{f_{\tau}'}{8\pi\tau_{cb}}},\tag{17}$$

where

$$\frac{1}{2\pi f_{\tau}'} = \tau_b + \tau_c + \frac{kT}{qI_c} (C_{je} + C_{cb}), \tag{18}$$

and

$$\tau_{cb} = C_{cb,e} \left( R_{b,cont} + R_{gap} + R_{spread} \right)$$

$$+ C_{cb,gap} \left( R_{b,cont} + R_{gap} / 2 \right)$$

$$+ \left( R_{b,cont,0} \| R_{b,cont,1} \right) C_{cb,ext}$$

$$(19)$$

Examining figure 5, the external collector capacitance  $C_{cb,ext}$  is not charged through the resistances  $R_{gap}$  and  $R_{spread}$ . It is pessimistic to calculate  $f_{max}$  as  $(f_{\tau}/8\pi R_{bb}C_{cb})^{1/2}$  in which the collector-base time constant includes the full collector-base capacitance. As indicated by Vaidyanathan and Pulfrey's model (eqn. 17), the external collector capacitance  $C_{cb,ext}$  is in fact charged through a smaller associated resistance  $(R_{b,cont,0}||R_{b,cont,1})$ . This model shows extremely good agreement with finite-element analysis (fig. 6).

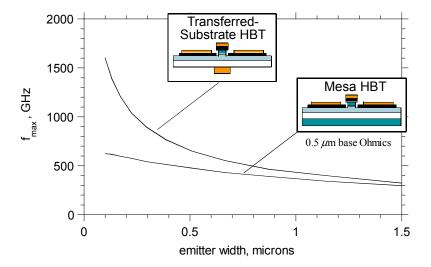

Figure 7 compares the  $f_{max}$  of mesa and transferred-substrate HBTs, computed using the finite-element model. For the transferred-substrate device,  $f_{max}$  increases rapidly with deep submicron scaling. Experimentally, we observe a more rapid variation of  $f_{max}$  with collector width than is shown in fig. 6, and fig. 7 predicts a higher  $f_{max}$  than is experimentally observed for mesa HBTs. Series resistance in the base metallization and collector series resistance  $^{24}$  (not modeled above, and not present in Schottky-collector transferred-substrate HBTs) are possible explanations for the discrepancy.

At high collector current densities, differential space-charge effects in the collector space-charge region result in  $C_{cb}$  smaller than  $\epsilon A_c/T_c$ , and increase the HBT  $f_{max}$ . The effect was predicted by Camnitz and Moll <sup>27</sup>, and first experimentally observed by Betser and Ritter <sup>26</sup>. Similar effects have been observed in MESFETs

Figure 6: Comparison of  $f_{max}$  computed from a finite element model with Vaidyanathan and Pulfrey's model (Eqn.. 17) and a model using the total collector junction capacitance (Eqn. 15). Except for  $W_c$ , the modeled HBT is that of figure 19, and has  $W_e = 0.4 \ \mu \text{m}$ .

Figure 7: Lithographic scaling of transferred-substrate and mesa HBTs.  $f_{max}$  is calculated using fig. 5's finite-element model of the collector-base junction. Except for  $W_c$  and  $W_e$ , the HBT parameters are taken from the device of fig. 19. Current density and epitaxial layer thicknesses are held constant, resulting in constant  $f_{\tau}$

Figure 8: HBT with an undercut collector-base junction formed by selective etching of the InP collector in HCl

<sup>28</sup>. In III-V materials at high fields, electron velocity  $v(\mathcal{E})$  decreases with increasing electric field. To a first approximation,  $1/v(\mathcal{E}) \simeq \kappa_0 + \kappa_1 \mathcal{E}$ . Modulating the collector voltage  $V_{cb}$  modulates the collector transit time  $\tau_c$  (eqn. 3), and partially modulates the space-charge in the collector drift region. This modulated space-charge partially screens the base from modulations in the collector applied field, and  $C_{cb,e}$ is reduced to

$$C_{cb,e} = \epsilon A_e / T_c - I_c \frac{d\tau_c}{dV_{cb}}$$

$$= \frac{\epsilon A_e}{T_c} - \frac{\kappa_1 J_c A_e}{2} \left[ 1 - \frac{\kappa_1 J_c T_c}{6\epsilon} \right], \tag{20}$$

The quadratic dependence upon  $J_c$  results from internal collector field redistribution in the presence of the collector space-charge <sup>27</sup>. Current spreads laterally during transport through the collector, flowing through a region of width  $\sim (W_e + T_c)$ . The differential space charge effect strongly reduces the collector junction capacitance in regions below and adjacent to the emitter stripe. It thus has the strongest impact upon  $f_{max}$  in devices with minimal excess collector capacitance. Experimental data confirming  $C_{cb}$  cancellation will be shown in section 4.2. Capacitance cancellation is not instantaneous, but instead arises after a delay proportional to  $\tau_c$ ; HBT power gain must therefore increase at -40 dB/decade for frequencies above  $\sim 1/2\pi\tau_c$ . The effect can produce a  $\sim 2:1$  increase in  $f_{max}$ , hence a large increase in the attainable gain of tuned millimeter-wave amplifiers. In contrast, in digital circuits (section 3.1), many delay terms are significant, and a 2:1 reduction in  $C_{cbi}$  would produce only a  $\sim 12\%$  decrease in gate delay.

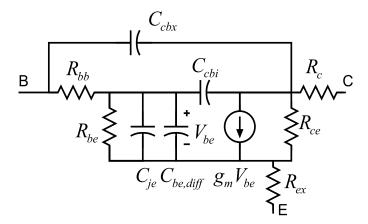

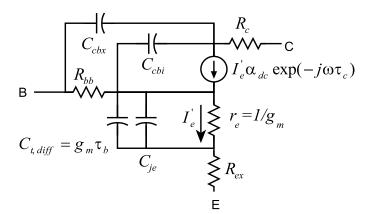

Figure 9: Hybrid- $\pi$  small-signal HBT equivalent circuit.  $C_{be, \text{diff}} = g_m(\tau_b + \tau_c)$ . The element  $C_{cbi}$  does not represent capacitance of that fraction of the collector junction lying under the emitter, but is instead a parameter adjusted to obtain the correct  $f_{max}$ .

#### 2.4. HBT equivalent circuit model

The HBT base-collector network is distributed, and accurate expressions for  $f_{max}$  are complex. Computer simulation of complex circuits requires a compact device model. Under small-signal operation, the Gummel-Poon model used in SPICE reduces to the simple hybrid- $\pi$  model of figure 9. For this model,  $f_{max} = (f_{\tau}/8\pi R_{bb}C_{cbi})^{1/2}$ . It should be emphasized that  $C_{cbi}$  corresponds to no particular physical area in the collector-base junction. Specifically  $C_{cbi}$  is not equal  $C_{cb,e}$ , the capacitance of that fraction of the collector junction which lies under the emitter. Instead, in this model  $R_{bb}$  is given by eqn. 14,  $(C_{cbx} + C_{cbi}) = \epsilon A_c/T_c$ , and the intrinsic collector-base capacitance is set to  $C_{cbi} = \tau_{cb}/R_{bb}$ , where  $\tau_{cb}$  is given by eqn. 19. Thus  $C_{cbi}$  is defined to be so that the simplified model predicts the correct device  $f_{max}$ . To correctly model common-base and emitter-follower input impedance at  $f \simeq f_{\tau}$ , the transconductance element must have an associated delay of  $\sim (\tau_c + \zeta \tau_b)$ , where the factor  $\zeta \simeq 0.1$ –0.2 is dependent upon the degree of base bandgap grading.

## 2.5. High $f_{max}$ HBT designs

To obtain simultaneous high values of  $f_{\tau}$  and  $f_{max}$  the emitter and collector stripe widths must both be scaled. The substrate transfer process is an extremely aggressive method of reducing the parasitic extrinsic collector-base junctions, and requires a substantial departure from typical fabrication processes. There are alternatives requiring less radical processing. With GaAs/AlGaAs HBTs <sup>29</sup> deep proton implantation can reduce the extrinsic collector capacitance. The extrinsic collector junction can be undercut using selective wet chemical etches (fig. 8) <sup>30</sup>, <sup>31</sup>. Collector capacitance under the base contact pad can be reduced using dielectric spacer

layers  $^{32}$ . Alternatively,  $R_{bb}$  can be reduced by regrowing, prior to base contact deposition, thick extrinsic P+ contact regions on the exposed base surface <sup>33</sup>, <sup>34</sup>. Finally, low  $R_{bb}C_{cbi}$  can be obtained in mesa HBTs by reducing the size of the base Ohmic contacts. Using a CBr<sub>4</sub> doping source, we have grown by MBE InGaAs base layers with  $> 10^{20}/\mathrm{cm}^3$  carbon (P-type) doping. At such doping levels,  $\rho_c$  and hence the transfer length  $L_{\rm contact} = (\rho_c/\rho_s)^{1/2}$  are greatly reduced. The width of the base Ohmic contacts can be accordingly reduced.

#### 3. HBT Digital Integrated Circuits

$f_{\tau}$  and  $f_{max}$  of scaled InP-based HBTs are significantly higher than Si/SiGe HBTs. Consequently, tuned and broadband amplifiers using InP-based HBTs show substantially higher bandwidths than those implemented in Si/SiGe <sup>36</sup>, <sup>37</sup>, <sup>38</sup>. Yet, in digital circuits the 2 competing technologies have held a rough parity for the past 3-4 years. Since analog/digital mixed-signal ICs (fiber optic transmission ICs, ADCs, DACs) are major HBT applications, we must examine in detail the relationship between logic gate delay and HBT design and scaling. The reader is also referred to gate delay analyes by Sano et. al. 49, and Enoki et. al. 50. General methods of digital circuit delay analysis are discussed in Hodges and Jackson <sup>51</sup>.

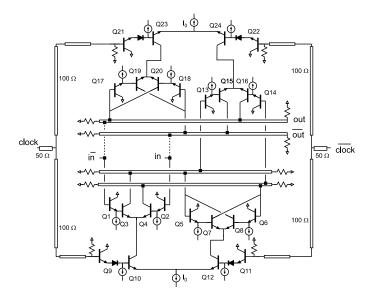

We compute below, as a function of HBT parameters, the maximum clock rate of an ECL master-slave (M/S) latch. M/S latches serve as timing control elements in digital ICs, as latched comparators in ADCs, and as decision circuits in fiber optic receivers. To benchmark their maximum clock frequency, M/S latches are configured as 2:1 static frequency dividers. It is important to distinguish between the maximum clock frequency of M/S latches configured as static dividers with that of dynamic 2:1 frequency dividers, which operate significantly higher clock frequencies, but have more restricted applications.

### 3.1. Digital delay analysis

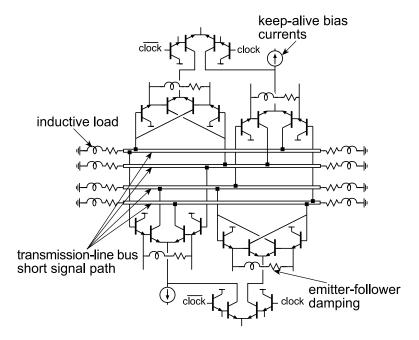

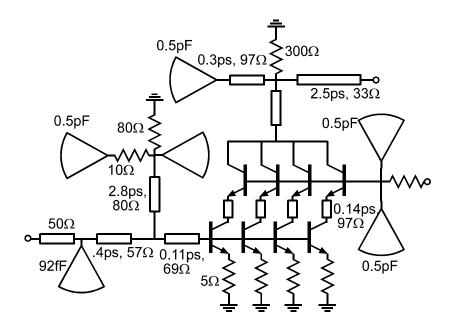

A schematic diagram of an ECL MS latch is shown in fig. 10. The master latch has input stage Q1-4 and latch Q5-8, while the slave latch has input stage Q13-16 and latch Q17-20. The clock current is steered by Q9-12 and Q21-24. In our designs, signals between gates are routed on the collector nodes, using 100  $\Omega$  transmission lines terminated at sending and receiving ends in 100  $\Omega$ .

A logic voltage swing  $\Delta V_L$  must be specified. Gate delay will vary with  $\Delta V_L$ , but a minimum  $\Delta V_L$  is necessary for adequate DC noise margin hence proper logic operation. In order for the differential pairs Q3-4 to properly steer the current of Q9, the difference in the internal  $V_{be}$  of the two transistors should be several times kT/q. As a first assumption, we set  $\Delta V_{be,int} \sim 6kT/q$ ; this results in a  $e^6$ :1 ratio between the currents in the on and off states. In the presence of parasitic emitter resistance  $R_{ex}$ , the logic swing required for at least an  $e^6$ :1 current switching ratio is to

$$\Delta V_L \ge 6kT/q + I_0 R_{ex} = 6kT/q + J_0 \rho_e$$

, (21)

Figure 10: ECL master-slave flip-flop. The current sources are implemented with current mirrors. Except where marked, all resistors and transmission-line impedances are 100  $\Omega$ . Dotted lines indicate connections for a static 2:1 frequency divider.

where  $I_0$  is the switched current,  $J_0$  the emitter current density and  $\rho_e$  the emitter resistance normalized to a unit emitter junction area.

We compute, approximately, the gate delay using the charge control method, adding the charging times of each node associated with the signal path. The node charging time from the initial state to the (50%) switching point is  $\Delta t \simeq \Delta Q/2I$ , where  $\Delta Q$  is the switched charge, and I the charging current <sup>51</sup>, <sup>52</sup>. This is equivalent to analysis of a linearized version of the digital circuit, in which node impedances are modeled by  $R = \Delta V/\Delta I$ ,  $C = \Delta Q/\Delta V$ , and  $g_m = \Delta I_c/\Delta V_{be}$  51. Gain effects varying to second order in  $(j\omega)$  in the circuit transfer function are neglected; this simplifying assumption introduces significant error by ignoring the effect of emitter-follower ringing.

We assume a current density  $J_0$  in the upper-level current-switch HBTs and a current density  $J_0/2$  for all emitter followers and for the lower-level clock-steering current-switch HBTs. The upper-level differential current-switch transistors have emitter areas  $A_{e,cs}$ , the lower-level (clock switching) current-switch transistors have emitter areas  $2 \cdot A_{e,cs}$ , and the emitter followers have emitter areas  $A_{e,ef}$ . The currents that flow in these devices are therefore  $I_0 = J_0 A_{e,cs}$ ,  $I_0 = (J_0/2)(2A_{e,cs})$ , and  $I_{0,E} = (J_0/2)A_{e,ef}$  respectively. The base-emitter voltage in the on-stage is denoted as  $V_{be,on}$ . For simplicity, we assume a digital voltage swing  $\Delta V_L$  at all upper-level collector nodes, although it is known that decreased MS latch delay can be obtained by using smaller switched currents (hence smaller  $\Delta V_L$ ) during

Figure 11: Simplified HBT common-base (T) equivalent circuit model used in the logic delay analysis. Note that  $\tau_b$  is modeled as a diffusion capacitance while  $\tau_c$  is modeled as a transport delay.

operation of the positive-feedback latch).

The large-signal base-emitter depletion capacitance is defined as  $C_{je} = c_{je} * A_e$ , where the average capacitance per unit emitter area is

$$c_{je} \equiv \frac{\Delta Q}{\Delta V} = \frac{1}{\Delta V} \int_{V_{be,on} - \Delta V}^{V_{be,on}} c_{je}(V) dV . \qquad (22)$$

The base-collector capacitance  $C_{cb} = c_{cb} * A_e$  is taken as proportional to the emitter area (thus assuming a fixed emitter-collector area ratio). The collector-base junction is fully depleted and operates at current densities below that causing base pushout. In the hybrid- $\pi$  model (fig. 9), the large-signal base-emitter diffusion capacitance is  $C_{be,\text{diff}} = I_0(\tau_b + \tau_c)/\Delta V$ . For common-base switching paths the T-model (fig. 11) is employed; for that model, the base-emitter junction has a small-signal diffusion capacitance  $C_{\rm t,diff} = g_m \tau_b$ , while under large signal drive the capacitance becomes  $\tau_b I_c/\Delta V_L$ .

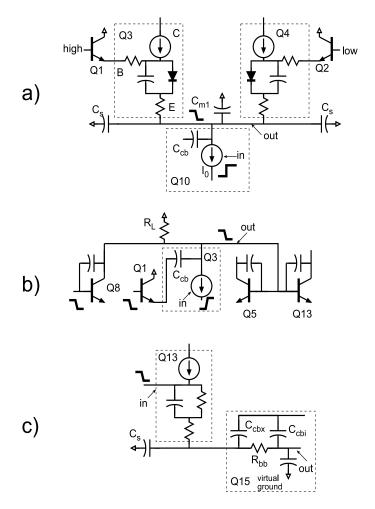

Assume that the bases of Q1 and Q17 are at a logic high while the bases of Q2 and Q18 are at a logic low. At t = 0 the clock rises from low to high. The clock differential pair Q10/Q12 changes state, establishing after a propagation delay a collector current  $I_0$  in Q10. The current  $I_0$  then charges the capacitances at the emitter node of Q3, driving the node negative until Q3 turns on (fig. 12a). After a propagation delay through Q3,  $I_0$  is established as a collector current for Q3. The current  $I_0$  then charges the capacitances at the collector node of Q3, driving the node negative with an charging time resulting from the node capacitances (fig. 12b). Finally (fig. 12c), the emitter followers (Q5,6,13,14) charge/discharge the base-emitter junctions of the master-stage latch current-steering pair (Q7,8) and the slave-stage input current-steering pair (Q15,16), with delay arising both from the emitter-followers and from the (Q7,8,15,16) base-emitter junction charging through  $R_{bb}$  Once this sequence is complete, the clock can change states and the sequence repeats itself in the slave stage. Note that the delays associated with the clock differential pairs occur both in the master and in the slave and therefore, to a first approximation, do not affect the maximum clock frequency.

We first calculate the switching delay at the emitter of Q3 (fig 12.a). Q10 is turned on at t = 0. Q10 and Q3 are in series, and have equal on-state and off-state emitter currents. The logic voltage swings at the base-emitter junctions of Q10 and Q3 must therefore be identical, with  $V_{be,on} - V_{be,off} = \Delta V_L = I_0 R_L$  for both transistors. Further, note that over the logic transition  $C_{je3}$  sees a voltage swing of  $\Delta V_L - I_0 R_{ex3} = I_0 (R_L - R_{ex3})$ , while  $C_{cb10}$  sees a voltage swing of  $2 \cdot \Delta V_L$ . There is interconnect capacitance  $C_{m1}$  at the node; further Q3 and Q4 have substrate capacitances  $C_{s,3}$  and  $C_{s,4}$ . The node charging time is

$$\begin{split} T_{\text{Q3emitter}} &= \Delta V_L \left( \frac{C_{s3} + C_{s4} + C_{m1} + 2C_{cb10} + C_{je4}}{2I_0} \right) \\ &+ (\Delta V_L - I_0 R_{ex3}) \left( \frac{C_{je3}}{2I_0} \right) + \tau_b \\ T_{\text{Q3emitter}} &= \Delta V_L \left( \frac{2c_s + C_{m1}/A_{e,cs} + 4c_{cb} + c_{je}}{2J_0} \right) \\ &+ (\Delta V_L - J_0 \rho_e) \left( \frac{c_{je}}{2J_0} \right) + \tau_b \;, \end{split} \tag{23}$$

where the latter form is written using currents, capacitances and resistances normalized to a unit HBT emitter junction area ( $\rho_e = R_{ex}A_e$ ,  $r_{bb} = R_{bb}A_e$ ).

Second, we calculate the delay between the emitter and collector of Q3 (fig 12,b). Q3 operates in common-base mode, and its  $g_m$  element has delay  $\tau_c$ . Capacitances  $C_{cb8}$  and  $C_{cb3}$  undergo a  $2\Delta V_L$  voltage swing; other capacitances undergo a swing of  $\Delta V_L$ . Adding collector transmission-line bus delay  $\tau_{bus}$  (fig. 10), the node delay at the collector of Q3 is

$$T_{\text{Q3coll}} = \tau_c + \tau_{bus} + \Delta V_L \left( \frac{2C_{cb8} + 2C_{cb3} + C_{cb5} + C_{cb13}}{2I_0} \right) T_{\text{Q3coll}} = \tau_c + \tau_{bus} + \Delta V_L \left( \frac{(4 + 2A_{e,ef}/A_{e,cs})c_{cb}}{2J_0} \right) .$$

(24)

Finally, we calculate the delay between the voltage transition at the collector of Q3 and the base (internal to  $R_{bb}$ ) of Q15 (fig 12,c). In the figure, the emitter follower is represented by a T-model and the current-steering device by a partial hybrid- $\pi$  model. The emitter followers Q6 and Q14, simultaneously undergoing a negative-going transition, are explicitly assumed to remain on during the switching event; this stipulates a minimum  $(A_{e,ef}/A_{e,cs})$  area ratio, and always-on operation must be verified during design. The bias current in Q7,8 and Q15,16 must be

Figure 12: Equivalent circuit of the nodes in the signal path for calculating the  $\rm M/S$ latch delay. Charging of the emitter node of Q3 (a). Charging of the collector node of Q3 (b). Charging of the base of the switching transistor Q15 (c).

Table 1: Delay coefficients  $a_{ij}$ , found by hand analysis, assuming gate delay of form  $T_{gate} = 1/2 f_{clock} = \sum a_{ij} r_i c_j$ .

|                  | $c_{je}$ | $c_{cbx}$ | $c_{cbi}$ | $c_s$ | $\frac{C_{m1}}{A_{e,cs}}$ | $\frac{\tau_f J_0}{\Delta V_L}$ | $\frac{\tau_{bus}J_0}{\Delta V_L}$ |

|------------------|----------|-----------|-----------|-------|---------------------------|---------------------------------|------------------------------------|

| $\Delta V_L/J_0$ | 1        | 6         | 6         | 1     | 0.5                       | 1                               | 1                                  |

| $kT/qJ_0$        | 0.5      | 1         | 1         | 0.5   | 0                         | 0.5                             | 0                                  |

| $ ho_e$          | -0.25    | 0.5       | 0.5       | 0.5   | 0                         | 0.5                             | 0                                  |

| $r_{bb}$         | 0.5      | 0         | 1         | 0     | 0                         | 0.5                             | 0                                  |

Table 2: Delay coefficients  $a_{ij}$ , found by SPICE, assuming gate delay of form  $T_{gate} =$  $1/2f_{clock} = \sum a_{ij}r_ic_j.$

|                  | $c_{je}$ | $c_{cbx}$ | $c_{cbi}$ | $c_s$ | $\frac{C_{m1}}{A_{e,cs}}$ | $\frac{\tau_f J_0}{\Delta V_L}$ | $\frac{\tau_{bus}J_0}{\Delta V_L}$ |

|------------------|----------|-----------|-----------|-------|---------------------------|---------------------------------|------------------------------------|

| $\Delta V_L/J_0$ | 0.8      | 4.3       | 4.3       | 1.9   | 0.7                       | 1.6                             | 1                                  |

| $ ho_e$          | -0.1     | 15        | 15        | 2.1   | 6                         | 0.2                             | 0                                  |

| $r_{bb}$         | 0.7      | 2.2       | 5.2       | 0     | 0.1                       | 0.7                             | 0                                  |

examined carefully for this calculation. Under maximum-clock-rate operation, the base voltages of Q7 and Q15 change states only slightly before an emitter current is established in these transistors through the turn-on of Q12 and Q24 at the next clock high-low transition. A hand calculation here can only be approximate; we will take the emitter current of Q7 and Q15 to be  $I_0$  during the base voltage transition. The delay is

$$T_{Q13/15} = (1/2)(kT/qI_{0,E} + R_{ex13})$$

$$\times (C_s + 2C_{cb15} + C_{je15} + \tau_f I_0/\Delta V_L)$$

$$+ (1/2)R_{bb13}(C_{je15} + 2C_{cbi15} + \tau_f I_0/\Delta V_L)$$

$$T_{Q13/15} = (1/2)(2kT/qJ_0 + \rho_e)(A_{e,cs}/A_{e,ef})$$

$$\times (C_s/A_{e,cs} + 2c_{cb} + c_{je} + \tau_f J_0/\Delta V_L)$$

$$+ (1/2)r_{bb}(c_{je} + 2c_{cbi} + \tau_f J_0/\Delta V_L) . \tag{25}$$

The total gate delay is then

$$1/2f_{clock} = T_{total} = T_{Q3emitter} + T_{Q3coll} + T_{Q13/15}$$

, (26)

and the maximum clock frequency  $f_{clock}$  is determined.

Both hand analysis and SPICE simulations indicate that  $f_{clock}$  exhibits a broad maximum as a function of the ratio of emitter follower to current switch emitter areas, with  $A_{e,ef}/A_{e,cs} \simeq 2$  being optimum. We subsequently assume this ratio. Results of the hand calculations are summarized in table 1. Note that because the logic swing  $\Delta V_L$  is large in comparison with kT/q, terms in  $kT/qJ_0$  will be substantially smaller than terms in  $\Delta V_L/J_0$  To somewhat simplify the tabulations,

Table 3: Delay components, found by SPICE, as a fraction of a total 4.9 ps latch delay, for the HBT of fig. 28. All emitter-followers and the lower-level current switch devices operate at 10<sup>5</sup> A/cm<sup>3</sup> current density, with the upper-level current switches operating at  $2 \cdot 10^5$  A/cm<sup>3</sup>. The logic swing is  $\Delta V_L = 200$  mV

|                  | $c_{je}$ | $c_{cbx}$ | $c_{cbi}$ | $c_s$ | $\frac{C_{m1}}{A_{e,cs}}$ | $\frac{\tau_f J_0}{\Delta V_L}$ | $\frac{\tau_{bus}J_0}{\Delta V_L}$ | total |

|------------------|----------|-----------|-----------|-------|---------------------------|---------------------------------|------------------------------------|-------|

| $\Delta V_L/J_0$ | 6%       | 7%        | 5%        | 4%    | 1%                        | 11%                             | 10%                                | 44%   |

| $ ho_e$          | 0%       | 9%        | 7%        | 2%    | 3%                        | 1%                              | 0%                                 | 21%   |

| $r_{bb}$         | 12%      | 1%        | 12%       | 0%    | 0%                        | 10%                             | 0%                                 | 35%   |

| total            | 18%      | 16%       | 23%       | 6%    | 5%                        | 22%                             | 10%                                | 100%  |

terms in  $kT/qJ_0$  were combined in subsequent tables with those in  $\Delta V_L/J_0$ . The delays  $\tau_f$  and  $\tau_{bus}$  are written as effective capacitances  $(\tau J_0/\Delta V_L)$ , in order to represent the delay in the form  $T_{gate} = 1/2 f_{clock} = \sum a_{ij} r_i c_j$ .

A large set of SPICE simulations were performed of M/S latch maximum toggle rate, using circuit models of  $\mu$ m-scale and submicron-emitter transferred-substrate HBTs. To the extent that the gate delay can be approximated by first-order delay terms,  $T_{gate} = 1/2 f_{clock} = \sum a_{ij} r_i c_j$ , the delay coefficients  $a_{ij}$  can be found by varying the HBT model parameters in the simulations. Tables 2 and 3 show the results of this analysis for the HBT of fig. 28. Given the many simplifications involved in the hand analysis, the correlation between hand analysis and simulation is reasonable, except that in hand analysis smaller coefficients are found for the terms  $r_{ex}c_{cbx}$ ,  $r_{ex}c_{cbi}$ ,  $r_{bb}c_{cbx}$ , and  $r_{bb}c_{cbi}$ , terms which in the simulations are found to collectively contribute 29% of the latch delay.

Tables 1, 2, and 3 provide important points regarding HBT design for fast logic. In modern InP-based HBTs,  $\tau_f$  is relatively small, and (for present UCSB HBTs) contributes only  $\sim 20\%$  of total gate delay, an amount comparable to the delay contributed by  $c_{je}$ , and much smaller than the  $\sim 40\%$  contributed by terms associated with  $(c_{cbx} + c_{cbi})$ . Low base and collector transit times, hence high  $f_{\tau}$ , is -of itself- not indicative of high speed logic operation. This is because under logic operation, the change in base+collector stored charge is

$$\Delta Q_{b,c} = \tau_f I_0 = \left(\frac{\tau_f I_0}{\Delta V_L}\right) \Delta V_L = C_{ls} \Delta V_L , \qquad (27)$$

while under small-signal operation

$$\delta Q_{b,c} = g_m \tau_f \delta V_{be} = \left(\frac{\tau_f I_0}{kT/q}\right) \delta V_{be} = C_{ss} \delta V_{be} . \tag{28}$$

Under logic operation, the base-emitter diffusion capacitance associated with  $\tau_f$  is reduced in proportion to the ratio of logic swing  $\Delta V_L$  to kT/q, a ratio of typically 10:1. In contrast, under logic operation the capacitances  $C_{je}$  and  $C_{cb}$  must be provided with charge  $C_{je}\Delta V_L$ , and  $C_{cb}\Delta V_L$ .

Examining the delay components in terms of real  $(r_{bb}, r_{ex})$  and equivalent  $(\Delta V_L/J_o)$  resistances through which the depletion and diffusion capacitances are charged, we are faced with a significant discrepancy between hand and computer analyses. In either analysis,  $\Delta V_L/J_o$  is dominant. A key conclusion is that high current densities are essential for fast HBT logic circuits. If the HBT is operated at a current density limited by the Kirk effect (eqn. 6), then the delay terms associated with charging the collector-base capacitance,

$$\frac{C_{cb}\Delta V_L}{I_0} = \frac{\epsilon A_c}{T_c} \cdot \frac{\Delta V_L}{J_o A_e}

= \frac{A_c}{A_e} \frac{\Delta V_L}{(V_{cb} + \phi)} \frac{T_c}{4v_{sat}},$$

(29)

are minimized through use of thin collector layers. Delay associated with  $r_{bb}$  is also significant. Finally, note that while simulations associate 22% of the net delay with  $R_{ex}$ , this underestimates its effect; because adequate noise margin demands  $\Delta V_L \geq 6kT/q + J_0\rho_e$  (eq. 21), reducing delay terms associated with  $\Delta V_L/J_o$  through increased current density demands simultaneous improvements in  $\rho_e$ .

#### 3.2. Scaling for high speed logic

As examined in sections 2.2 and 2.3, lithographic scaling of the emitter and collector junction widths progressively increases  $f_{max}$  if the parasitic collector-base junction is eliminated. If the lithographic dimensions are scaled while holding the base and collector epitaxial layer thicknesses constant,  $f_{max}$  increases rapidly while  $f_{\tau}$  remains relatively constant. While such a device will produce gain at very high frequencies in reactively-tuned MIMICs, broadband analog circuits require simultaneous high values of  $f_{\tau}$  and  $f_{max}$ .

In analyzing HBT logic speed (section 3.1), it is found that  $\sim 10$ –15 equivalent RC delay terms are significant. In order to improve logic speed, all significant HBT capacitances and transit delays must be reduced. We now examine the scaling of HBT parameters required to increase bandwidth by a factor of  $\gamma:1$ , using simplified expressions for HBT parameters in order to more clearly show the dominant trends. To ensure that bandwidth increases by  $\gamma:1$  for all circuits, digital and analog, using the scaled HBT, all transit times and all capacitances in figure 9 must be reduced by  $\gamma:1$ , while maintaining constant all resistances, the transconductance, and the collector bias current  $I_c$ . Explicitly,  $I_c \propto \gamma^0$  and  $g_m \propto \gamma^0$ .

The base-emitter diffusion capacitance is

$$C_{be,diff} = g_m(\tau_b + \tau_c) = (qI_c/kT)(\kappa_2 T_b^2 + \kappa_3 T_c)$$

, (30)

Here the terms  $\kappa_i$  represent parameters which do not change with scaling. To obtain  $C_{be,\text{diff}} \propto \gamma^{-1}$  with fixed  $I_c$ , we must set  $\tau_b \propto \gamma^{-1}$  and  $\tau_c \propto \gamma^{-1}$ . This requires  $T_b \propto \gamma^{-1/2}$  and  $T_c \propto \gamma^{-1}$ .

An immediately apparent limit to collector scaling is loss of collector breakdown voltage. An AlInAs/GaInAs HBT with a 0.2  $\mu$ m InGaAs collector thickness exhibits  $V_{br,ceo} = 1.5 \text{ V}$  at  $10^5 \text{ A/cm}^2$  bias. Semiconductors with higher products

$(\mathcal{E}_{max}v_{sat})$  of breakdown field and electron velocity mitigate this limit; HBTs with InP collectors  $^{35}$  exhibit  $\tau_c$  comparable to devices with InGaAs collectors but have  $\sim 5:1$  increased breakdown. Regardless of the collector thickness, impact ionization cannot occur for  $V_{ce}$  less than the bandgap of the collector semiconductor. Further, unless the collector bandgap is small or the collector much thinner than 1000 Å, Zener tunneling currents will also be small for bias voltages below the collector bandgap energy. Even with 1000-Å collector layers, an InP/GaInAs/InP DHBT will exhibit  $V_{br,ceo} > 1.2 \text{ V}$ , sufficient for current-mode logic. While important in power amplifiers and in mixed-signal (medium-voltage) ICs, loss of breakdown voltage may not pose a serious limit to the scaling of InP-collector DHBTs for low-voltage, high-speed logic.

The capacitance  $C_{je}$  is given by

$$C_{je} = C_{je1} + C_{je2} = \kappa_4 L_e W_e / T_{eb} + \kappa_5 T_{eb} T_b I_c . \tag{31}$$

Analysis of the partitioning of  $C_{cb}$  between  $C_{cb,x}$  and  $C_{cbi}$  is complex (section 2.3), and in this section we therefore restrict the analysis to HBTs in which  $C_{cb,x}$  is zero ( $L_c \simeq L_e$  and  $W_c \simeq W_e$ ) and  $C_{cbi} = C_{cb}$ . Such HBTs include transferred-substrate (figure 4) and undercut-mesa devices (figure 8), and mesa devices having very high base doping and hence requiring only a very small base Ohmic contact width.  $C_{cb}$  then scales as

$$C_{cb} = \epsilon W_c L_c / T_c \simeq \epsilon W_e L_e / T_c . \tag{32}$$

Because  $T_c \propto \gamma^{-1}$ , to obtain  $C_{cb} \propto \gamma^{-1}$  we must set  $W_c L_c \propto \gamma^{-2}$  and hence  $W_e L_e \propto \gamma^{-2}$ .

The base resistance  $R_{bb}$  is the sum of the terms (eqn. 14)  $R_{b,cont}$ ,  $R_{gap}$  and  $R_{spread}$ . Correct scaling of  $C_{cb}$  requires that  $W_eL_e \propto \gamma^{-2}$ . It is desired that  $R_{bb}$  vary negligibly with scaling; we show here that this is obtained by setting  $W_e \propto W_c \propto \gamma^{-2}$  and  $L_e \simeq L_c \propto \gamma^0$ . The base contact resistance term  $R_{b,cont} = \kappa_6 \rho_c^{1/2} / L_e T_e$  is proportional to  $\gamma^{1/4}$ , while  $R_{spread} = \kappa_7 W_e / L_e T_{eb} \propto \gamma^{-3/2}$ . If we scale  $W_{eb} \propto \gamma^{-1}$ , then  $R_{gap} = \kappa_8 W_{eb} / L_e T_b \propto \gamma^{-1/2}$ . While the contact resistance term  $R_{b,cont}$ , the dominant term in  $R_{bb}$  for submicron devices, increases ( $\propto \gamma^{1/4}$ ) slowly with scaling, the rapid decrease in  $R_{gap}$  and  $R_{spread}$  results in a total  $R_{bb}$  showing only a very slow increase with scaling.

To obtain  $C_{je2} \propto \gamma^{-1}$  we must set  $T_{eb} \propto \gamma^{-1/2}$ . This results in  $C_{je1} \propto \gamma^{-3/2}$ , improving more rapidly than required for a  $\gamma$ : 1 scaling in transistor bandwidth.

The collector series resistance  $R_c$  is zero in transferred-substrate HBTs using Schottky collector contacts. In undercut-mesa devices,  $R_c$  has a similar geometric dependence as  $R_{bb}$ , and also varies only minimally with scaling.

Scaling thus requires that the emitter and collector stripe widths  $W_e$  and  $W_c$  be proportional to  $\gamma^{-2}$ , and that the emitter and collector stripe lengths  $L_e$  and  $L_c$  be independent of scaling. Because the collector current is constant  $(I_c \propto \gamma^0)$ , the emitter current density increases quadratically with the desired improvement in transistor bandwidth  $(J_e \propto \gamma^2)$ , as does the transistor's operating power density

$(P/A_e = J_e V_{ce} \propto \gamma^2)$ . Limits to bias current density imposed by reliability concerns and dissipated power density are thus major impediments to scaling for high bandwidth.

The emitter resistance  $R_{ex} = \rho_e/W_eL_e$  presents a major impediment to scaling. With  $W_eL_e \propto \gamma^{-2}$ , in order to maintain the desired constant  $R_{ex}$  the aggregate emitter resistivity  $\rho_e \propto \gamma^{-2}$  must improve in proportion to the square of the intended improvement in HBT bandwidth. This will require substantial increases in emitter doping over those now typically used in HBTs, and use of low-resistivity (e.g. InAs) semiconductor contact layers.

The collector-emitter resistance is  $R_{ce} = V_A/I_c$ , where the Early voltage is  $V_A = qN_aT_bT_c/\epsilon$  and  $N_a$  is the base doping. From these relationships  $R_{ce} \propto \gamma^{-3/2}$ , and does not scale as desired. Fortunately, for an HBT with  $T_b = 300$  Å,  $T_c = 0.2\mu\text{m}$ , and  $N_A = 5 \cdot 10^{19}/\text{cm}^3$  (a device with 275 GHz  $f_\tau$ ),  $V_A \sim 500$  V. A  $\gamma = 10:1$  scaling for a target 2750 GHz  $f_\tau$  would still result in  $V_A = 16$  Volts, which is acceptably large. In HBTs, degradation of  $R_{ce}$  through base-width modulation is not a significant impediment to scaling.

In scaling the device, we have set  $W_e \propto \gamma^2$  and  $L_e \propto \gamma^0$ . If all other widths and lengths in the device layout are scaled in the same proportions, then the HBT area, and the area of a given circuit, are proportional to  $\gamma^{-2}$ . The average wire length within the circuit is proportional to the square root of the IC area, and hence is proportional to  $\gamma^{-1}$ . Wiring delays, whether transmission-line delays or  $C_{wire}\Delta V/\Delta I$  charging times, thus also scale correctly. Because of the fixed bulk metal resistivity, interconnect parasitic series resistance does not scale correctly, increasing as  $\gamma^2$ .

In scaled HBTs, base current is dominated by surface recombination and by currents conducted on the surface between the base-emitter junction and the base Ohmic contact. Consequently,  $I_b \propto n(T_{eb})L_e$ . Because  $I_c \propto L_eW_en(T_{eb})/T_b$ ,  $\beta \propto W_e/T_b$ . With the scaling laws above,  $\beta \propto \gamma^{-3/2}$ . Current gain decreases rapidly with scaling, and reduction of surface recombination and surface conduction is critical in deep submicron devices.

Finally, we reconsider scaling of the mesa HBT. For mesa HBTs, base and collector thickness, emitter and collector junction widths, emitter contact resistivity, and current density must all scale as discussed above for undercut-mesa and transferred-substrate HBTs. In particular, the base-collector junction width must still scale as  $\gamma^{-2}$ . For a normal triple-mesa device, this then requires that the widths  $W_b$  of the base Ohmic contacts (fig. 1) scale as  $\gamma^{-2}$ , while maintaining a fixed  $R_{b,cont} = (\rho_s \rho_c)^{1/2} (1/2L_e) \coth(W_b/L_{\rm contact})$ . This can be accomplished by a combined reduction of both  $\rho_s$  and  $\rho_c$ , and hence a general analysis is exceedingly complex. As a limiting case, with a highly scaled HBT,  $W_c$  and must be very small, and hence  $W_b$  will be much less than  $L_{\rm contact}$ . In this case  $R_{b,cont} \simeq \rho_c/2L_eW_b$ , and hence constant  $R_{b,cont}$  requires that the base Ohmic contact resistivity scale as  $\rho_c \propto \gamma^{-2}$ . Transferred-substrate and narrow-mesa HBTs do not require this improvement of base contact resistivity with scaling.

Table 4: Scaling laws for HBTs; required proportional change in key relevant HBT physical parameters in order to obtain a  $\gamma$ :1 increase in bandwidth in an arbitrary circuit. Additionally, for mesa HBTs, but not transferred-substrate or undercutmesa devices, the base contact resistivity  $\rho_v$  must scale as  $\gamma^{-2}$

| parameter                           | symbol                   | scaling law     |

|-------------------------------------|--------------------------|-----------------|

| collector depletion layer thickness | $T_c$                    | $\gamma^{-1}$   |

| base epitaxial layer thickness      | $T_b$                    | $\gamma^{-1/2}$ |

| emitter-base junction width         | $W_e$                    | $\gamma^{-2}$   |

| collector-base junction width       | $W_c$                    | $\gamma^{-2}$   |

| emitter-base depletion thickness    | $T_{eb}$                 | $\gamma^{-1/2}$ |

| emitter parasitic resistivity       | $\rho_e = R_{ex} A_e$    | $\gamma^{-2}$   |

| emitter junction area               | $A_e = W_e L_e$          | $\gamma^{-2}$   |

| emitter current                     | $I_e$                    | $\gamma^0$      |

| emitter current density             | $J_e$                    | $\gamma^2$      |

| bias and signal voltages            | $V_{CE}, v_{ce}, v_{be}$ | $\gamma^0$      |

| average interconnect length         | $L_{wire}$               | $\gamma^{-1}$   |

| circuit area                        | _                        | $\gamma^{-2}$   |

| device power density                | _                        | $\gamma^2$      |

| circuit power density               | _                        | $\gamma^2$      |

To simultaneously increase HBT bandwidth in general circuits by  $\gamma$ : 1, emitter and collector junction widths must vary as  $\gamma^{-2}$  while maintaining constant junction lengths. Base thickness must vary as  $\gamma^{-1/2}$  and collector thickness as  $\gamma^{-1}$ . Emitter current density and transistor and IC power density all increase in proportion to  $\gamma^2$ . The emitter contact structure must improve in proportion to  $\gamma^2$ . Power dissipation, reliability under high-current operation, required improvements in surface recombination velocity, and the required quality of the emitter Ohmic contact are the most significant impediments to scaling. These relationships are summarized in table 4.

# 3.3. Design projections for > 200 GHz logic

Following the design rules above, a scaling study of high speed M/S latches was pursued. Based upon measured parameters of tested HBTs, an HBT SPICE model was developed in which model elements (depletion capacitances, contact resistances, and carrier transit times) were calculated as a function of lithographic dimensions and layer thicknesses. ECL master-slave flip-flops were then simulated for maximum clock frequency. The results (table 5) start with the HBT design of fig. 28, and show progressive increases in clock rate as the emitter and collector stripe widths are reduced, base and collector layers thinned, the current density increased, and the emitter contact resistivity reduced. Thin collector layers are here required not primarily for low  $\tau_c$ , but primarily so as to increase (eq. 6) the current density at base pushout, and hence decrease  $C_{cb}\Delta V_L/I$  (eq. 29).

Table 5: SPICE simulation results of flip-flop clock speed as a function of transistor design. Interconnect capacitance and delay is not considered. Boldface indicates parameter changed from previous design..

| Emitter |                     |       | Col       | llector           | Base     |           | Clock            |     |

|---------|---------------------|-------|-----------|-------------------|----------|-----------|------------------|-----|

|         | parasitic           |       |           | current           |          |           |                  |     |

| width   | resistance          | width | thickness | density           | material | thickness | doping           |     |

| 1.2     | 50                  | 1.8   | 3000      | 1.0E+05           | InGaAs   | 400       | 4E19 Be          | 115 |

| 0.7     | 50                  | 1.5   | 3000      | 1.0E+05           | InGaAs   | 400       | 4E19 Be          | 125 |

| 0.7     | 50                  | 1.5   | 3000      | 1.0E+05           | InGaAs   | 300       | 4E19 Be          | 128 |

| 0.7     | 50                  | 0.8   | 3000      | 1.0E+05           | InGaAs   | 300       | 4E19 Be          | 159 |

| 0.35    | 50                  | 0.45  | 3000      | 1.0E+05           | InGaAs   | 300       | 4E19 Be          | 176 |

| 0.35    | 50                  | 0.45  | 3000      | 1.0E+05           | InGaAs   | 300       | 1E20 C           | 182 |

| 0.35    | 25                  | 0.45  | 2120      | 2.0E+05           | InP      | 300       | 1E20 C           | 250 |

| 0.35    | 12.5                | 0.45  | 1500      | 4.0E+05           | InP      | 300       | 1E20 C           | 285 |

| μm      | Ohm-µm <sup>2</sup> | μm    | Å         | A/cm <sup>2</sup> | -        | Å         | cm <sup>-3</sup> | GHz |

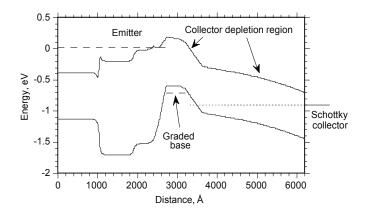

Figure 13: Band diagram, under bias, of a typical device.

#### 4. Transferred-substrate HBTs

Wide HBT bandwidths are obtained by scaling. In scaling for high  $f_{\tau}$ , significant limits include high power density and high current density, demands for very low emitter parasitic resistance, and the collapse of  $f_{max}$  due to the extrinsic collectorbase junction. Using substrate transfer processes, this extrinsic junction can be reduced in size or eliminated. This permits either aggressive lithographic scaling without epitaxial scaling for greatly increased  $f_{max}$  at constant  $f_{\tau}$ . Alternatively, if high values of both  $f_{\tau}$  and  $f_{max}$  are sought, simultaneous lithographic and epitaxial scaling is required; with the extrinsic  $C_{cb}$  eliminated, operation at high current density and reduction of the emitter resistance are the key requirements for further scaling.

#### 4.1. Growth and fabrication

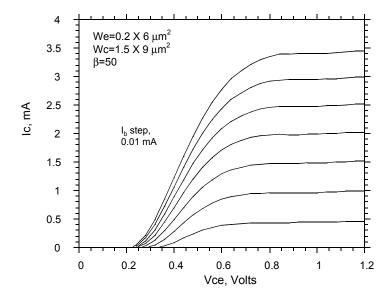

The epitaxial layer structure is described by its band diagram (fig. 13). The In-GaAs base is typically 300–400 Å thick, has 2kT bandgap grading, and is Be-doped at 5·10<sup>19</sup>/cm<sup>3</sup>. The InGaAs collector is 2000-3000 Å thickness. A collector N<sup>+</sup> pulse-doped layer placed 400 Å from the base delays the onset of base push-out at high collector current densities. Although such pulse-doped layers have been used as electron launchers <sup>39</sup> in GaAs-based HBTs, our experimental data shows no significant effect of the launcher upon  $\tau_c$  for InGaAs-collector HBTs.

Devices typically use Schottky collector contacts <sup>40</sup>, although HBTs with N+ subcollector layers (Ohmic-collector devices) have also been fabricated. While Ohmic-collector devices have non-zero collector series resistance, hence lower  $f_{max}$  $^{24}$ , the 0.2 V barrier present in the Schottky-collector device increases the  $V_{ce}$  re-

Figure 14: Transferred-substrate HBT process flow.

quired to suppress base push-out at high current densities. Ohmic-collector devices thus show higher  $f_{max}$  under the low- $V_{ce}$  conditions associated with current-modelogic (CML). Schottky-collector devices are used for emitter-coupled-logic (ECL), where the operating  $V_{ce}$  is higher.

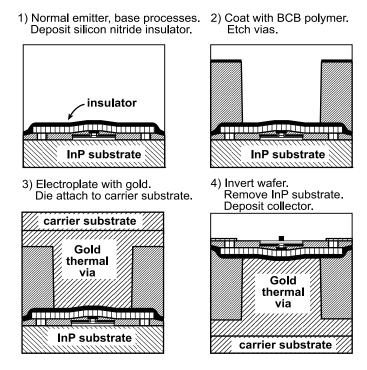

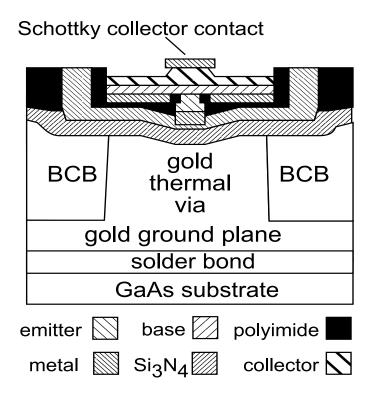

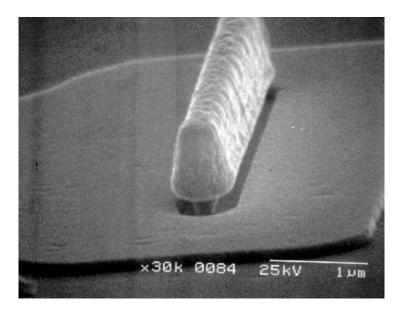

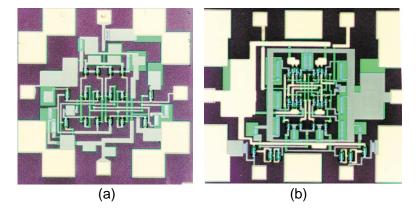

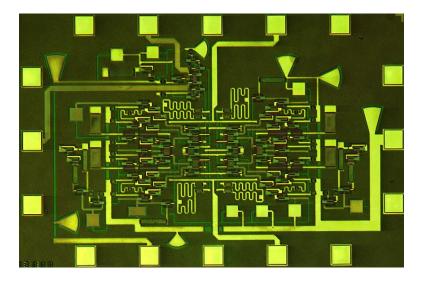

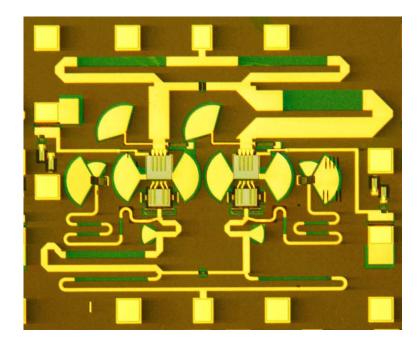

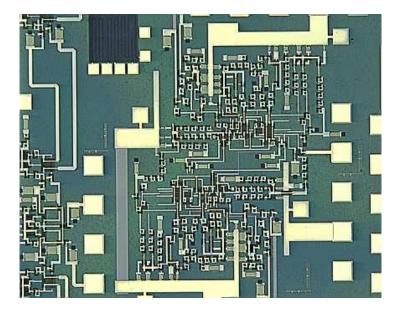

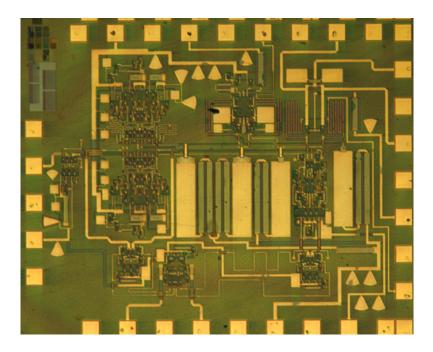

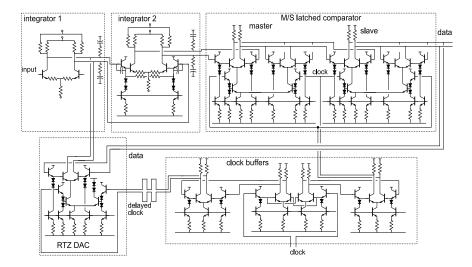

Figure 14 shows the process flow. Standard fabrication processes 42 define the emitter-base junction, the base mesa, polyimide planarization, and the emitter contacts. The substrate transfer process commences with deposition of the PECVD Si<sub>3</sub>N<sub>4</sub> insulator layer and the Benzocyclobutene (BCB) transmission-line dielectric (5  $\mu$ m thickness). Thermal and electrical vias are etched in the BCB. The wafer is electroplated to metallize the vias and to form the ground plane. The wafer is then solder-bonded to a GaAs carrier substrate. The InP substrate is removed in HCl and Schottky collectors are deposited, completing the process. Fig. 15 shows a detailed device cross section.

For the emitter-base junction, deep submicron scaling requires tight control of lateral undercutting during the base contact recess etch. To form the emitter, reactive-ion etching in CH<sub>4</sub> / H<sub>2</sub> / Ar, monitored with a HeNe laser, first removes the N<sup>+</sup> GaInAs emitter contact layer. A HCl/HBr/Acetic selective wet etch then removes the AlInAs emitter, stopping on the AlInAs/GaInAs emitter-base grade. By etching at 10° C, the etch rate is slowed, and a controlled emitter undercut is formed. The undercut both narrows the emitter and serves (as normal) to define

Figure 15: Schematic cross-section of a transferred-substrate HBT

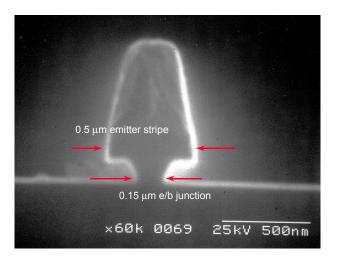

Figure 16: Cross-section of emitter-base junction. The 0.5  $\mu$ m emitter metal was defined with a projection lithography system.

Figure 17: Transferred-substrate HBT defined by contact lithography

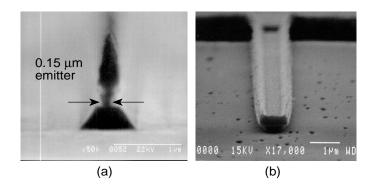

Figure 18: E-beam HBT: test structure with 0.15  $\mu$ m emitter-base junction (a), and 0.4  $\mu$ m Schottky collector stripe (b)

the liftoff edge in the self-aligned base contact deposition. A timed nonselective wet Citric/H<sub>3</sub>PO<sub>4</sub>/H<sub>2</sub>O<sub>2</sub> etch then removes the base- emitter grade. Etch selectivity in both the RIE and HCl/HBr/Acetic etches aids in etch-depth control, and we are able to reproducibly etch  $\sim 100$  Å into the base without use of surface contact resistance probing as a process monitor. Figure 16 shows the cross-section of a 0.15- $\mu$ m emitter-base junction.

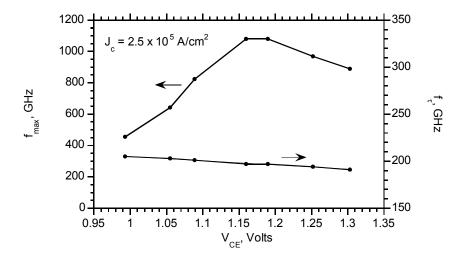

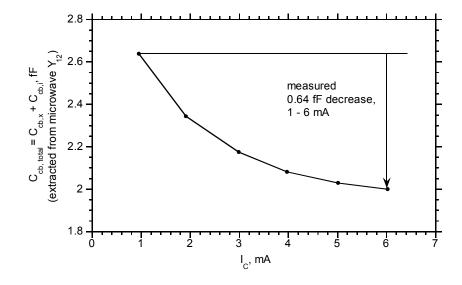

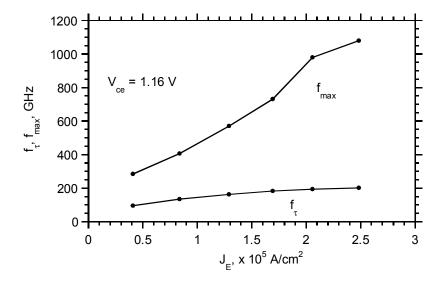

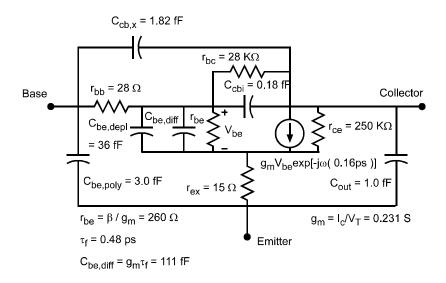

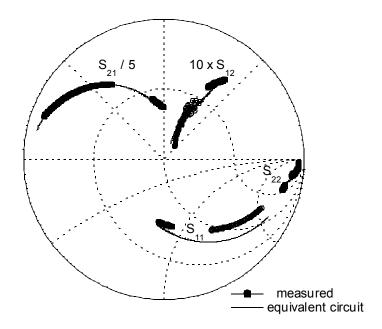

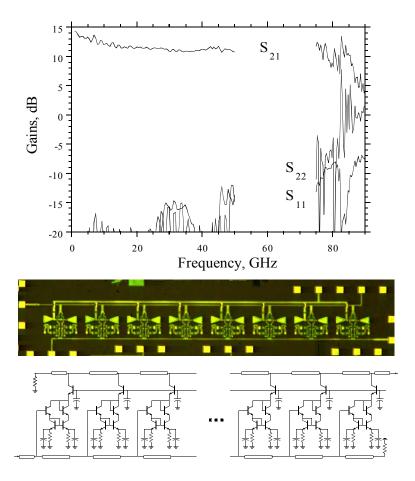

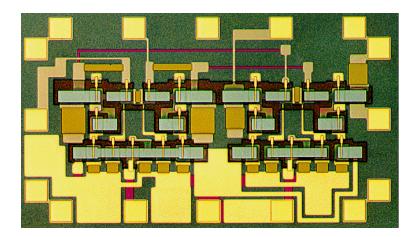

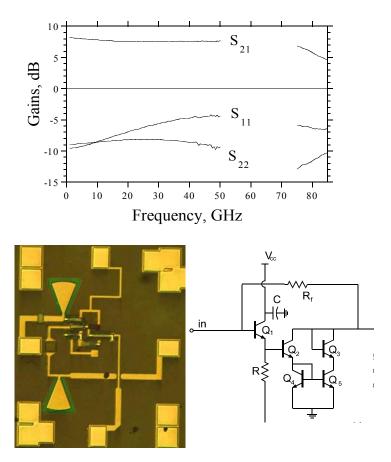

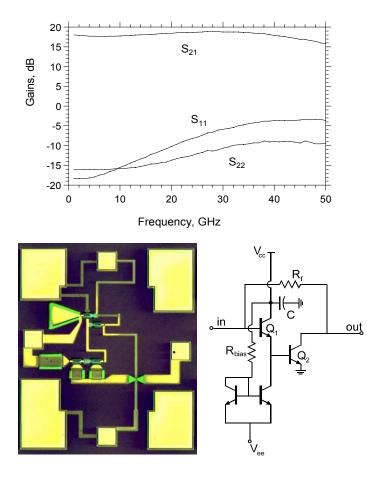

In defining submicron collector-base junctions, use of the Schottky-collector contact eliminates the need for an etch of similar precision through an N<sup>+</sup> collector Ohmic contact layer. The collector junction is defined by the stripe width of the deposited metal. Subsequent to collector deposition, a self-aligned wet etch of  $\sim 1000$ Å depth removes the collector junction sidewalls (eliminating fringing fields) and reduces the collector junction width by  $\sim 2000$  Å. The step, intended to reduce  $C_{cb}$ , generally provides a greater increase  $f_{max}$  than would be expected from the observed reduction in collector junction width.