# $In_{0.53}Ga_{0.47}As/InP$ TYPE-I DHBTs w/ 100 nm COLLECTOR AND 491GHzf , $415~GHZf_{max}$

Zach Griffith, Mattias Dahlström\*, and Mark J.W. Rodwell Department of Electrical and Computer Engineering University of California, Santa Barbara, CA 93106-9560, USA E-mail: <a href="mailto:griffith@ece.ucsb.edu">griffith@ece.ucsb.edu</a>, 805-893-3273

Xiao-Ming Fang, Dmitri Loubychev, Ying Wu, Joel M. Fastenau, Amy W.K. Liu IQE Inc., 119 Technology Drive, Bethlehem, PA 18015, USA

now with IBM Microelectronics Semiconductor Research and Development Center Essex Junction, VT 05452, USA

#### Abstract

In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP double heterojunction bipolar transistors (Type-I DHBT) have been designed and fabricated having 100 nm drift collector and 30 nm highly doped base. The DHBTs have been scaled vertically for reduced electron transit time and aggressively scaled laterally to minimize the base-collector capacitance  $C_{cb}$  associated with thinner collectors. Devices employing a proven effective InGaAs/InAlAs superlattice base-collector grade (42 nm transition) exhibit a 491 GHz f and 415 GHz  $f_{max}$  and show no signs of current blocking until P > 20 mW/ $\mu$ m<sup>2</sup> due to device self-heating. We also report devices of the same layer structure where the base-collector transition has been thinned to 25 nm exhibiting a 465 GHz f and 416 GHz  $f_{max}$  and show no signs of current blocking until  $J_e > 9$  mA/ $\mu$ m<sup>2</sup> at 2.0  $V_{ce}$  associated with the base-collector grade. For both, the DC current gain  $V_{ce} = 3.1$  V, and similar ideality factors  $v_{ce} = 3.1$  V, and similar ideality factors  $v_{ce} = 3.1$  V.

## I. Introduction

Development of digital logic and mixed-signal systems operating at higher clock speeds and bandwidth require continued improvement in transistor performance [1]. Projected HBT performance for 160 Gb/s systems include an f and  $f_{max} > 440$  GHz, a breakdown voltage  $V_{BR,CEO} > 3$  V, operating current density  $J_e > 10 \text{ mA/}\mu\text{m}^2$  at  $V_{cb} = 0 \text{ V}$ , and low base-collector capacitance  $(C_{cb}/I_c < 0.5 \text{ psec/V})$  [2]. When designing an HBT for use in a digital IC, it should be done with emphasis on minimizing the major delay terms associated with  $= C_{cb} V_{logic}/I_c$ . If the device can operate at the Kirk threshold current density  $J_{Kirk} = T_c^{-2}$  (electric field at the basecollector junction is zero) as the collector thickness  $T_c$  is reduced, the delay  $C_{cb}$   $V_{logic}/I_c$  scales  $T_c$ . In order for an InP DHBT to effectively operate at the high current densities associated with thinner collectors, proper design and growth of the base-collector grade (Type-I DHBT) is crucial to prevent current blocking related to the conduction band discontinuity  $E_c$  0.26 eV between In<sub>0.53</sub>Ga<sub>0.47</sub>As and InP--these include a chirped superlattice InGaAs / InAlAs grade with pulse doping [3,4] or step-graded InGaAs / InGaAsP / InP collector [5]. Type-II DHBTs are an alternative where no base-collector grading is required because of the staggered band lineup of the GaAsSb base and InP collector [6], but this comes at the expense of a lower hole mobility p for GaAsSb [7]. We

present here experimental evidence that with proper design and growth, a Type-I DHBT with chirped superlattice base-collector grade can operate at current densities  $J_e > 16 \, \mathrm{mA/\mu m^2}$  at a 100 nm collector scaling generation without current blocking associated with the conduction band discontinuity  $E_c$ .

## II. Design

For Type-I DHBTs to operate effectively at high  $J_e$ , the conduction band discontinuity between InGaAs and InP must be removed. Previous DHBT designs from our laboratory have employed a 47 nm transition region (20 nm setback / launcher,

Table 1: DHBT layer structures, 42 / 25 nm transitions

| Table 1. Diffit tayer structures, 42 / 23 nm transitions |                                           |                           |               |  |  |  |

|----------------------------------------------------------|-------------------------------------------|---------------------------|---------------|--|--|--|

| Thickness, nm                                            | Material                                  | Doping, cm-3              | Description   |  |  |  |

| 30                                                       | InGaAs                                    | 7-4 10 <sup>19</sup> : C  | Base          |  |  |  |

| 15 / 10                                                  | In <sub>0.53</sub> Ga <sub>0.47</sub> As  | 9 10 <sup>16</sup> : Si   | Setback       |  |  |  |

| 24 / 12                                                  | 2 InGaAs / InAlAs 9 10 <sup>16</sup> ; Si |                           | B-C Grade     |  |  |  |

| 3                                                        | InP                                       | . 10 <sup>18</sup> : Si   | Pulse doping  |  |  |  |

| 58 / 75                                                  | InΡ                                       | 9 10 <sup>16</sup> : Si   | Collector     |  |  |  |

| 10                                                       | lnP                                       | 1.5 10 <sup>19</sup> : Si | Sub-Collector |  |  |  |

| 8.5                                                      | In <sub>0.53</sub> Ga <sub>0.47</sub> As  | 2 10 <sup>19</sup> : Si   | Sub-Collector |  |  |  |

| 300 InP                                                  |                                           | 2 10 <sup>19</sup> : Si   | Sub-Collector |  |  |  |

| Substrate                                                | SI : InP                                  |                           |               |  |  |  |

Table 2: Summary of device characteristics

| Transition | Peak | V <sub>BR,CEO</sub> | c,emitter<br>Ω-μm <sup>2</sup> | s, base | c, base<br>Ω-μm <sup>2</sup> | s, col | c, col<br>Ω-μm <sup>2</sup> | nb   | n <sub>C</sub> | T,peak | Peak f | Peak<br>f <sub>max</sub> |

|------------|------|---------------------|--------------------------------|---------|------------------------------|--------|-----------------------------|------|----------------|--------|--------|--------------------------|

| 42 nm      | 41   | 3.1                 | 7.8                            | 629     | 6.2                          | 12.9   | 4.0                         | 1.44 | 1.12           | 105 K  | 491    | 415                      |

| 25 nm      | 47   | 3.1                 | 10.4                           | 616     | 3.8                          | 13.3   | 5.8                         | 1.51 | 1.11           | 111 K  | 465    | 416                      |

24 nm grade, 3 nm pulse doping) between the base and InP portion of the collector--this proved effective and device and circuit results for such have been previously reported [4,8,9]. As  $T_c$  is scaled, the ternary materials associated with the setback and grade occupy a greater portion of the collector and the device operating temperature will increase rapidly at moderate base-collector voltages  $V_{cb}$  [10]. There are two approaches to reduce them from the collector.

The conduction-band potential drop across the setback layer associated with launching electrons into the grade is [4]:

setback

$$(V_{cb})$$

$\frac{T_{setback}}{T_c}$   $\frac{qN T T_{setback}}{\sigma_r}$   $\frac{(qN_c - J(x)/\phi_{eff})T_cT_{setback}}{2\sigma_r}$  (1)

For the device designs reported in [4,8], the 200 nm and 150 nm  $T_c$  with 20 nm  $T_{setback}$  had a  $_{setback}$  0.370 and 0.378 eV, respectively. Scaling to 100 nm  $T_c$  w/ 20 nm  $T_{setback}$  would give  $_{setback}$  0.442 eV. Based on the previous results and the effectiveness of the grade with the values of  $_{setback}$  just listed, the setback was thinned for these 100 nm collector devices to 15 nm (42 nm transition) for  $_{setback}$  0.332 eV.

A pulse-doping is required to suppress the change in the conduction band quasi-field at the InP interface within the collector when a chirped-superlattice grade is used to remove the  $E_c$  discontinuity and is determined from the following relationship [3,4]:

$$NT = \frac{-\frac{o}{r} E_c}{q^2 T_{grade}}$$

(2)

The second device design explored employs the same layer structure and doping values as pursued for the 42 nm transition device, but the grade has been reduced by 2:1, with the pulse doping and setback adjusted (25 nm transition) to produce a setback 0.338 eV

## III. Growth and Fabrication

The epitaxial material was grown by commercial vendor IQE Inc. on a 3" SI-InP wafer and the HBTs were fabricated in an all wet etch, standard triple mesa process. The device layer structure is provided in table 1 and further details of the base and collector design are given in [4]. The devices are passivated with and the wafer is planarized in benzocyclobutene (BCB) to minimize device leakage currents associated with semiconductor surface charge effects. BCB also provides a low-loss spacer (  $_r = 2.7$ ,  $T_{BCB} = 1.6 \mu m$ ) between the device interconnects and InP substrate to reduce spurious resonances from the RF measurements through substrate mode coupling.

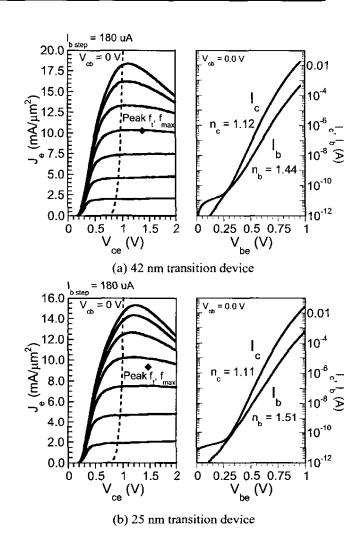

Figure 1: Common emitter I-V and Gummel Characteristics Emitter junction area,  $A_{ibe} = 0.6$  4.3  $\mu$ m<sup>2</sup>

#### IV. Measurements and Results

A summary of the device characteristics is provided in table 2. Standard transmission line measurements (TLM) were performed to extract the sheet resistance  $_c$  and contact resistance  $_c$  for the base and collector layers. The emitter  $_c$  was determined from RF parameter extraction. DHBTs for both layer structures have a peak  $_c>40$ , a common-emitter breakdown voltage  $V_{BR,CEO}=3.1$  V (at  $I_c=50$  µA), and a collector leakage current  $I_{cbo}<150$  pA (at  $V_{ch,offset}=0.3$  V). A plot of the common-emitter current-voltage and Gummel characteristics are shown in figure 1.

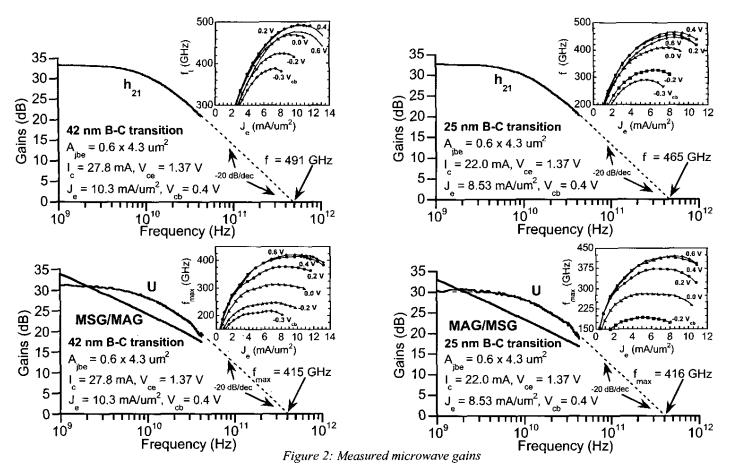

DC-42 GHz RF measurements were carried out after performing an off wafer Line-Reflect-Line (LRL) calibration on an Agilent 8510C network analyzer. An on-wafer open circuit pad structure identical to the one used by the devices was measured after calibration in order to de-embed this associated capacitance from the device measurements. Peak f and  $f_{max}$  were determined from extrapolation through a least-square-fit between the transfer functions  $|h_{21}(f)| = h_{21,DC}/(1+h_{21,DC}^2(f^2/f^2))^{1/2}$ , and  $|U(f)| = U_{DC}/(1+U_{DC}^2(f^2/f_{max}^2))^{1/2}$ , to the measured microwave gains  $|h_{21}|$  and |U|, at measured frequencies. Both DHBTs have a 0.6 4.3  $\mu$ m² emitter s/c junction area  $A_{jbe}$  and 1.3  $\mu$ m collector mesa width--collector to emitter width ratio  $W_c/W_e = 2.17$ . Peak f and  $f_{max}$  for all devices is between  $J_e = 7-11$  mA/ $\mu$ m² at  $V_{cb} = 0.4$  V for different device dimensions on the wafers.

Thermal resistance  $J_A$  and device junction temperature were measured by the method of Liu [11] at different  $V_{cb}$  to vary the field distribution and thus power dissipation in the InGaAs setback, ternary grade, and InP layers of the collector. Because InGaAs, InAlAs, and InP have substantially different thermal resistivities, variation of  $J_A$  with  $V_{cb}$  and  $J_e$  should be expected. Table 3 shows  $J_A$  (from  $J_e = 5.8$  mA/ $\mu$ m²) for varying  $V_{cb}$  and the temperature rise at different bias points. Note that the change in thermal feedback coefficient, (V/K) is adjusted to account for the difference in operating current density. Also, the collector junction may be considerably hotter than the emitter junction due to the emitter interconnect metal, and the high thermal resistance of the InGaAs base.

Table 3 -- Thermal data, 42 nm transition

| <sub>JA</sub> = 2.3613 + | 0.8056 V <sub>cb</sub> (K/mW) A <sub>jbe</sub> = | - 0.6 4.3 μm² |

|--------------------------|--------------------------------------------------|---------------|

| V <sub>ce</sub> (V)      | J <sub>e</sub> (mA/μm²)                          | T (K)         |

| 2.5                      | 9.61                                             | 242           |

| 2.5                      | 7.40                                             | 179           |

| 2.0                      | 14.49                                            | 271           |

| 2.0                      | 13.66                                            | 253           |

| 2.0                      | 12.36                                            | 226           |

| 1.11                     | 18.41                                            | 153           |

| 1.37                     | 10.30                                            | 105           |

Thermal data, 25 nm transition

| JA = 2.9195         | + 1.4154 V <sub>cb</sub> (K/mW) – A <sub>jbe</sub> = | = 0.6 4.3 μm² |

|---------------------|------------------------------------------------------|---------------|

| V <sub>ce</sub> (V) | J <sub>e</sub> (mA/μm²)                              | <i>T</i> (K)  |

| 2.5                 | 8.60                                                 | 304           |

| 2.5                 | 7.12                                                 | 247           |

| 2.0                 | 14.90                                                | 386           |

| 2.0                 | 12.33                                                | 311           |

| 2.0                 | 10.90                                                | 272           |

| 1.23                | 15.30                                                | 176           |

| 1.37                | 8.53                                                 | 111           |

# Acknowledgement

This work was supported by the ONR under contract N0001-40-4-10071 and DARPA TFAST program N66001-02-C-8080

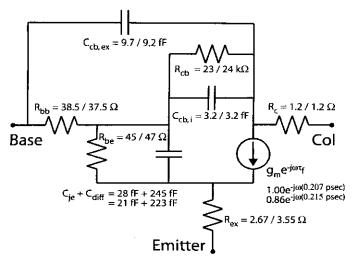

Figure 3: Hybrid-π model, 42 / 25 nm transitions

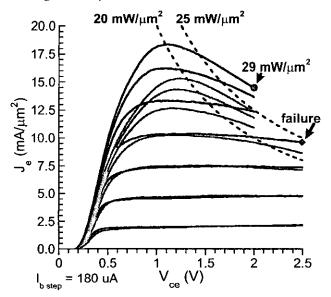

Figure 4: High power density Common-emitter curves 42 nm transition black, 25 nm transition blue

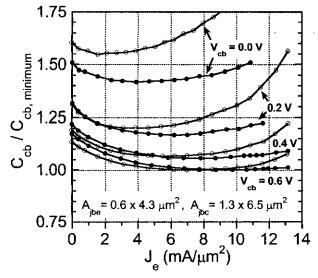

Figure 5:  $C_{cb}$  variation w/ bias 42 nm transition filled, 25 nm transition hollow

## V. Discussion

Figures 3, 4 and 5 show a direct comparison of the two DHBTs. The hybrid-model shows that the devices have similar values of resistive and capacitive parasitics--thus performance disparity can be focused on the different B-C grades. The common-emitter I-V curves from figure 4 are also comparable for  $J_e$  9 mA/ $\mu$ m<sup>2</sup>. At higher  $J_e$ , the 25 nm transition device suffers from current blocking while the 42 nm transition device behaves normally until  $J_e$  18 mA/ $\mu$ m<sup>2</sup>. We are certain that current blocking is observed because of the increase in  $C_{cb}$  shown in figure 5 at higher  $J_e$ . The inability of the 25 nm transition devices to operate well at high  $J_e$  may be due to imperfect design, deviation between design and growth, or more fundamental issues regarding the design of the graded layers. Further investigation is required.

Because InP has a higher breakdown field and higher thermal conductivity than InGaAs and InAlAs, it might be expected that the 25 nm transition devices show significantly improved  $V_{BR,CEO}$ ,  $_{JA}$ , or  $P_{max}$ . The data does not support these expectations. The lower  $_{JA}$  of the 42 nm transition devices at high  $J_e$   $J_{Kirk}$  is due in part to the relatively small electrostatic potential drop in the setback and grading layers of the collector.

#### References

- T. Enoki et al., "Prospects of InP-based IC technologies for 100-Gbit/sclass lightwave communications systems", *International Journal of High Speed Electronics and Systems*, Vol. 11, No. 1, pp. 137-158, 2001

- M.J.W. Rodwell et al., International Journal of High Speed Electronics and Systems, "Scaling of InGaAs/InAlAs HBTs for High Speed Mixed-Signal and mm-Wave ICs" Vol. 11, No. 1, pp. 159-215, 2001

- C. Nguyen et al., "Bandgap Engineered InP-Based Power Double Heterojunction Bipolar Transistors", Proceedings IEEE International Conference on Indium Phosphide and Related Materials, Cape Cod, MA, pp. 15-19, May, 1997

- M. Dahlström et al., "Wideband DHBTs Using a Graded Carbon-Doped InGaAs Base" IEEE Electron Device Letters, vol. 24, no. 7, pp. 433-435, 2003

- M. Ida et al., "High-Speed InP/InGaAs DHBTs with a Thin Pseudomorphic Base" Conference Proceedings IEEE GaAs IC, San Diego, CA, 9-12 Nov, pp. 211-214, 2003

- C.R. Bolognesi et al., "Type-II Base-Collector Performance Advantages and Limitations in High-Speed NpN Double Heterojunction Bipolar Transistors (DHBTs)", IEICE Trans. Electron., Vol. E86-C, No. 10, October, 2003

- H.J. Zhu et al., "GaAsSb-Based HBTs Grown By Production MBE System", Proceedings IEEE International Conference on Indium Phosphide and Related Materials, Kagoshima, Japan, 31 May - 4 June, pp. 338-341, 2004

- Z. Griffith et al., "InGaAs/InP DHBTs for Increased Digital IC Bandwidth having a 391 GHz f and 505 GHz fmax", IEEE Electron Device Letters, vol. 26, no. 1, pp. 11-13, 2005

- Z. Griffith et al., "Ultra High Frequency Static Dividers > 150 GHz in a Narrow Mesa InGaAs/InP DHBT Technology", Proc. IEEE Bipolar/BiCMOS Circuits and Technology Meeting, Montreal, Canada, 13-14 September, 2004

- I. Harrison et al., "Thermal Limitations of InP HBT's in 80 and 160 Gbits<sup>-1</sup> IC's" *IEEE Transactions on Electron Devices*, vol. 51, no. 4, pp. 529-534, 2004

- W. Liu, Handbook of III-V Heterojunction Bipolar Transistors, John Wiley and Sons Inc., 1998