# Transistor and Circuit Design for 100–200-GHz ICs

Zach Griffith, *Member, IEEE*, Yingda Dong, Dennis Scott, Yun Wei, Navin Parthasarathy, Mattias Dahlström, Christoph Kadow, Vamsi Paidi, Mark J. W. Rodwell, *Fellow, IEEE*, Miguel Urteaga, Richard Pierson, Petra Rowell, Bobby Brar, Sangmin Lee, Nguyen X. Nguyen, and Chahn Nguyen

Abstract—Compared to SiGe, InP HBTs offer superior electron transport properties but inferior scaling and parasitic reduction. Figures of merit for mixed-signal ICs are developed and HBT scaling laws introduced. Device and circuit results are summarized, including a simultaneous 450 GHz  $f_{\tau}$  and 490 GHz  $f_{\rm max}$  DHBT, 172-GHz amplifiers with 8.3-dBm output power and 4.5-dB associated power gain, and 150-GHz static frequency dividers (a digital circuit figure-of-merit for a device technology). To compete with advanced 100-nm SiGe processes, InP HBTs must be similarly scaled and high process yields are imperative. Described are several process modules in development: these include an emitter-base dielectric sidewall spacer for increased yield, a collector pedestal implant for reduced extrinsic  $C_{\rm cb}$ , and emitter junction regrowth for reduced base and emitter resistances.

*Index Terms*—InP heterojunction bipolar transistor, static frequency divider, millimeter-wave amplifier, dielectric sidewall-spacer, collector pedestal, emitter regrowth.

## I. INTRODUCTION

ESPITE formidable progress in CMOS, bipolar transistors remain competitive due to the larger breakdown voltages obtainable and the larger lithographic feature sizes required

Manuscript received March 3, 2005; revised June 5, 2005. The reported work from University of California Santa Barbara was supported by the Defense Advanced Research Projects Agency (DARPA) under the TFAST program N66001-02-C-8080, by the Office of Naval Research under N0014-04-1-0071, N00014-01-1-0024, and N00014-99-1-0041, and by the Jet Propulsion Laboratory (JPL) President's Fund. The reported work from Rockwell Scientific Corporation (RSC) and Global Communication Semiconductors (GCS) was sponsored by the DARPA TFAST program.

- Z. Griffith, N. Parthasarathy, C. Kadow, and M. J. W. Rodwell are with the Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106-9560 USA (e-mail: griffith@ece.ucsb.edu).

- Y. Dong was with the Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106-9560 USA. He is now with the SanDisk Corporation, Sunnyvale, CA 94089 USA.

- D. Scott was with the Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106-9560 USA. He is now with Northrup Grumman Space Technology, Redondo Beach, CA 90278 USA.

- Y. Wei was with the Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106-9560 USA. He is now with RF Micro Devices, Charlotte, NC 28269 USA.

- M. Dahlström was with the Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106-9560 USA. He is now with the IBM Microelectronics Semiconductor Research and Development Center, Essex Junction, VT 05452 USA.

- V. Paidi was with the Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106-9560 USA. He is now with Maxlinear Inc., Carlsbad, CA 92008 USA.

- M. Urteaga, R. Pierson, P. Rowell, and B. Brar are with the Rockwell Scientific Corporation, Thousand Oaks, CA 91360 USA.

- S. Lee and N. X. Nguyen are with Global Communication Semiconductors, Torrance, CA 90505 USA.

- C. Nguyen was with Global Communication Semiconductors, Torrance, CA 90505 USA. He is now with the Rockwell Scientific Corporation, Thousand Oaks, CA 91360 USA.

Digital Object Identifier 10.1109/JSSC.2005.854609

for a transistor at a given bandwidth. Compared to SiGe, InP heterojunction bipolar transistors (HBTs) have  $\approx 3.5:1$  higher collector electron velocity and  $\approx$  10:1 higher base electron diffusivity. Consequently, at the same scaling generation InP HBTs would have  $\approx 3.1$  greater bandwidth than SiGe HBTs. Today the maturity of advanced silicon processes has enabled SiGe HBTs to be fabricated with 100-nm emitter junctions with minimal extrinsic parasitics, while efforts to similarly scale InP HBTs have just begun. With that, SiGe HBTs have demonstrated simultaneous 300 GHz  $f_{\tau}$  and 350 GHz  $f_{\text{max}}$  [1] and 102 GHz static frequency dividers [2], while InP DHBTs have obtained simultaneous 450 GHz  $f_{\tau}$  and 490 GHz  $f_{\rm max}$ [3], 176 GHz power amplifiers with 5-dB power gain [4], and >150 GHz static frequency dividers [5]–[8]. Consequently, the two technologies today have comparable bandwidth, with SiGe offering much higher levels of integration. Improved bandwidth and integration of InP HBTs therefore requires great consideration be given to scaling laws and limits, and the requirements placed upon transistor design for wide-band circuits must be clearly understood, where the ensuing fabrication processes must provide high yield at 100-nm scaling [9].

## II. HBT PERFORMANCE METRICS

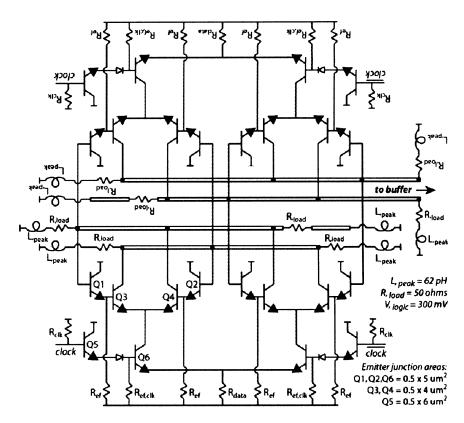

Although readily measured and widely reported in the device literature, transistor asymptotic unity current gain  $f_{\tau}$  and unity power gain  $f_{\mathrm{max}}$  cutoff frequencies are of limited value in predicting the speed of logic, mixed-signal, or optical transmission ICs, and transistors designed exclusively for high values of these parameters may perform poorly in circuits. For HBTs, an emitter-coupled logic (ECL) master-slave (M-S) latch is a representative small-scale mixed-signal circuit. Such latches serve as decision circuits in optical receivers, as latched comparators in ADCs, and as timing control elements in larger ICs. An M-S latch with inverting feedback (Fig. 1) forms a 2:1 static frequency divider, the maximum clock frequency  $f_{\rm clk,max}$  of which serves as a convenient and popular speed benchmark of a mixed-signal IC technology. From charge control analysis, [10], [12],  $T_{\text{gate}} = 1/(2f_{\text{clk,max}})$  is approximately a sum of RC delays  $T_{\text{gate}} = \sum a_{ij} R_i C_j$ . Table I lists the delay coefficients  $a_{ij}$ and Table II the components of  $T_{\mathrm{gate}}$  for an HBT design with target 260 GHz  $f_{\rm clk,max}$  [10], [11].  $\Delta V_L = R_{\rm load} I_c$  is the logic voltage swing,  $R_{load}$  the load resistance,  $I_c$  the collector current,  $R_{\rm ex}$  and  $R_{bb}$  the emitter and base parasitic series resistances,  $C_{ie}$  the emitter depletion capacitance,  $C_{cbx}$  and  $C_{cbi}$  the components of the collector depletion capacitance  $C_{\mathrm{cb}}$  external to and internal to  $R_{bb}$ ,  $\tau_f$  the sum of base  $\tau_b$  and collector  $\tau_c$ transit times, and  $\tau_w$  the propagation delay on the signal wiring bus (Fig. 1).

Fig. 1. Circuit schematic; 2:1 static frequency divider.

TABLE I TOP—DELAY COEFFICIENTS  $a_{ij}$  FOR AN ECL M-S LATCH, WHERE  $T_{\mathrm{gate}} = (2f_{\mathrm{clk,max}})^{-1} = \sum a_{ij}R_iC_j$ . BOTTOM—PROPORTION OF  $T_{\mathrm{gate}}$  DELAY FOR A 300-nm SCALING-GENERATION HBT, WITH TARGET 260 GHz CLOCK RATE

|                  | $C_{je}$ | $C_{cbx}$ | $C_{cbi}$ | $	au_f I_c/\Delta V_L$  | $	au_w I_c \ / \ \Delta V_L$ |      |

|------------------|----------|-----------|-----------|-------------------------|------------------------------|------|

| $\Delta V_L/I_c$ | 1        | 6         | 6         | 1                       | 1                            |      |

| $kT/qI_c$        | 0.5      | 1         | 1         | 0.5                     | 0                            |      |

| $R_{ex}$         | -0.3     | 0.5       | 0.5       | 0.5                     | 0                            |      |

| $R_{bb}$         | 0.5      | 0         | 1         | 0.5                     | 0                            |      |

|                  | $C_{je}$ | $C_{cbx}$ | $C_{cbi}$ | $\tau_f I_c/\Delta V_L$ | $\tau_w I_c/\Delta V_L$      | sum  |

| $\Delta V_L/I_c$ | 11%      | 16%       | 22%       |                         |                              | 49%  |

| $\Delta V_L/I_c$ |          |           |           | 15%                     | 18%                          | 33%  |

| $kT/qI_c$        |          |           |           | 1%                      |                              | 1%   |

| $R_{ex}$         | -1%      |           |           | 1%                      |                              | 0%   |

| $R_{bb}$         | 5%       |           | 3%        | 7%                      |                              | 15%  |

| sum              | 16%      | 16%       | 25%       | 24%                     | 18%                          | 100% |

| •                |          | 42%       |           |                         |                              |      |

The base and collector transit times play a relatively minor role in logic speed, with only 24% of  $T_{\rm gate}$  arising from  $\tau_f$  for the HBT of Table II. This is in contrast to the much stronger relative contribution of transit times to  $f_{\tau}$ , with  $\tau_f$  typically contributing 80% of  $\tau_{ec}=1/2\pi f_{\tau}$ . Depletion capacitance charging times  $C\Delta V_L/I_c$  dominate over transit delays in digital circuits because  $\Delta V_L\gg kT/q$ , as is required for digital noise margin. Examining the total delay  $\Sigma a_{ij}R_iC_j$  in terms of resistances, 49% of  $T_{\rm gate}$  is associated with the load resistance

TABLE II

TECHNOLOGY ROADMAPS FOR 40, 80, 160 Gb/s ICs, ASSUMING AN MS

D-LATCH MAXIMUM CLOCK FREQUENCY 1.5:1 HIGHER THAN THE DATA

RATE. MASTER-SLAVE LATCH DELAY INCLUDES 10% INTERCONNECT DELAY

| Parameter                                                           | Gen. 1             | Gen. 2      | Gen. 3            |

|---------------------------------------------------------------------|--------------------|-------------|-------------------|

| MS D-latch speed                                                    | 60 GHz             | 121 GHz     | 260 GHz           |

| Emitter width (µm)                                                  | 1.0                | 0.8         | 0.3               |

| Parasitic resistivity $\rho_{ex}$ , $(\Omega \cdot \mu \text{m}^2)$ | 50                 | 20          | 5                 |

| Base thickness (nm)                                                 | 40                 | 40          | 30                |

| Doping (cm <sup>-3</sup> )                                          | 5·10 <sup>19</sup> | $7.10^{19}$ | $7 \cdot 10^{19}$ |

| Sheet resistance (Ω/sq)                                             | 750                | 700         | 700               |

| Contact resistance $\rho_{v,b}$ $(\Omega \cdot \mu \text{m}^2)$     | 150                | 20          | 20                |

| Collector width (µm)                                                | 3                  | 1.6         | 0.7               |

| Collector thickness (nm)                                            | 300                | 200         | 100               |

| Current density (mA/ $\mu$ m <sup>2</sup> )                         | 1                  | 2.3         | 12                |

| $A_{collector}$ / $A_{emitter}$                                     | 4.55               | 2.6         | 2.9               |

| $f_{	au}$ (GHz)                                                     | 170                | 248         | 570               |

| $f_{max}$ (GHz)                                                     | 170                | 411         | 680               |

| $I_c$ / $L_e$ (mA/ $\mu$ m)                                         | 1                  | 1.9         | 3.7               |

| $	au_f$ (ps)                                                        | 0.67               | 0.50        | 0.22              |

| $C_{cb}$ / $I_c$ (ps/V)                                             | 1.7                | 0.62        | 0.26              |

| $C_{cb} \cdot \Delta V_l / I_c$ (ps)                                | 0.5                | 0.19        | 0.09              |

| $R_{bb}$ / ( $\Delta V_l$ / $I_c$ )                                 | 0.8                | 0.68        | 0.99              |

| $C_{je} \cdot \Delta V_l / I_c$ (ps)                                | 1.7                | 0.72        | 0.15              |

| $R_{ex}$ / ( $\Delta V_l$ / $I_c$ )                                 | 0.1                | 0.15        | 0.17              |

$\Delta V_L/I_c$ . High current density is thus essential. For adequate logic noise margin,  $\Delta V_L$  must be at least  $\sim 4(kT/q + R_{\rm ex}I_e)$ , hence increased current density must be accompanied by

reduced emitter resistance, so as to maintain a small  $\Delta V_L$ . Although not evident in Table I,  $R_{\rm ex}$  thus has a large indirect effect on  $f_{\rm clk,max}$ , as increased  $R_{\rm ex}$  forces increased  $\Delta V_L$ . Examined in terms of capacitances, 58% of  $T_{\rm gate}$  arises from the depletion capacitances  $C_{\rm cb}+C_{\rm je}$ , even given the assumed HBT design having small C/I ratios. For logic and mixed-signal ICs, low  $C_{\rm cb}\cdot \Delta V_L/I_c$  charging time is critical, necessitating very high current density, minimal excess collector junction area, and very low emitter access resistance.

For reactively-tuned amplifiers [13] in radio transceivers,  $f_{\rm max}$  defines the highest frequency at which power gain can be obtained, and is therefore directly relevant.  $f_{\tau}$  has significant but secondary importance; when tuned for maximum power gain, a transistor with a high  $f_{\rm max}/f_{\tau}$  ratio requires a high ratio of load resistance to transistor input resistance. The required high impedance tuning ratio aggravates matching-network resistive losses—already considerable in >100 GHz ICs—and thereby reduces gain. In receivers, amplifiers are tuned not for maximum gain but for minimum noise figure, while in transmitters, amplifiers are tuned for maximum efficiency and for maximum saturated power output. Gain expressions under such constraints are complex.

At a given scaling generation, the HBT base and collector layers can be thinned for highest feasible  $f_{\tau}$  while sacrificing both  $f_{\rm max}$  and logic speed, but such transistors are of limited value in circuits. Of greater value are balanced and proportional reductions of all transistor parasitics, such that all circuits employing the transistor exhibit a proportional increase in bandwidth.

## III. SCALING: LAWS, LIMITATIONS, AND ROADMAPS

Approximate HBT scaling laws derived in [11] are here summarized. For a  $\gamma$ : 1 bandwidth increase in an arbitrary circuit using the transistor, all transistor capacitances and transit delays must be reduced  $\gamma$ : 1 while maintaining constant all parasitic resistances, all bias and signal voltages, the transconductance  $g_m$ , and the operating current  $I_c$ . Reducing the collector depletion layer thickness  $T_c$  by  $\gamma:1$  and base thickness  $T_b$ by  $\gamma^{1/2}$ : 1 reduces  $\tau_f$  by the required proportion but would increase  $C_{\rm cb}$  if junction areas were held constant. Reducing the emitter and collector junction areas in proportion to  $\gamma^2$ : 1 then results in the desired  $\gamma:1$  reduction in  $C_{\rm cb}$ . Because the total base resistance is only weakly dependent upon the emitter junction width (contact and link resistance dominate over spreading resistance) but varies as the inverse of the emitter junction stripe length, reducing the emitter and collector junction widths in proportion to  $\gamma^2$ : 1 will maintain constant  $R_{bb}$ while effecting the needed  $\gamma^2$ : 1 reduction in emitter junction area. With constant  $I_c$ , but with the emitter junction area reduced in proportion to  $\gamma^2$ : 1, the emitter current density increases:  $J_e \propto \gamma^2$ . This is feasible within the limits imposed by the Kirk effect, as  $J_{\rm Kirk} \propto 1/T_c^2 \propto \gamma^2$ . Because the emitter parasitic resistance  $R_{\rm ex}$  must remain constant in the presence of a  $\gamma^2$ : 1 reduction in emitter junction area  $A_e$ , the normalized emitter contact resistivity  $\rho_{\rm ex}=R_{\rm ex}A_e$  must be reduced rapidly, with  $\rho_{\rm ex} \propto 1/\gamma^2$ . Because operating  $J_e$  increases in proportion to the bandwidth squared, the maximum reliable

TABLE III SUMMARY OF SIMULTANEOUS PARAMETER SCALING FOR A  $\gamma:1$  INCREASE IN HBT AND CIRCUIT BANDWIDTH

| key device parameter                                                 | required change             |

|----------------------------------------------------------------------|-----------------------------|

| collector depletion layer thickness                                  | decrease $\gamma$ :1        |

| base thickness                                                       | decrease $\sqrt{\gamma}$ :1 |

| emitter junction width                                               | decrease $\gamma^2$ :1      |

| collector junction width                                             | decrease $\gamma^2$ :1      |

| emitter contact resistivity, $ ho_{ex}$                              | decrease $\gamma^2$ :1      |

| current density                                                      | increase $\gamma^2$ :1      |

| base contact resistivity – if contacts lie above B-C junction        | decrease $\sim \gamma^2$ :1 |

| base contact resistivity – if contacts do not lie above B-C junction | unchanged                   |

power density  $P/A_e = J_e V_{ce} \propto \gamma^2 V_{ce}$  is a more significant applied voltage limit than the low-current breakdown voltages  $BV_{CEO}$  or  $BV_{CBO}$ .

Scaling requirements for the base contact resistivity and for the emitter depletion thickness are not easily summarized here [11]. The emitter depletion layer thickness need not be scaled as rapidly as that of the collector, hence  $C_{\rm je}$  becomes progressively less significant with scaling. If the base Ohmic contacts lie above the collector-base junction, then their width must reduced  $\gamma:1$  to obtain the requisite reduction in  $C_{\rm cb}$ ; this necessitates a  $\sim \gamma^2:1$  reduction in the base contact resistivity  $\rho_{v,b}$ . It the contacts do not lie above the junction, their resistivity can remain unchanged. These scaling laws are summarized in Table III.

Consider specifically the impact of this scaling on ECL logic speed. With a  $\gamma:1$  scaling, the collector thickness  $T_c$  is reduced  $\gamma:1$ , the current density increased  $\gamma^2:1$ , and the dominant delay  $C_{\rm cb}\cdot \Delta V_L/I_c$  reduced  $\gamma:1$ . The parasitic voltage drop  $R_{\rm ex}I_c=\rho_{\rm ex}J_e$  remains constant only because  $\rho_{\rm ex}$  is reduced rapidly, being proportional to  $1/\gamma^2$

Base  $\rho_{v,b}$  and emitter  $\rho_{\rm ex}$  contact resistivity, thermal resistance  $\theta_{\rm JA}$ , and fabrication yield of submicron features are the key barriers to further scaling [11], [14]. Current density must increase, and emitter and base contact resistivities must decrease in proportion to the *square* of circuit bandwidth. Thermal resistance normalized to the emitter junction area  $\theta_{\rm JA}A_e$ , must also be reduced in proportion to the square of circuit bandwidth. Table II shows a prospective HBT scaling roadmap for increased digital logic speed; note in particular that at  $\sim\!260$  GHz target clock rate, the emitter contact resistivity must be  $\sim\!5~\Omega~\cdot\mu{\rm m}^2$ , the current density  $12~{\rm m}A/\mu{\rm m}^2$ , and the normalized thermal resistance  $\sim\!5~{\rm K}~\cdot\mu{\rm m}^2/{\rm mW}$ .

Consider a future HBT having 1 THz  $f_{\tau}$  and  $f_{\rm max}$ . Its emitter width would be  $\sim$ 75 nm, feasible with present lithographic tools. But, to be properly scaled so as to enable, e.g.,  $\sim$ 500 GHz digital clock rates  $\sim$ 1 K  $\cdot$   $\mu$ m $^2$ /mW thermal resistance and  $\sim$ 1  $\Omega \cdot \mu$ m $^2$  emitter contact resistivity would be required. It is not yet clear how to obtain such parameters.

# IV. TRANSISTOR AND IC RESULTS FOR MESA HBTS

At a given scaling generation, defined by the minimum emitter feature size, different transistor layer structures are

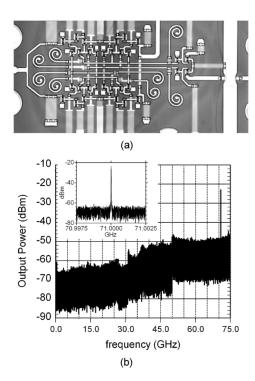

Fig. 2. Fabricated and measured results of UCSB static frequency divider. (a) Circuit photograph of static divider signal bus, (b) Output spectum of divide-by-2 circuit at 71 GHz,  $f_{\rm clock}=142$  GHz.

preferred so as to obtain a differing balance of device parasitics that are more suited for the particular application—i.e., mm-wave tuned amplifiers benefit from high  $f_{\rm max}$  and can tolerate moderately lower  $f_{\tau}$ , whereas digital IC speed benefits from devices having simultaneously high values of  $f_{\tau}$  and  $f_{\rm max}$ , and demands low  $C_{\rm cb} \cdot \Delta V_L/I_c$  and low  $R_{\rm ex} \cdot I_c/\Delta V_L$ . Amongst different HBT designs, numerous device and circuit results have recently been reported.

Two device designs intended for use in high-speed logic have been investigated at the University of California at Santa Barbara (UCSB) with 150-nm and 120-nm drift-collector thickness  $T_c$ . The HBT having 150-nm  $T_c$  obtained a simultaneous 391 GHz  $f_{\tau}$ , 505 GHz  $f_{\rm max}$ , and  $C_{\rm cb}/I_c=0.51$  ps/V when biased at  $J_e=5.17$  mA/ $\mu$ m² and  $V_{\rm cb}=0.6$  V. The common-emitter breakdown voltage BV<sub>CEO</sub> was 5.1 V [15]. From this device design, ECL static frequency dividers were designed and fabricated at UCSB and at GCS (Fig. 1). Divide-by-2 circuits fabricated at UCSB produced an  $f_{\rm clk,max}=142$  GHz (Fig. 2), [15], and utilizing the same collector structure an  $f_{\rm clk}\geq150$  GHz static divider (Fig. 3) was demonstrated from GCS [5]. For the 150 GHz divider, the key device parameters of the HBTs within the circuit at their respective bias conditions are given in Table IV.

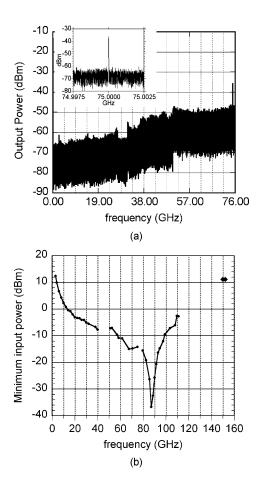

From the 120-nm  $T_c$  design, 450 GHz  $f_{\tau}$ , 490 GHz  $f_{\rm max}$ , and  $C_{\rm cb}/I_c=0.36$  ps/V were obtained at a bias of  $J_e=8.7~{\rm mA}/{\mu}{\rm m}^2$  and  $V_{\rm cb}=0.6$  V.  ${\rm BV}_{\rm CEO}$  was 3.9 V [3]. The DC common-emitter IV characteristics and measured microwave gains are shown in Fig. 4.

Devices with a collector  $T_c = 100$  nm were explored to investigate the effectiveness of the InGaAs/InAlAs chirped-superlattice base-collector grade [16] at higher current densi-

Fig. 3. Measured results of 150 GHz static frequency divider—UCSB design, GCS fabrication. (a) Output spectum of divide-by-2 circuit at 75 GHz,  $f_{\rm clock} = 150$  GHz, (b) Input signal sensitivity plot.

TABLE IV

KEY DEVICE PARAMETERS (Fig. 1) OF THE 150-GHz STATIC DIVIDER

|              | units            | Q1, Q2  | Q3, Q4  | Q5      | Q6      |

|--------------|------------------|---------|---------|---------|---------|

| $A_e$        | $\mu$ m $^2$     | 0.5 × 5 | 0.5 × 4 | 0.5 × 6 | 0.5 × 5 |

| $J_e$        | mA/ $\mu$ m $^2$ | 4.0     | 6.0     | 3.3     | 4.8     |

| $C_{cb}/I_c$ | ps/V             | 0.99    | 0.59    | 0.86    | 0.59    |

| $V_{cb}$     | V                | 0.0     | 0.6     | 1.7     | 0.6     |

| $f_{	au}$    | GHz              | 260     | 301     | 280     | 301     |

| $f_{max}$    | GHz              | 268     | 358     | 280     | 358     |

ties. 491 GHz  $f_{\tau}$ , 415 GHz  $f_{\rm max}$ , and  $C_{\rm cb}/I_c=0.57$  ps/V was measured at  $J_e=10.3$  mA/ $\mu$ m² and  $V_{\rm cb}=0.4$  V, while BV<sub>CEO</sub> = 3.1 V [17].  $J_{\rm Kirk}\approx 15$  mA/ $\mu$ m², at  $V_{\rm ce}=1.0$  V. Thermal failure is at 25–30 mW/ $\mu$ m², hence the devices can be biased at  $V_{\rm ce}=2$  V while carrying 13 mA/ $\mu$ m². The devices thus far discussed have a  $0.6\times 4.3~\mu$ m² emitter junction area  $A_{\rm je}$ , a collector to emitter width ratio = 2.2, and employ an evaporated self-aligned base contact. The reduced  $f_{\rm max}/f_{\tau}$  ratio of the HBTs with  $T_c=100$  nm reflects insufficient lateral scaling of the emitter and collector junctions.

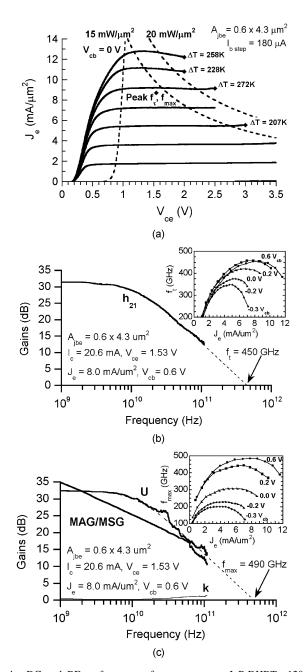

Devices intended for power amplifiers employing a 210-nm collector  $T_c$  obtained a simultaneous 276 GHz  $f_{\tau}$ , 451 GHz

Fig. 4. DC and RF performance of a narrow-mesa InP-DHBT—120-nm collector, 30-nm base. (a) Common-emitter I-V characteristics at high power density, (b) Measured microwave gains at peak  $f_{\tau}$ , DC-110 GHz, (c) Measured microwave gains at peak  $f_{\max}$ , DC-110 GHz.

$f_{\rm max}$ , and  $C_{\rm cb}/I_c=0.65$  ps/V, with  ${\rm BV_{CEO}}=6.9$  V. An ensemble of different medium power amplifiers were fabricated from this collector structure and have been reported [4]—among them include a 176-GHz common-base amplifier with 8.3-dBm output power and 4.5-dB associated power gain, shown in Fig. 5. The common-base configuration is employed because it has higher maximum stable gain (MSG) than common-emitter. This MSG is further increased by minimizing the base feed inductance and collector-emitter overlap capacitance  $C_{\rm ce}$ . Stage gain was limited on this amplifier due to  $f_{\rm max}$  decreasing ( $\approx$  300 GHz) to below design values (450 GHz) on the wafer carrying amplifiers.

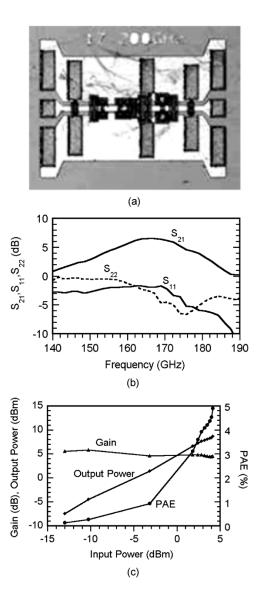

Fig. 5. Fabricated and measured results of InP-DHBT power amplifiers. (a) Circuit photograph of 172-GHz one-stage MMIC amplifier. (b) Small-signal S-parameters, 140–220 GHz. (c) Amplifier power gain at 172 GHz.

# V. ADVANCED INP HBT PROCESS MODULES

# A. Dielectric Sidewall Spacers—LSI Level Device Yield

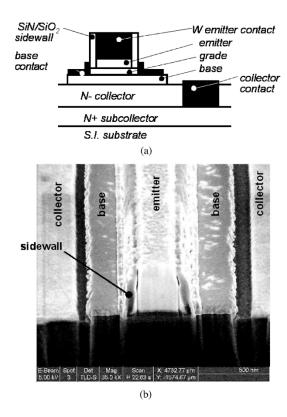

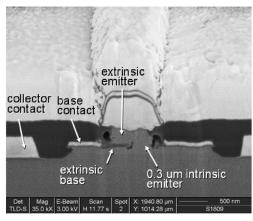

The mesa HBTs described above suffer limited yield from the self-aligned emitter-base etch/liftoff process. Further, doubling circuit speed requires emitter  $\rho_c \approx 5\,\Omega\cdot\mu\mathrm{m}^2$  and narrow 200-nm base contacts. Dielectric sidewall spacer processes eliminate the need for evaporated self-aligned base contacts [18], and by doing so, emitter-base short-circuits associated with liftoff are avoided. Furthermore, the sidewall spacer allows for very thin emitter semiconductor layers, minimizing undercut during mesa formation. Fig. 6 shows an early prototype HBT with an emitter dielectric sidewall. More advanced processes at Rockwell Scientific have produced high HBT yield at 0.25- $\mu$ m emitter width, demonstrating devices with 326 GHz  $f_{\tau}$ , 305 GHz  $f_{\rm max}$ , and  $C_{\rm cb}/I_c < 0.55$  ps/V [19].

Fig. 6. Dielectric sidewall spacer process. (a) Sidewall process schematic. (b) SEM cross section of a fabricated device.

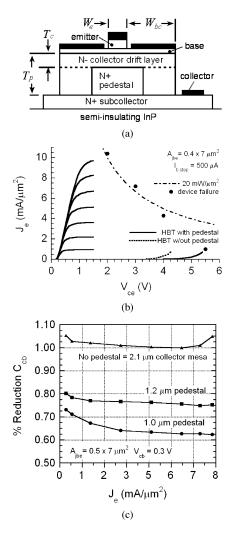

# B. Collector Pedestal Implant—Reduced $C_{\rm cb}$

At the 0.25- $\mu$ m emitter (width) scaling generation, a significant challenge is maintaining an acceptably small collector to emitter junction area ratio  $A_{jc}/A_{ie}$ . While the base contact transfer length  $L_T$  is 200 nm for a base contact  $ho_{v,b} = 20 \, \Omega \cdot \mu \text{m}^2$ to an  $R_{\rm sheet} = 500 \,\Omega$ , 200-nm-wide base contacts present challenges in process design for high yield fabrication, and in addition present significant bulk metal resistance along the length of the base contact. Closely following the SiGe device structure [20], an implanted  $N^+$  collector pedestal reduces the capacitance underneath where the base contact lies [Fig. 7(a)], permitting somewhat higher base contact resistivities and wider base contacts at a given level of device performance. The pedestal also substantially reduces the  $C_{\rm cb}$  associated with the large base-pad interconnect used in some device technologies. Pedestals can be used with mesa, dielectric-sidewall, or regrown emitter-base junction HBTs.

Initial pedestal HBT results from UCSB [21] have demonstrated high quality regrowth of the active device layers with expected common-emitter I–V characteristics shown in Fig. 7(b). Gummel characteristics of these devices show low leakage currents ( $I_{cbo}=320~{\rm pA}$  at  $V_{\rm cb}=0.3~{\rm V}$ ) with collector and base ideality factors of  $n_c=1.14$  and  $n_b=1.25$ , respectively. RF device performance suffered from high emitter resistance ( $\rho_c\approx90~\Omega\cdot\mu{\rm m}^2$ ) due to errors made in device fabrication and only 170 GHz  $f_{\tau}$  and 150 GHz  $f_{\rm max}$  were measured. With pedestal implants, there has been observed both significantly reduced  $C_{\rm cb}$  [Fig. 7(c)] together with moderately increased device

Fig. 7. Topology and electrical performance for a UCSB pedestal InP HBT. (a) Pedestal process schematic. (b) Common-emitter I-V characteristics for the pedestal HBT. (c) Amount of  $C_{\rm cb}$  reduction for varying pedestal width.

breakdown voltage—where on the same wafer  $BV_{CEO}=4.0~V$  and 3.3 V (at  $I_c=50~\mu A$ ) for a 100-nm drift-collector  $T_c$  with and without the pedestal, a 20% increase. The high-field region of the drift-collector for the pedestal device is now buried within the collector mesa (above the pedestal implant), such that surface breakdown effects associated with the  $\approx 10^{12}~cm^{-2}$  (N-type) surface state charge density typical of ill-passivated InP surfaces have a reduced effect. Increased breakdown in collector pedestal InP DHBTs has also been observed and reported in [22].

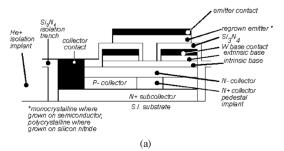

### C. Emitter Junction Regrowth

Dielectric sidewall and collector pedestal processes address neither base nor emitter contact resistivity scaling limits. Again, closely following the SiGe device structure, there has been developed an HBT process flow [Fig. 8(a)] in which a low-resistivity polycrystalline InAs regrowth forms a T-shaped emitter whose ohmic contact is much larger than the emitter junction for reduced  $R_{\rm ex}$ . Such reductions of emitter resistance through an increased contact/junction area ratio is an alternative to materials engineering for reduced emitter access resistance.

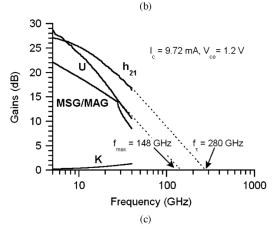

Fig. 8. Regrown-emitter InP-HBT topology and results from UCSB. (a) Schematic of regrown-emitter III–V HBT. (b) SEM cross section of regrown HBT. (c) Measured microwave gains at peak  $f_{\tau}$  and  $f_{\rm max}$ .

Recall that an emitter  $\rho_c \approx 5~\Omega \cdot \mu \text{m}^2$  is targeted for 260-GHz clock rate, a resistivity  $\approx 1.6:1$  better than the best reported results thus far obtained [17]. The emitter regrowth process also permits an extrinsic base region of  $N_A > 10^{20}~\text{cm}^{-3}$  doping and a total extrinsic and intrinsic thickness of 100 nm for reduced base resistance  $R_{bb}$ . Self-aligned refractory base ohmic contacts lie under the extrinsic emitter regions.

Regrown-emitter devices from UCSB have demonstrated 280 GHz  $f_{\tau}$  and 148 GHz  $f_{\rm max}$  in such processes [23], shown in Fig. 8(b). Presently, device performance is limited by both difficulties in emitter regrowth over the edges of the emitter etch window [Fig. 8(c)] and by partial passivation of the base doping by hydrogen associated with the PECVD  ${\rm Si_3N_4}$  deposition process. The fabrication process is now being substantially revised, where a fully epitaxial regrown-emitter InP HBT process is now being pursued with initial results reported in [24].

#### ACKNOWLEDGMENT

For the results reported here, the mesa DHBT material and emitter-regrowth templates were grown by commercial vendor IQE Inc., Bethlehem, PA. The authors would like to thank Dr. A. W. K. Liu and Dr. J. M. Fastenau of IQE, and Dr. N. Harff and J. Prairie of the Mayo Clinic Special Purpose Processor Development Group (SPPDG) for the testing of the dividers reported here >113 GHz.

## REFERENCES

- [1] M. Khater, J.-S. Rieh, T. Adam, A. Chinthakindi, J. Johnson, R. Krishnasamy, M. Meghelli, F. Pagette, D. Sanderson, C. Schnabel, K. T. Schonenberg, P. Smith, K. Stein, A. Stricker, S.-J. Jeng, D. Ahlgren, and G. Freeman, "SiGe HBT Technology with  $f_{\rm max}/f_{\tau}=350/300$  GHz and gate delay below 3.3 ps," *Proc. IEEE Int. Electron Device Meeting*, pp. 247–250, Dec. 2004.

- [2] J. Böck, H. Schäfer, H. Knapp, K. Aufinger, M. Wurzer, S. Boguth, T. Böttner, R. Stengl, W. Perndl, and T. F. Meister, "3.3 ps SiGe bipolar technology," *Proc. IEEE Int. Electron Device Meeting*, pp. 255–258, Dec. 2004.

- [3] Z. Griffith, M. J. W. Rodwell, X.-M. Fang, D. Lubyshev, Y. Wu, J. M. Fastenau, and W. K. Lui, "InGaAs/InP DHBTs with 120 nm collector having simultaneously high  $f_{\tau}$ ,  $f_{\rm max} \geq 450$  GHz," *IEEE Electron Device Lett.*, vol. 26, no. 8, pp. 530–532, Aug. 2005.

- [4] V. Paidi, Z. Griffith, Y. Wei, M. Dahlström, M. Urteaga, N. Parthasarathy, M. Seo, L. Samoska, A. Fung, and M. J. W. Rodwell, "G-band (140–220 GHz) and W-band (75–110 GHz) InP DHBT medium power amplifiers," *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 2, pp. 598–605, Feb. 2005

- [5] Z. Griffith, M. Dahlström, M. J. W. Rodwell, M. Urteaga, R. Pierson, P. Rowell, B. Brar, S. Lee, N. Nguyen, and C. Nguyen, "Ultra high frequency static dividers >150 GHz in a narrow mesa InGaAs/InP DHBT technology," in *Proc. IEEE Bipolar/BiCMOS Circuits and Technology Meeting*, Montreal, QC, Canada, Sep. 2004, pp. 176–179.

- [6] G. He, J. Howard, M. Le, P. Partyka, B. Li, G. Kim, R. Hess, R. Bryie, R. Lee, S. Rustomji, J. Pepper, M. Kail, M. Helix, R. Elder, D. Jansen, N. Harff, J. Prairie, E. Daniel, and B. Gilbert, "Self-Aligned InP DHBT with  $f_{\tau}$  and  $f_{\text{max}}$  over 300 GHz in a new manufacturable technology," *IEEE Electron Device Lett.*, vol. 25, no. 8, pp. 520–522, Aug. 2004.

- [7] D. A. Hitko, T. Hussain, J. F. Jensen, Y. Royter, S. Morton, D. S. Matthews, R. D. Rajavel, I. Milosavljevic, C. H. Fields, S. Thomas III, A. Kurdoghlian, Z. Lao, K. Elliott, and M. Sokolich, "A low power (45 mW/latch) static 150 GHz CML divider," in *Proc. IEEE Compound Semiconductor Integrated Circuit Symp.*, Monterey, CA, Oct. 2004, pp. 167–170

- [8] D. Sawdai, P. C. Chang, V. Gambin, X. Zeng, J. Wang, M. Barsky, B. Chan, B. Oyama, A. Gutierrez-Aitken, and A. Oki, "Veritcal scaling of planarized InP/InGaAs heterojunction bipolar transistors with  $f_{\tau} > 350$  GHz and  $f_{\rm max} > 500$  GHz," presented at the IEEE Int. Conf. on Indium Phosphide and Related Materials, Glasgow, Scotland, U.K., May 2005.

- [9] J. Zolper, "Challenges and opportunities for InP HBT mixed signal circuit technology," in *Proc. IEEE Int. Conf. Indium Phosphide and Related Materials*, Santa Barbara, CA, May 2003, pp. 8–11.

- [10] M. J. W. Rodwell, M. Urteaga, Y. Betser, D. Scott, M. Dalhström, S. Lee, S. Krishnan, T. Mathew, S. Jaganathan, Y. Wei, D. Mensa, J. Guthrie, R. Pullela, Q. Lee, B. Agarwal, U. Bhattacharya, and S. Long, "Scaling of InGaAs/InAlAs HBTs for high speed mixed-signal and mm-wave ICs," *Int. J. High-Speed Electron. Syst.*, vol. 11, no. 1, pp. 159–215, 2001.

- [11] M. J. W. Rodwell, M. Urteaga, T. Mathew, D. Scott, D. Mensa, Q. Lee, J. Guthrie, Y. Betser, S. C. Martin, R. P. Smith, S. Jaganathan, S. Krishnan, S. I. Long, R. Pullela, B. Agarwal, U. Bhattacharya, L. Samoska, and M. Dahlström, "Submicron scaling of HBTs," *IEEE Trans. Electron Devices*, vol. 48, no. 11, pp. 2606–2624, Nov. 2001.

- [12] D. A. Hodges and H. G. Jackson, Analysis and Design of Digital Integrated Circuits. New York: McGraw-Hill, 1983.

- [13] T. H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, 2nd ed. Cambridge, U.K.: Cambridge Univ. Press, Mar. 2004.

- [14] I. Harrison, M. Dahlström, S. Krishnan, Z. Griffith, Y.-M. Kim, and M. J. W. Rodwell, "Thermal limitations of InP HBTs in 80- and 160-Gb ICs," IEEE Trans. Electron Devices, vol. 51, no. 4, pp. 529–534, Apr. 2004.

- [15] Z. Griffith, M. Dahlström, M. J. W. Rodwell, X.-M. Fang, D. Lubyshev, Y. Wu, J. M. Fastenau, and W. K. Lui, "InGaAs/InP DHBTs for increased digital IC bandwidth having a 391 GHz  $f_{ au}$  and 505 GHz  $f_{ ext{max}}$ ," IEEE Electron Device Lett., vol. 26, no. 1, pp. 11-13, Jan. 2005.

- [16] M. Dahlström, X.-M. Fang, D. Loubychev, M. Urteaga, S. Krishnan, N. Parthasarathy, Y.-M. Kim, and M. J. W. Rodwell, "Wideband DHBTs using a graded carbon-doped InGaAs base," IEEE Electron Device Lett., vol. 24, no. 7, pp. 433-435, Jul. 2003.

- [17] Z. Griffith, M. Dahlström, M. J. W. Rodwell, X.-M. Fang, D. Lubyshev, Y. Wu, J. M. Fastenau, and W. K. Lui, "In<sub>0,53</sub>Ga<sub>0,47</sub>As/InP Type-I DHBTs w/100-nm collector and 491 GHz  $f_{ au}$ , 415 GHz  $f_{ ext{max}}$ ," presented at the IEEE Int. Conf. Indium Phosphide and Related Materials, Glasgow, Scotland, U.K., May 2005.

- [18] T. Oka, K. Hirata, H. Suzuki, K. Ouchi, H. Uchiyama, T. Taniguchi, K. Mochizuki, and T. Nakamura, "Small-scale InGaP/GaAs heterojunction bipolar transistors for high-speed and low-power intergrated-circuit applications," Int. J. High-Speed Electron. Syst., vol. 11, no. 1, pp. 115-136, 2001.

- [19] M. Urteaga, P. Rowell, R. Pierson, B. Brar, M. Dahlström, Z. Griffith, M. J. W. Rodwell, S. Lee, N. Nguyen, and C. Nguyen, "Deep submicron InP DHBT technology with electroplated emitter and base contacts," in Proc. Device Research Conf., Notre Dame, IN, Jun. 2004, pp. 239–240.

- [20] J.-S. Rieh, M. Khater, K. T. Schonenberg, F. Pagette, P. Smith, T. N. Adam, K. Stein, D. Ahlgren, and G. Freeman, "Collector vertical scaling and performance tradeoffs in 300 GHz SiGe HBT," in Proc. Device Research Conf., Notre Dame, IN, Jun. 2004, pp. 235-236.

- [21] Y. Dong, Z. Griffith, M. Dahlström, and M. J. W. Rodwell, "Ccb reduction in InP heterojunction bipolar transistors with selectively implanted collector pedestal," Proc. Device Research Conf., pp. 67-68, Jun. 2004.

- [22] J. C. Li, M. Chen, D. A. Hitko, C. H. Fields, B. Shi, R. Rajavel, P. M. Asbeck, and M. Sokolich, "A submicrometer 252 GHz  $f_{\tau}$  and 283 GHz  $f_{

m max}$  InP DHBT with reduced  $C_{

m cb}$  using selectively implanted buried subcollector," IEEE Electron Device Lett., vol. 26, no. 3, pp. 136–138, Mar. 2005.

- [23] Y. Wei, D. Scott, Y. Dong, A. C. Gossard, and M. J. W. Rodwell, "280 GHz  $f_{\tau}$  InP DHBT with 1.2  $\mu$  m<sup>2</sup> base-emitter junction area in MBE regrown-emitter technology," in Proc. Device Research Conf., Notre Dame, IN, Jun. 2004, pp. 237-238.

- [24] C. Kadow, A. C. Gossard, and M. J. W. Rodwell, "Regrown-emitter InP HBTs," presented at the 22nd North American Conf. Molecular Beam Epitaxy, Alberta, Canada, Oct. 2004.

Zach Griffith (M'05) received the B.S., M.S., and Ph.D. degrees in electrical engineering in 1999, 2001, and 2005, respectively, from the University of California, Santa Barbara.

His continued efforts at UC Santa Barbara include the design and fabrication of increased bandwidth InP DHBTs beyond 500 GHz for use in high-speed digital and analog ICs operating beyond 250 GHz.

from Fudan University, Shanghai, China, in 1997, and the M.S. degree in physics from the University of Delaware in 1999, with thesis work on magnetic tunneling junction and MRAM devices. He received the Ph.D. degree in electrical engineering from the University of California, Santa Barbara, in 2004 with work on high-speed InP heterojunction bipolar

Currently, he is with SanDisk Corporation, Sunnyvale, CA, working on NAND flash memory devices.

Redondo Beach, CA.

Dennis Scott received the B.S. and M.S. degrees in electrical engineering from the University of Illinois, Urbana-Champaign, in 1996 and 1999, respectively. He then attended the University of California, Santa Barbara, from 1999 to 2004 pursuing the Ph.D. degree in electrical engineering. His primary research efforts were on HBT fabrication and process development, molecular beam epitaxy, and epitaxial regrowth.

He is currently working on HBT technology development at Northrop Grumman Space Technology,

Yun Wei received the Ph.D. degree in electrical engineering from the University of California, Santa Barbara, in 2003.

He is currently with the Infrastructure Product Line (IPL) of RF Micro Devices, Charlotte, NC. His research includes wide bandwidth power InP HBTs and its MMICs, quasi-optic arrays, ultrahigh frequency InP HBTs in MBE regrown-emitter technology, and GaN HEMT technology and its applications in power amplifiers and low noise amplifiers.

Navin Parthasarathy received the B.E. (Hons.) degree in electrical and electronic engineering and the M.Sc. (Hons.) degree in physics from the Birla Institute of Technology and Science, Pilani, India, in 2000. He is currently pursuing the Ph.D. degree at the University of California, Santa Barbara, under the supervision of Prof. Mark Rodwell.

His research work includes the design and fabrication of InP based high-speed transistors and circuits.

Mattias Dahlström received the M.Sc. degree in engineering physics and the Ph.D. degree in electrical engineering from The Royal Institute of Technology (KTH), Sweden, in 2003. His Ph.D. work on ultrahigh-speed InP HBTs was performed at the University of California, Santa Barbara, under the leadership of Prof. Mark Rodwell. His InP transistor work focused on achieving >300-GHz operation for transistors suitable for communication circuits. Key improvements were done in composite collector design, base transit time, parasitic resistances, and

current density, resulting in several state-of-the-art devices. Dr. Dahlström is now with IBM, Essex Junction, VT, developing high-speed SiGe HBTs.

Christoph Kadow received the Diploma degree in physics from the Ludwig-Maximilian Universität, Munich, Germany, in 1996, and the Ph.D. degree in materials science and engineering from the University of California, Santa Barbara, in 2000.

He currently is a project scientist in the department of Electrical and Computer Engineering at the University of California, Santa Barbara. His research interests are semiconductor devices and materials. The current focus of his work is high-bandwidth transistor design and associated process development. Previous

research efforts include the development of ErAs/GaAs nanoscale materials for photoconductive applications. He is an author or coauthor of 25 papers in technical journals.

Vamsi Paidi received the B.Tech. degree in electrical engineering from the Indian Institute of Technology, Madras, India, and the Ph.D. degree in electrical engineering from the University of California, Santa Barbara, in 2000 and 2004, respectively.

He is currently with Maxlinear Inc., Carlsbad, CA. His reaserch includes analog and mixed-signal circuit design for RF and microwave applications.

Mark J. W. Rodwell (F'03) received the B.S. degree from the University of Tennessee, Knoxville, in 1980, and the M.S. and Ph.D. degrees from Stanford University, Stanford, CA, in 1982 and 1988, respectively.

He is Professor and Director of the Compound Semiconductor Research Laboratories and the NSF Nanofabrication Users Network (NNUN) at the University of California, Santa Barbara. He was with AT&T Bell Laboratories, Whippany, NJ, during 1982–1984. His research focuses on high bandwidth InP bipolar transistors and multi-GHz bipolar circuit

design. His recent research activities also include microwave power amplifiers, and monolithic analog and digital transistor circuits operating above 100 GHz. He

Dr. Rodwell was the recipient of a 1989 National Science Foundation Presidential Young Investigator Award. His work on GaAs Schottky-diode ICs for subpicosecond/mm-wave instrumentation was awarded the 1997 IEEE Microwave Prize.

**Miguel Urteaga** received the B.A.Sc. degree in engineering physics from Simon Fraser University, Vancouver, BC, Canada, in 1998, and the M.S. and Ph.D. degrees in electrical engineering from the University of California, Santa Barbara, in 2001 and 2003, respectively.

Since 2003, he has been with the Rockwell Scientific Company, Thousand Oaks, CA. His research interests include device design and fabrication of high-speed InP HBTs, as well as the design of ultrahigh-frequency integrated circuits.

**Richard Pierson**, photograph and biography not available at the time of publication.

**Petra Rowell** received the B.S. degree in mathematics from California Lutheran University, Thousand Oaks, CA, in 1994.

She joined the Rockwell Scientific Company, Thousand Oaks, in 1994 where she has worked in the electrochemistry, laser optics, and electronics groups. Currently, she is in charge of the test operations in the electronics division of Rockwell Scientific.

**Bobby Brar** received the Ph.D. degree in electrical engineering from the University of California, Santa Barbara (UCSB), in 1995. At UCSB, he studied the InAs/AlSb/GaSb material system for high-speed electronic and optoelectronic applications.

In 1995, he joined the Nanoelectronics branch in the Central Research Laboratories at Texas Instruments Incorporated to work on InP-based resonant tunneling devices and field effect transistors for high-speed mixed-signal applications. Under the Ultra program sponsored by DARPA, he also

conducted research in ultrathin crystalline layers grown on silicon substrates to build resonant tunneling structures for silicon-based quantum devices. In 1998, he joined the Rockwell Scientific Company, Thousand Oaks, CA, and managed the Advanced III–V Devices and Materials department, overseeing research in InP, GaAs, GaN and Antimonide-based technologies for high-performance ICs. He is presently the Director of the Electronics Division at Rockwell Scientific, which focuses on the development of state-of-the-art components from MEMS to MMICs. He has published over 50 papers in technical journals.

**Sangmin Lee** received the M.S. and Ph.D. degrees in electrical engineering from the Department of Physics, Sogang University, Seoul, Korea, in 1992 and 1996, respectively.

In 1996, he developed all-optical switches up to  $4\times4$  channeling using RIE etching and selective regrowth techniques in a photonic device laboratory at the Electronics and Telecommunication Research Institute of Korea. Demonstrated were  $1\times2$ ,  $1\times4$ ,  $2\times2$  switch modules and  $4\times4$  switch sub modules. In 1999, he developed high-speed InP HBT devices

using transferred substrate techniques at the University of California, Santa Barbara. As a part of his work, a 462 GHz InP double heterojunction transistor was demonstrated. Since 2002, he has been with Global Communication Semiconductors Inc. as a Senior Engineer and participated in R&D projects pertaining to both photonic and electronic devices such as high-speed InP HBT, InP-based modulator, SOA, and GaAs VCSEL.

**Nguyen X. Nguyen** received the Ph.D. degree in electrical engineering from the University of California at Santa Barbara.

He is presently the Director of Advanced Technology Development at Global Communication Semiconductors, Inc. He is responsible for the development of the baseline high-performance InP HBT process at GCS. Previously, he was a Senior Development Engineer at Skyworks Solutions (formerly Conexant Systems), where he was a key member of the InGaP/GaAs HBT process technology.

nology group. Prior to that, he was with the research staff at HRL Laboratories, where he successfully established baseline GaN HFETs for high-performance electronics applications. His pioneering works in robust GaN HFET low noise amplifiers has enabled novel circuits and systems. He has extensive experience in device engineering and development for commercial high-volume and high-performance applications. He holds two patents with two pending, and has published over 25 research papers.

Chahn Nguyen, photograph and biography not available at the time of publication.