This work was supported under the DARPA-TFAST program

## Why are fast transistors required?

## Fiber Optic Communication Systems

40 Gb/s commercially available 80 and 160 Gb/s(?) long haul links

### High speed Instrumention

mixed-signal ICs with large dynamic range

### mm-Wave Wireless Transmission

*high frequency communication links, atmospheric sensing, military and commercial radar*

# InP vs Si/SiGe HBTs

InP system has inherent material advantages over Si/SiGe

20x lower base sheet resistance,5x higher electron velocity,4x higher breakdown-at same f<sub>t</sub>.

but...

today's SiGe HBTs are fast catching up due to 5x smaller scaling and offer much higher levels of integration due to the Si platform

Scaling Laws for HBTs

Reduce vertical dimensions to decrease transit times

Reduce lateral dimensions to decrease RC time constants

Increase current density to decrease charging time

# InP HBTs today... and tomorrow?

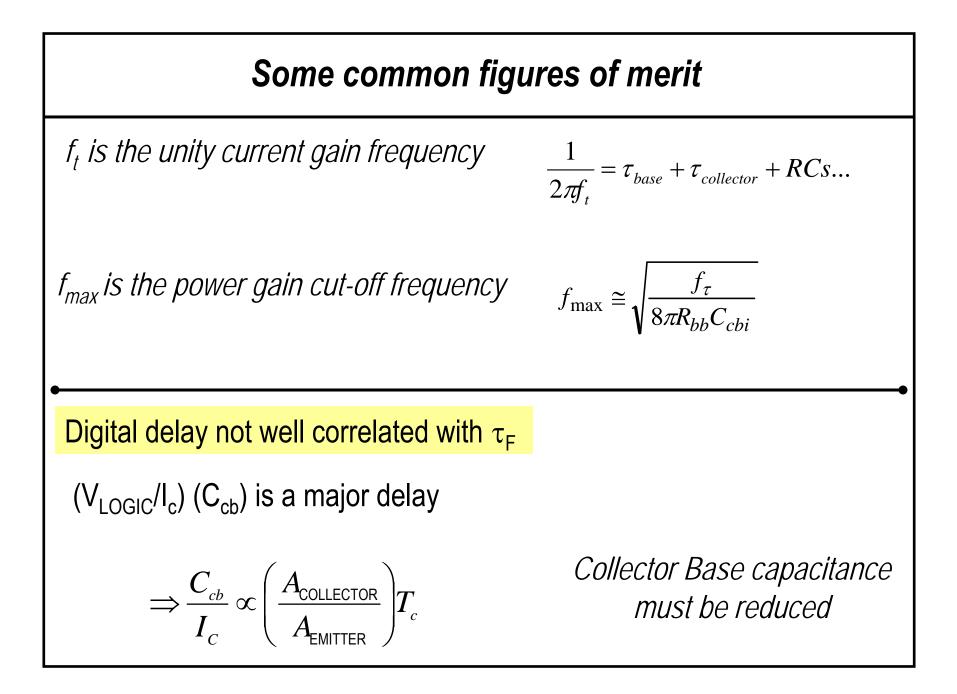

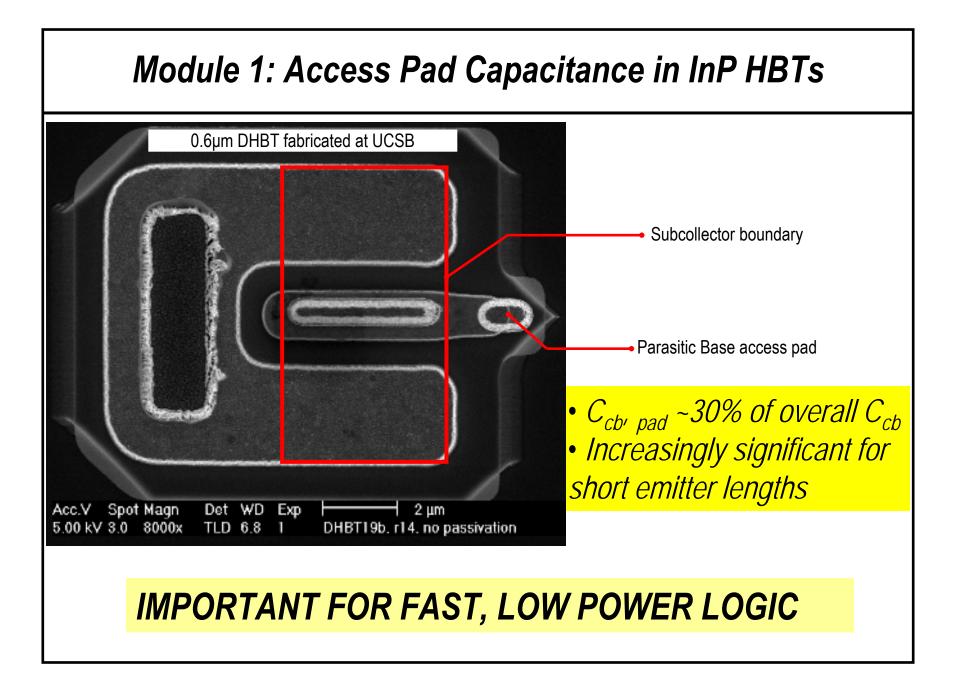

- Parasitic base collector capacitance

under base contacts

- Base ohmic transfer length limits collector scaling

- Non-planar device

# Key Challenges for InP HBTs

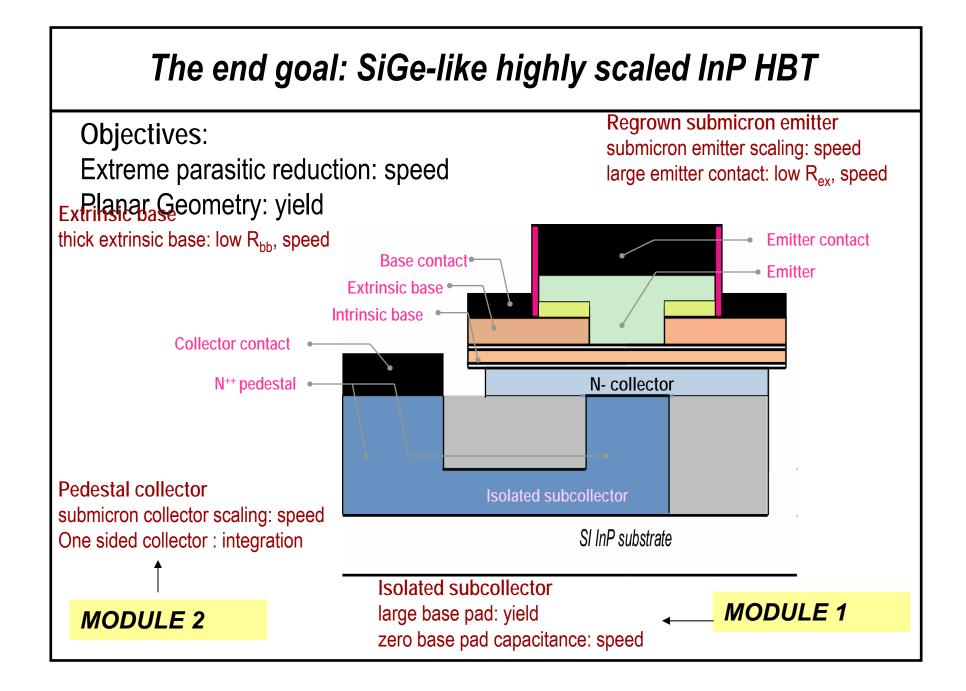

- Scaling of collector-base junction

- Planar, manufacturable process for high levels of integration

- Narrow base-emitter junction formation and also low R<sub>ex</sub>

A Radical approach is necessary

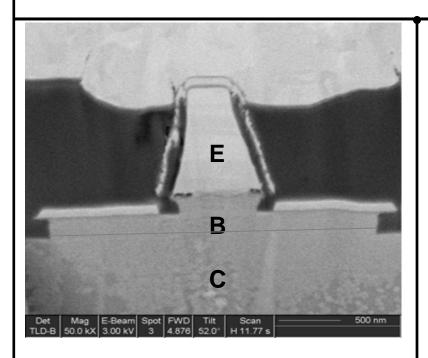

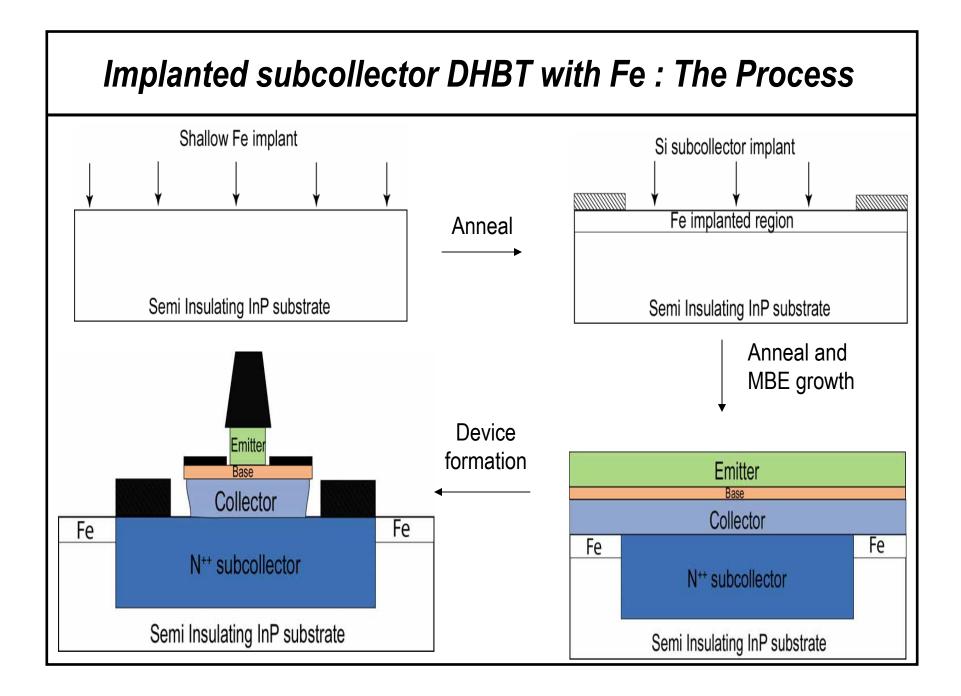

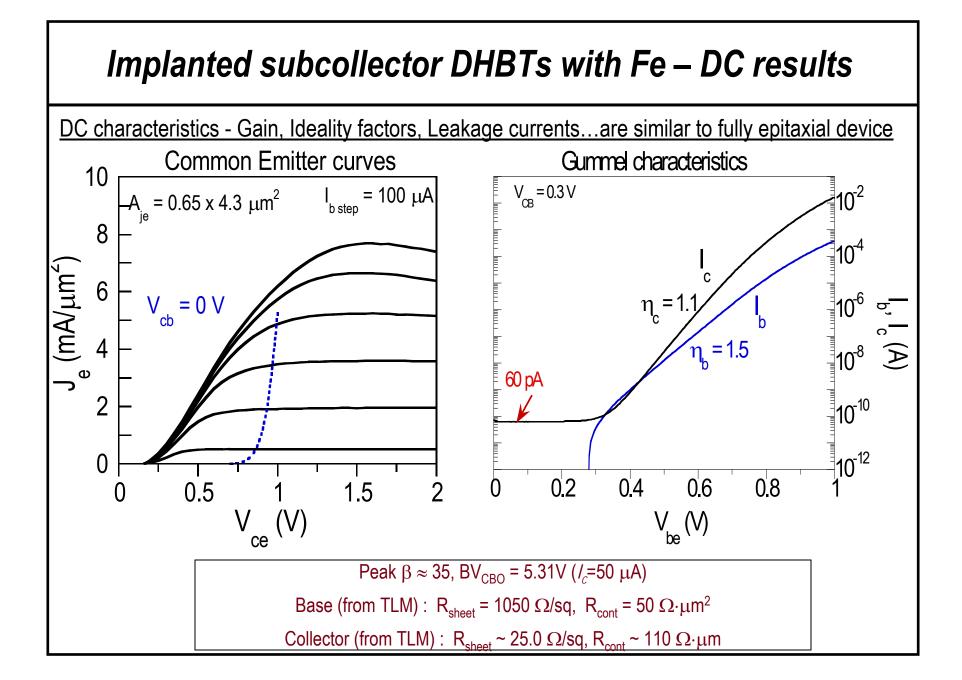

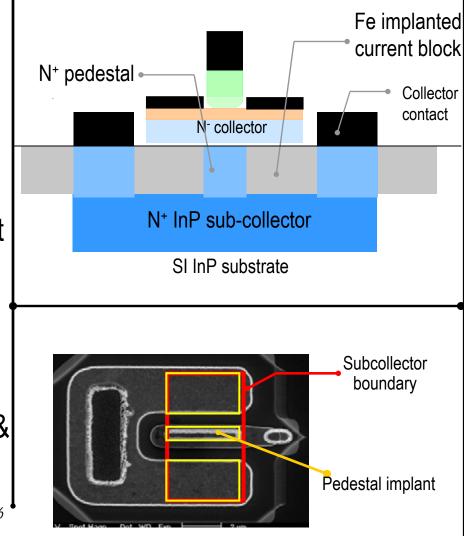

#### Implanted subcollector InP DHBTs Emitter • Approach contact Selectively implanted N<sup>++</sup> subcollector Collector contact • Growth of drift collector, base & emitter Device formation Implanted N<sup>++</sup> InP subcollector SI substrate Side View Interface charge compensation Emitter contact Collector post N<sup>++</sup> charge present on exposed InP Base post surface Collector contact • Fe implant suppresses interface charge Implanted sub-collector SI InP SI InP SI InP

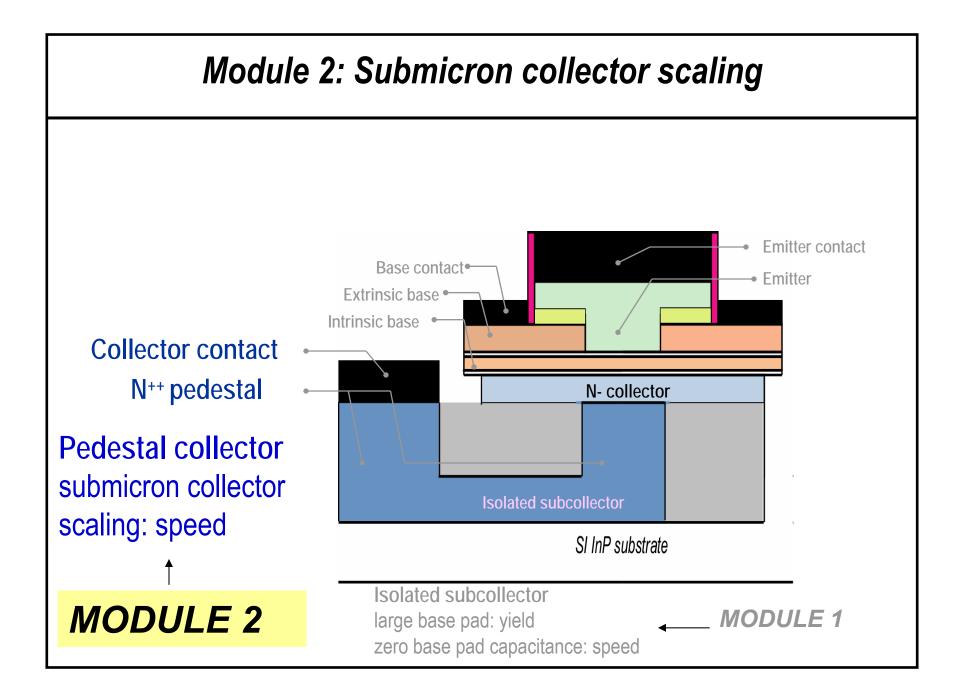

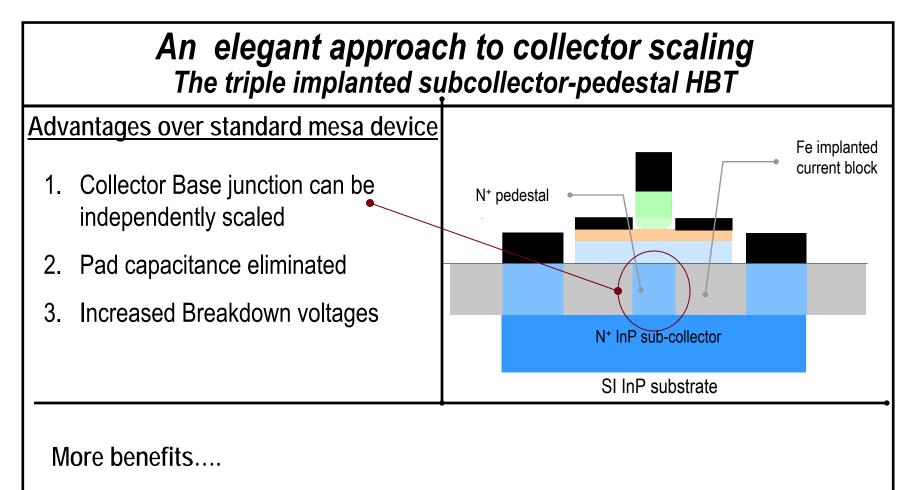

# An elegant approach to collector scaling The triple implanted subcollector-pedestal HBT

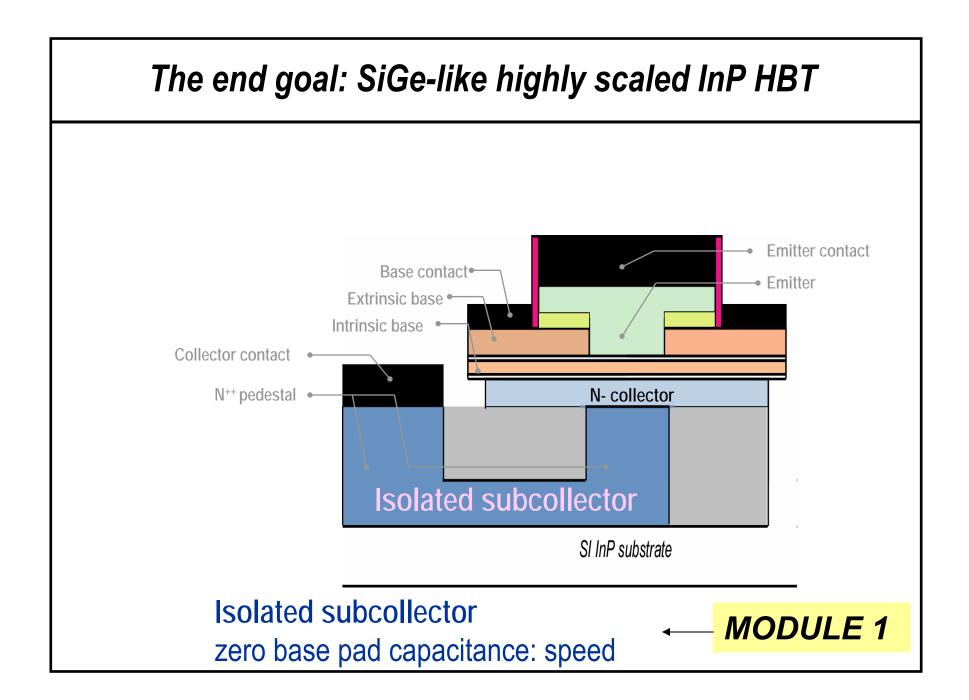

# Approach

deep N<sup>++</sup> InP subcollector by selective Si implant

$\rightarrow$  isolate base pad (Module 1)

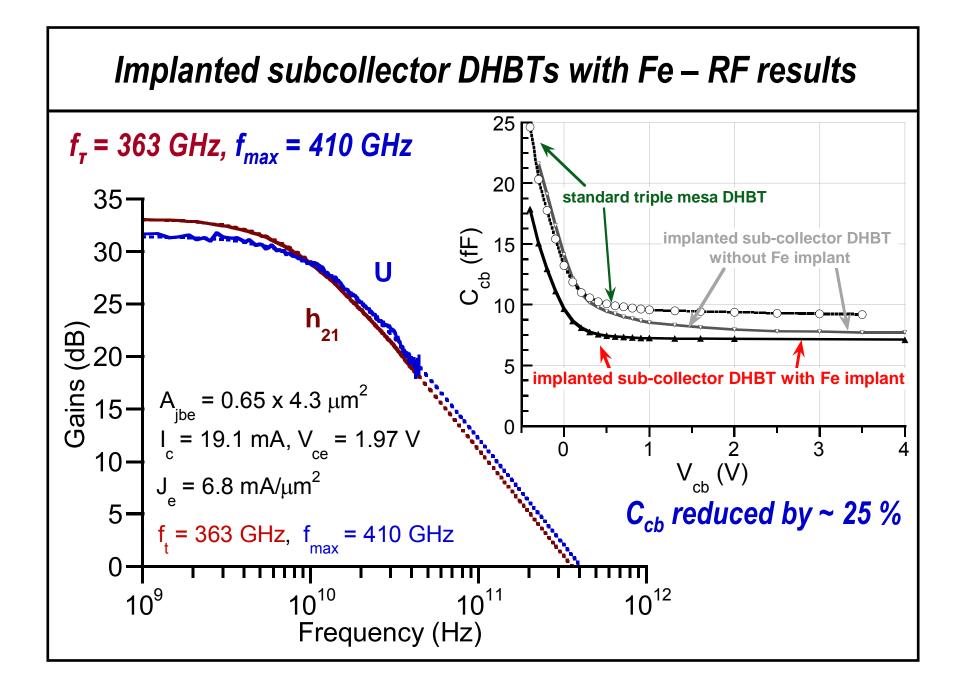

2. SI layer ~0.2 $\mu$ m, by Fe implant

$\rightarrow$  decrease extrinsic C<sub>cb</sub>

- 3. Second Si implant creates N<sup>++</sup> pedestal for current flow

- 4. Growth of drift collector, base & emitter and device formation

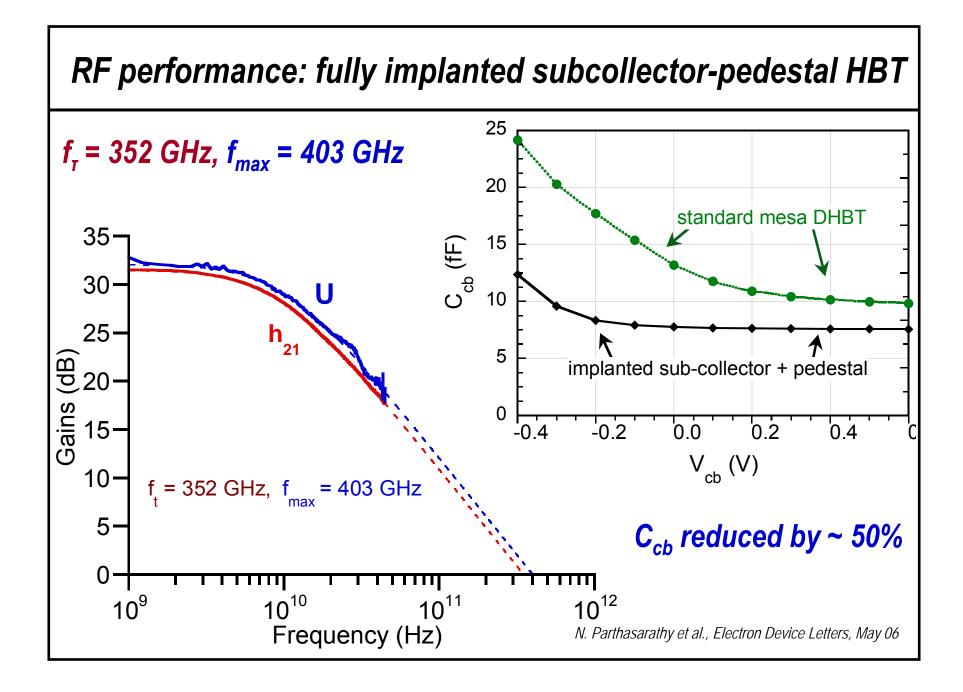

N. Parthasarathy et al., Electron Device Letters, Vol. 27(5), May 06

- 4. Highly planar, fully implanted process, no regrowth required  $\rightarrow$  manufacturability

- 5. Implants before growth endless variations in subcollector-pedestal layers without compromising device planarity

- 6. Fe compensates interface charge  $\rightarrow$  reliability and repeatability

# Conclusion

### Implanted collector InP HBTs at 500 nm scaling generation ~ 400 GHz ft & fmax

- Implanted subcollector DHBTs eliminate pad capacitance

- Implanted pedestal-subcollector DHBTs independent collector scaling

### InP HBT future: 125 nm scaling generation with implanted pedestalsubcollectors

~1 THz  $f_t \& f_{max}$ , 400 GHz digital latches & 600 GHz amplifiers?

## Applications

160+ Gb/s fiber ICs, 300 GHz MMICs for communications, radar, & imaging & applications unforeseen & unanticipated

"The principal applications of any sufficiently new and innovative technology always have been – and will continue to be – applications created by that technology." -Kroemer's Lemma of New Technology