30th Anniversary Reader Bonus

# Ask The Applications Engineer

# ANALOG DEVICES TECHNICAL REFERENCE BOOKS

# **Published by Analog Devices**

**Nonlinear Circuits Handbook**

**Transducer Interfacing Handbook**

**Mixed-Signal Design Seminar Notes**

**Amplifier Applications Guide**

**System Applications Guide**

**Linear Design Seminar Notes**

**Practical Analog Design Techniques**

**High-Speed Design Seminar Notes**

**ADSP-21000 Family Applications Handbook**

Published by Prentice Hall (available from Analog Devices)

**Analog-Digital Conversion Handbook**

**Digital Signal Processing in VLSI**

DSP Applications Using the ADSP-2100 Family (Vols. 1 & 2)

# **Ask The Applications Engineer**

© Analog Devices, Inc., 1997

All rights reserved

# WORLDWIDE HEADQUARTERS

One Technology Way P.O. Box 9106, Norwood, MA 02062-9106, U.S.A Tel: (617) 329-4700, Fax: (617) 326-8703

Printed in the United States of America

Information furnished by Analog Devices, Inc., is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices, Inc., for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Use in life support applications: Products sold by Analog Devices are not designed for use in life support equipment where malfunction of such products can reasonably be expected to result in personal injury or death. Buyer uses or sells such products for life support application at buyer's own risk and agrees to defend, indemnify, and hold harmless Analog Devices from any and all damages, claims, suits, or expense resulting from such use.

All brand or product names mentioned are trademarks or registered trademarks of their respective holders. Specifications are subject to change without notice.

# **TABLE OF CONTENTS**

|     |                                                                                           | Page |

|-----|-------------------------------------------------------------------------------------------|------|

|     | Preface                                                                                   | iv   |

| 1.  | Multi troubles, Trouble from the start, About log compensation resistors James Bryant     | 1    |

| 2.  | When it comes to trimming                                                                 | t 2  |

| 3.  | V/F converters                                                                            | t 4  |

| 5.  | Used correctly, high-speed comparators provide many useful circuit functions John Sylvan  | 6    |

| 6.  | Op-amp issues                                                                             | t 8  |

| 7.  | Op-amp issues—Noise                                                                       | t 10 |

| 8.  | Op-amp issues—Noise (continued), How grainy is current flow? James Bryant                 | 12   |

| 9.  | Seminars and Support                                                                      | 14   |

|     | Supply decoupling, non-idealities of resistors                                            | 14   |

| 10. | PC-board tracks and ground planes                                                         | t 16 |

| 11. | Voltage references                                                                        | 18   |

| 12. | Grounding (again)                                                                         | 20   |

|     | Time references, More on Trimming                                                         | 22   |

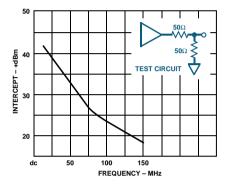

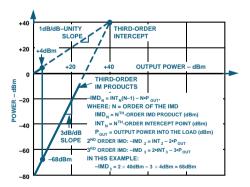

| 13. | Confused about amplifier distortion specs?                                                | 23   |

| 14. | High-frequency signal contamination James Bryant, with Herman Gelbach                     | 26   |

|     | A Reader Notes (re-High-frequency signal contamination) Leroy Cordill                     | 1 28 |

| 15. | Using sigma-delta converters, part I Oli Josefsson                                        | ı 29 |

| 16. | Using sigma-delta converters, part II, and questions on noise in converters Oli Josefssor | n 33 |

| 17. | Must a "16-bit" converter be 16-bit monotonic and settle to 16 ppm?                       | 39   |

| 18. | Settling time                                                                             | 40   |

| 19. | Interfacing to serial converters, part I                                                  | 42   |

| 20. | Interfacing to serial converters, part II Eamon Nash                                      | 44   |

| 21. | Capacitance and capacitors                                                                | 46   |

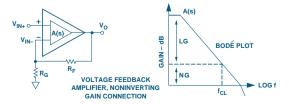

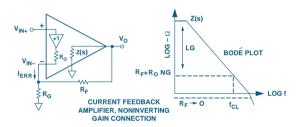

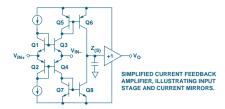

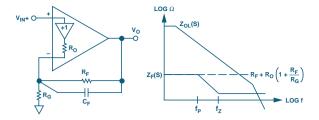

| 22. | Current-feedback amplifiers, part I                                                       | 50   |

| 23. | Current-feedback amplifiers, part II Erik Barnes                                          | 52   |

|     | Index                                                                                     | v    |

### PREFACE AND INTRODUCTION

This special issue of *Analog Dialogue* is offered as a bonus to our faithful readers and an encouragement to new readers. We have reprinted here the popular series, entitled "Ask The Applications Engineer", from its inception in 1988 through Number 23\* in 1996.

We are celebrating *Analog Dialogue*'s 30th sequential year in print, just concluded. During those years, *Analog Dialogue* has informed, enlightened, and occasionally educated more than a generation of engineers, scientists, and technicians about Analog Devices's products, practice, and ideas for high-performance signal processing by analog, digital, and mixed means.

This 30th anniversary Selection, Ask The Applications Engineer, joins the collection of articles in our 25th anniversary bonus edition, The Best of Analog Dialogue—1967 to 1991. Readers of that 224-page collection (still available upon request) will recall its many articles relating to practice—as well as articles about landmark products. Our intent in originating the "Ask The Applications Engineer" series has been to supplement that mine of information with a source of what has come to be called FAQ—frequently asked questions (and answers). They are chronicled by a few of our Applications Engineers, but are based on the accumulated wisdom and experience of our worldwide Applications Engineering staff, interacting with tens of thousands of customers worldwide.

Throughout the pages of this volume you will find references to Analog Devices products and publications, just as they appeared in the original edition. If you are interested in receiving copies of publications available from Analog Devices or information about specific products, you may consult our Web site, http://www.analog.com, or phone our Help line, 1-800-ANALOGD (1-800-262-5643) in North America, (617) 937-1428 elsewhere, or one of our local offices. Data sheets are available in North America by 24-hour automated fax by phoning the AnalogFax<sup>TM</sup> number, 1-800-446-6212. Requests for publications may also be faxed to (617) 326-8703. Naturally, any timely material is on its way to obsolescence the day it appears in print, so it's possible that at the time you read about a particular device, updated or improved versions have become available. For updated information, phone our Help line or one of our local offices.

The articles in this publication appear in chronological order, starting with "Ask The Applications Engineer—1". But in order for the book to be useful as a reference source, we have provided an Index at the back; it will permit the reader to find material relating to a particular interest wherever it appears. We hope you will find this publication helpful and will welcome your suggestions of questions to be answered in the future.

Dan. Sheingold@analog.com

Editor, Analog Dialogue

<sup>\*</sup>With one exception: We have not included "Ask The Applications Engineer—4", which was devoted to a description of a 5.25" Component Selection Guide diskette that was novel and useful in its time; however, it has long been obsolete—in this day of the Web site, the CD-ROM, and the selection tree in print. Just about everything else has turned out to include information of timeless value.

by James Bryant

### **MULTI TROUBLES**

- Q. My multiplexed ADC system is misbehaving . . .

- A. Before you go any further, have you grounded all unused multiplexer channels?

- Q. No. But how did you know?

- A. Because the floating terminal is one of the commonest causes of problems in systems containing CMOS multiplexers. Unused MUX inputs and outputs (whether integrated into a multiplexed ADC or part of a self-contained MUX chip) can pick up signals from stray fields and inject them into the device's substrate, turning on spurious substrate devices. Then, even when the unused channel is turned off, the performance of the *on-channel may be* badly degraded (at *the* unlikely extreme, *the* injection may turn on a spurious four-layer device and destroy some chips).

Whenever a MUX is used, all its inputs and outputs must be connected to a potential between its supply rails. The best way to deal with unused channels is to ground them, but they may be connected to a more-convenient potential within the rails.

### TROUBLE FROM THE START

- Q. To save power, my ADC is powered up only to make a measurement. The system is very accurate in continuous operation, but unpredictable when power is strobed. Why?

- A. When an ADC's power is switched on only to perform a conversion, it may misbehave for three reasons: slow reference turn-on, random initial logic states, and system latch-up.

For various reasons—thermal stabilization, capacitance charging, slow starting of regenerative current mirrors using PNP transistors in band-gap references— it is not uncommon for some voltage references to have relatively large errors for many milliseconds after power-up. Such errors in an ADC's external or internal reference during conversion lead to inaccurate results.

At turn-on, a typical ADC's logic will be in a random state; for a conversion triggered at that time, the ADC may not be able to perform correctly. With one conversion triggered, the logic should return to its correct pre-conversion state—but cases exist where two conversion cycles are necessary before the ADC is certain to perform a valid conversion. Hence, a good general rule is to perform two "dummy" conversions after powerup before relying on the results. (It is also well to recall that some ADCs react badly to having a conversion triggered before the previous conversion is complete; when this happens, one or two "dummy" conversions may be needed to return the logic to a known state.)

If an ADC's external logic is arranged so that the end of the ADC "Busy" signal starts a delay which ends with the start of the next conversion, it is important to realize that if the converter powers up in the Busy state, the Busy signal may remain latched up until a conversion Start pulse has been received. In this case, such a system cannot self-start. If the

Busy signal is always present on power-up the problem is almost certain to be recognized—and addressed—during the design of the system; but if the Busy signal is only occasionally present on power-up the system may latch unpredictably. As a rule, control signals to an ADC during start-up should not depend on the logical state of Busy.

# **ABOUT LOG COMPENSATION RESISTORS**

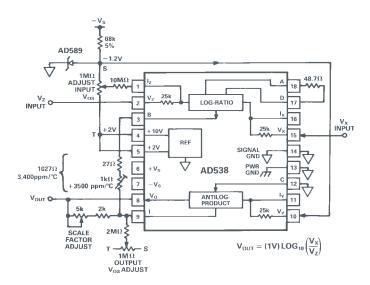

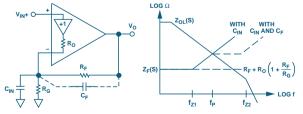

- Q. Designs of logarithmic circuits\*, including those using the AD538 Y[Z/X]<sup>m</sup> unit: (for example, Figure 6 from the AD538 Multifunction Unit data sheet†) call for "kT/q compensation resistors". What are they and where do I get them?

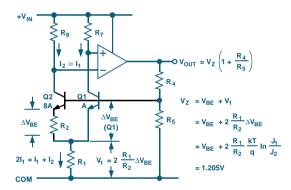

- A. The  $V_{BE}$  difference across two opposed silicon junctions, one carrying a current, I, and the other a current,  $I_{REF}$ , is  $(kT/q) \ln (I/I_{REF})$ . Here, k/q is the ratio of Boltzmann's constant to the charge on an electron (about 1/11,605 K/V), and T is the absolute temperature in kelvins.

Although employing similar junctions in isothermal pairs eliminates the effects of temperature-sensitivity of reverse saturation current, the kT/q term is still temperature-dependent. To eliminate this dependency in the application, the logarithmic voltage must be used in a circuit whose gain is inversely proportional to the absolute temperature of the junctions. Over a reasonable range of temperatures near  $20^{\circ}\text{C}$ , this may be arranged by the use of a gain-setting  $1\text{-k}\Omega$  resistor having a positive temperature coefficient of approximately  $3,400\text{ppm}/^{\circ}\text{C}$ —and keeping it at the same temperature as the junctions.

A 3,500 ppm/°C resistor is available from Tel Laboratories, 154G Harvey Road, Londonderry, New Hampshire 03053 (603)-625-8994, Telex: (710)-220-1844, designated Q-81, and from the Precision Resistor Co. Inc., 10601, 75th. St., Largo, Florida 33543 [(813)-541-5771 Telex: 821788], as the PT146. Analog Devices offices in most European countries are aware of local suppliers of these resistors.

\*Much useful information about logarithmic and other analog function circuits can be found in the Nonlinear Circuits Handbook, published by Analog Devices (\$5.95), P.O. Box 9902, Norwood MA 02062. †See The Best of *Analog Dialogue* 1967–1991, pp. 164-167.

by James Bryant

### WHEN IT COMES TO TRIMMING . . .

- Q. I need some advice about trimming offsets and gains.

- A. Don't!—unless you must. Good alternatives include (a) using headache-free devices, components, and circuits that meet the specs without trimming; (b) taking advantage of digital technology in system applications to make trim corrections in software. Savings provided on occasion by trim potentiometers, in conjunction with loosely spec'd devices, can turn out to be illusory when you consider the effects of circuit design, temperature, vibration, and life on performance and stability—as well as additional paperwork and complexity trimming entails.

- Q. Nevertheless, how do I trim the offset and gain errors in analog circuitry?

- A. In the correct order and with the correct inputs. If you consider the transfer characteristic of the circuit being trimmed the method to use is generally straightforward.

The simplified ideal transfer characteristic of a linear analog circuit (such as an amplifier, ADC or DAC) is given by the equation:

$$OP = K \times IP$$

(1)

where OP is output, IP is input, and K is a scale factor (Note that this simplification hides an enormous number of issues: quantization error in an ADC; dimensionality of K if the input and output are in different forms [e.g. voltage in / current out]; intentional offsets; and many others.)

In a real (non-ideal) circuit, offset and gain errors, OS (referred to the input) and  $\Delta K$ , respectively, also appear in the equation, which becomes:

$$OP = (K + \Delta K) \times (IP + OS)$$

(2)

$$OP = (K \times IP) + [(K \times OS) + (\Delta K \times IP) + (\Delta K \times OS)]$$

(3)

Equations (2) and (3) are incomplete in that they assume only one offset—at the input—but this is the most-common case. Systems with separate input and output offsets will be considered later.

From (3) we see that it not possible to trim gain directly when an unknown offset is present. Offset must be trimmed first. With *IP* set at 0, the offset trim is adjusted until *OP* is also 0. Gain may then be trimmed: with an input near to full scale (FS), the gain trim is adjusted to make the output obey equation (1).

- Q. But what about bipolar ADCs and DACs?

- A. Many ADCs and DACs may be switched between unipolar and bipolar operation; such devices, wherever possible, should have their offset and gain trimmed in the unipolar mode. Where it is not possible, or where the converter is to operate only in the bipolar mode, other considerations apply.

A bipolar converter may be considered as a unipolar converter with a large offset (to be precise, an offset of 1 MSB—one-half

of full-scale range). Depending on the architecture used, this bipolar offset (*BOS*) may or may not be affected by the gain trim. If it is so affected, equation (1) becomes:

$$OP = K \times (IP - BOS)$$

(4)

In this case offset is trimmed at analog zero, after which gain is trimmed near FS—positive or negative, but usually positive. This is normally the method used for DACs where the bipolar offset is within the DAC.

If the bipolar offset is not affected by the gain trim:

$$OP = K \times IP - BOS \tag{5}$$

Here offset is trimmed at FS negative and gain is trimmed at (or very near to—see below) FS positive. This method is used for most ADCs and for DACs where bipolar offset is obtained by the use of op amps and resistors external to the DAC.

Naturally, the method suggested on the data sheet should always be followed, but where a data sheet is unobtainable, in general, offset should be trimmed at analog zero for DACs and FS negative for ADCs—and near FS positive for both.

- Q. Why do you keep saying "near" to full scale?

- A. Amplifiers and DACs may be trimmed at zero and full scale. In the case of a DAC, all-1's—the largest digital input possible—should produce an output 1 LSB below "full scale," where "full scale" is considered as some constant times the reference; this follows since the output of a DAC is the normalized product of the reference and the digital input.

ADCs are not trimmed at zero and FS. The output of an ideal ADC is quantized, and the first output transition (from  $00\dots00$  to  $00\dots01$ ) takes place 1/2 LSB above the nominal value of all 0's. Thereafter transitions take place every 1-LSB increase in analog input until the final transition takes place 1 1/2 LSB below FS. A non-ideal ADC is trimmed by setting its input to the nominal value of a desired transition and then adjusting until the ADC output flickers between the two values equally.

The offset of an ADC is therefore trimmed with an input corresponding to the first transition (i.e., 1/2 LSB above zero or above FS negative—which is "near" zero or "near" FS negative); and the gain is then trimmed at the last transition (i.e. 1 1/2 LSB below FS positive—which is "near" FS positive). This procedure results in an interaction between the gain and offset errors during offset trim but it should be too slight to be significant.

- Q. Are there any other anomalies resulting in a need to trim "near", rather than at full scale?

- A. Synchronous voltage-to-frequency converters (SVFCs) are liable to injection locking phenomena when their output frequency is harmonically related to their clock frequency, i.e., when their output is very close to 1/2, 1/3 or 1/4 of clock frequency. FS for an SVFC is 1/2 clock frequency. The presence of a trim tool can exacerbate the problem. It is therefore advisable to trim the gain of an SVFC at around 95% of FS.

- Q. What about circuits requiring both "input" and "output" offset trim?

- A. Circuits such as instrumentation and isolation amplifiers often have two stages of dc gain, and the gain of the input stages can be variable. Thus a two stage amplifier, with an input offset, *IOS*, an output offset, *OOS*, a first stage gain of *K*, and a unity-gain output stage, has (for zero input) an output, *OP*, of:

$$OP = OOS + K \times IOS$$

(6)

From (6) it is evident that if the gain is constant we need only adjust either *IOS* or *OOS* to null the total offset (although if the input uses a long-tailed pair of bipolar transistors we will get a better offset temperature coefficient if we trim both—for FET long-tailed pairs this is not necessarily the case). If the first stage gain is to be varied, both offsets must be trimmed.

This is done by an iterative procedure. With zero input, and gain set to maximum, the input offset is adjusted until the output is also zero. The gain is then reduced to its minimum value and the output offset adjusted until the output is zero again. The two steps are repeated until no further adjustment is necessary. Gain trimming should not be done until both *IOS* and *OOS* are pulled; the actual values of the high and low gains used in offset trim are unimportant.

- Q. What circuitry should I use for gain and offset trims?

- A. Many amplifiers (and a few converters) have terminals for trimming gain and offset. Many more do not.

Offset trim is normally performed with a potentiometer connected between two assigned terminals, and its wiper is connected (sometimes via a resistor) to one of the supplies. The correct connections and component values will be given on the device data sheet. One of the commonest differences between op-amps is the value of offset correction potentiometer and which supply it should be connected to.

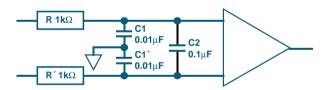

Where separate terminals are not provided for offset trim, an offset-adjusting constant can usually be added to the input signal. Two basic possibilities are shown in Figures 1a and 1b. Where the correction is being made to a system where a differential input op amp is used as an inverter (the commonest case) the method of la is best to correct for device offsets—but not system offsets. In the single-ended connection, method 1b will work for system offsets but should be avoided where possible for small device offsets, because it often requires a

a. Voltage applied to non-inverting input.

b. Current summed at inverting input.

Figure 1. Two connections for offset adjustment.

very large value of summing resistance, compared to the signal-input resistances, in order to (i) avoid loading the summing point excessively, (ii) scale the correction voltage properly and produce enough attenuation to minimize the effects of differential supply-voltage drifts. It is often helpful to use resistances between the supplies and the potentiometer to increase trim resolution and reduce dissipation.

Where gain trim is provided for in a circuit, it will generally consist of a variable resistor. Details of its value and connection will appear on the data sheet of the device. Where gain trim is not required, this resistor may be replaced by a fixed resistor having half the resistance of the maximum value of the recommended trim potentiometer.

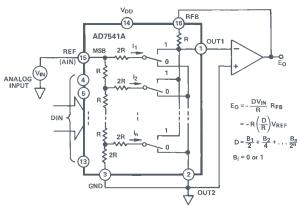

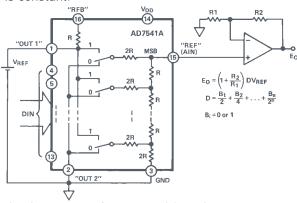

Where gain trim is not provided it is not always achievable externally without an additional variable-gain stage. For example, consider a DAC using a ladder network. If the ladder network is used in the current mode (Figure 2a), the input impedance at the reference terminal does not vary with digital code, and the gain of the DAC may be trimmed with a small variable resistor in series with either the reference input or the feedback resistor. However, if the DAC is used in the voltage mode (Fig 2b), then the reference input impedance is code dependent, and gain may only be trimmed by varying the reference voltage—which is not always possible—or the gain of the buffer amplifier.

The possibility of trimming gain in circuits not furnished with gain-trim circuitry, therefore, will depend on individual cases; each must be assessed on its own merits.

a. CMOS DAC connected for current steering. Input impedance is constant.

b. The same DAC connected for voltage output. Figure 2. Comparing basic DAC circuits.

by James Bryant

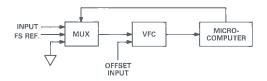

### V/F CONVERTERS

- Q. How do I send an analog signal a long distance without losing accuracy?

- A. An excellent solution to this common problem is to ship the signal as frequency using a *voltage-to-frequency converter* (VFC), a circuit whose output is a frequency proportional to its input. It is relatively easy to send a frequency signal over a long transmission path without interference via optical isolators, optical fibre links, twisted-pair or co-axial lines, or radio links.

If the data must be digital, the receiver will consist of a frequency counter, easily implemented in a single-chip microcomputer. Frequency is reconverted to analog voltage by a "frequency-to-voltage converter" (FVC)—generally a VFC configured to perform its inverse function, often using a phase-locked loop.

- Q. How does a VFC work?

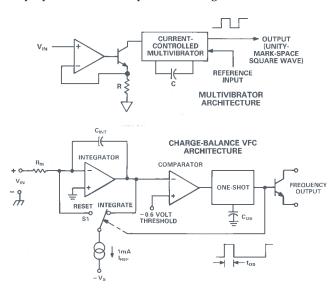

- A. There are two common types: multivibrator-(AD537) and charge-balance (AD650) VFCs.\*  $^{*}$

In the *multivibrator* type, the input voltage is converted to a current which charges and discharges a capacitor. The switching thresholds are set by a stable reference, and the output, which has unity mark-space ratio, is a frequency proportional to the input.

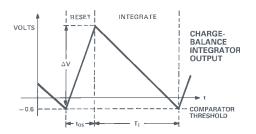

The *charge-balance* VFC uses an integrator, a comparator and a precision charge source. The input is applied to the integrator, which charges. When the integrator output reaches the comparator threshold, the charge source is triggered and a fixed charge is removed from the integrator. The rate at which charge is removed must balance the rate at which it is being supplied, so the frequency at which the charge source is triggered will be proportional to the input to the integrator.

- Q. What are the advantages and disadvantages of the two types?

- A. The multivibrator is simple and cheap, demands little power, and has unity mark-space (M-S) output—very convenient with some transmission media. But it is less accurate than the charge-balance type and cannot integrate negative input transients.

The charge-balance type is more accurate, and negative input transients are integrated to contribute to the output. It has more-demanding supply requirements and a lower input impedance, and its output is a pulse train, not a unity M-S square wave.

- Q. What are the important types of error in a VFC?

- A. The same three as in most precision circuitry: offset errors, gain errors and linearity errors—and their variation with temperature. As with most precision circuitry, offset and gain can be trimmed by the user, but linearity cannot. However, the linearity of VFCs is normally very good (if the capacitors are properly chosen—see below).

- Q. How do you trim gain and offset in a VFC?

- A. The procedure suggested by theory is to trim offset first at zero frequency and then gain at full scale (FS). But this can give rise to problems in recognizing "zero frequency," which is the state when the VFC is just not oscillating. It is therefore better to trim offset with a small input (say 0-1% FS) and adjust for a nominal frequency, then trim gain at FS, and then repeat the procedure once or twice.

For example, suppose a VFC is being used with FS of 100 kHz at 10-volt input. Ideally,  $10\,\mathrm{V}$  should give 100-kHz output and 10-mV input should give 100 Hz. Offset is, therefore, trimmed for 100 Hz with 10 mV applied; gain is then trimmed to give 100 kHz at 10 V. But gain error affects the 10-mV offset trim slightly, so the procedure may have to be repeated to reduce the residual error.

If a VFC is used with software calibration a deliberate offset is often introduced so that the VFC has a definite frequency for zero input voltage. The microcomputer measures the VFC outputs at 0 V and FS inputs and computes the offset and scale factor. It may also be necessary to reduce the gain so that the VFC cannot try to exceed its maximum rated frequency.

\*Data sheets are available for any of the Analog Devices products mentioned here. An Application Note: "Operation and Applications of the AD654 V-to-F Converter," is also available without charge.

- Q. What circuit precautions are necessary when using a VFC?

- A. Apart from the usual precautions necessary with any precision analog circuitry (grounding, decoupling, current routing, isolation of noise, etc., a subject for a book, not a paragraph) the main precautions necessary when using a VFC are the choice of capacitor and separation of the input and output.

The critical capacitors in a precision VFC (the multivibrator's timing capacitor, and the monostable timing capacitor in a charge-balance type) must be stable with temperature variation. Furthermore, if they suffer from *dielectric absorption*, the VFC will be nonlinear and may have poor settling time.

If a capacitor is charged, discharged and then open-circuited it may recover some charge. This effect, known as dielectric absorption (DA), can reduce the precision of VFCs or sample-hold amplifiers using such capacitors. VFCs and SHAs should therefore use Teflon or polypropylene, or zero- temperature-coefficient (NPO, COG) ceramic capacitors with low DA.

Coupling between output and input of a VFC can also affect its linearity. To prevent problems, decoupling practices and the usual layout precautions should be observed. This is critically important with opto couplers, which require high current drive (10-30 mA).

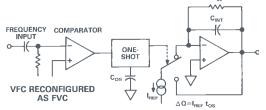

- Q. How do you make a frequency-to-voltage converter?

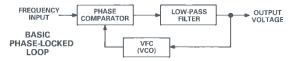

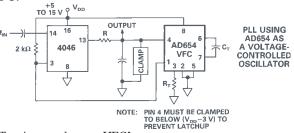

- A. There are two popular methods: the input frequency triggers the monostable of a charge-balance VFC that has a resistor in parallel with its integration capacitor; or the input frequency can be applied to the phase/frequency comparator of a phase-locked loop (PLL), which uses a VFC (of either type) as its oscillator. The basic principle of the first type is illustrated below.

For each cycle of the input frequency, a charge,  $\Delta Q$ , is delivered to the leaky integrator formed by R and C. At equilibrium, an equal charge must leak away during each period, T (= 1/f), of the input, at an average rate, I = V/R. Thus,  $V = \Delta Q \cdot f \cdot R$ .

Though the mean voltage is independent of C, the output ripple is inversely dependent on C. The peak-to-peak ripple voltage,  $\Delta V$ , is given by the equation,  $\Delta V = \Delta Q/C$ . This indicates that ripple is independent of frequency (assuming that the charge, Q, is delivered in a short time relative to the period of the input). The settling time of this type of FVC is determined by the exponential time constant, RC, from which the time to settle within a particular error band may be calculated.

From these equations, we see that the characteristics of this type of FVC are interdependent, and it is not possible to optimize ripple and settling time separately. To do this we must use a PLL.

The phase-locked-loop FVC illustrated differs from any other PLL in only one respect: the voltage-controlled oscillator of the normal PLL, which must be monotonic but not necessarily linear, has been replaced by a VFC with a linear control law. In the servo system, negative feedback keeps the VFC's output frequency equal to the input frequency. The output voltage, the VFC's input, is accurately proportional to the input frequency.

Designing PLL systems is beyond the scope of this discussion, but if a 4000-series CMOS PLL, the 4046, is used *just as a phase detector* (its VCO's transfer characteristic is not sufficiently linear), we can build the FVC shown here, with an AD654 VFC.

- Q. What is a synchronous VFC?

- A. A charge-balance VFC with improved linearity and stability, where the monostable is replaced by a bistable, driven by an external clock. The fixed time during which the precision current discharges the integrator is one clock period of the external clock.

A further advantage of the SVFC is that the discharge does not start when the integrator passes the comparator threshold (at a non-critical rate), but on the next clock cycle. The SVFC output is synchronous with a clock, so it is easier to interface with counters,  $\mu$ Ps, etc.; it is especially useful in multichannel systems: it eliminates problems of interference from multiple asynchronous frequency sources.

There are two disadvantages. Since the output pulses are synchronized to a clock they are not equally spaced but have substantial jitter. This need not affect the user of a SVFC for a/d conversion, but it does prevent its use as a precision oscillator. Also, capacitive coupling of the clock into the comparator causes injection-lock effects when the SVFC is at 2/3 or 1/2 FS, causing a small (4-6 bit at 18-bit resolution at 1-MHz clock) dead zone in its response. Poor layout or device design can worsen this effect.

Despite these difficulties the improvement in performance produced by the abolition of the timing monostable makes the SVFC ideal for the majority of high-resolution VFC applications.

- Q. Can you have a synchronized FVC?

- A. Yes, and with very good performance; it is best done with an FVC- connected SVFC and a clock that is common to both ends of the transmission path. If the input signal to a synchronized FVC is *not* phase related to the clock, severe timing problems can arise, which can only be solved by the use of additional logic (two D flip-flops) to establish the correct phase relationship.

<sup>1</sup>See Gardner, F. M, *Phase-lock Techniques*, 2nd ed., New York: Wiley, 1979, for more detail; also Analog Devices' *Analog-Digital Conversion Handbook*.

High-speed comparators provide many useful circuit functions when used correctly.

by John Sylvan

Question: Why can't I just use a standard op amp in a high-gain or open-loop configuration as a voltage comparator?

You can—if you are willing to accept response times in the tens of microseconds. Indeed, if in addition you require low bias-currents, high-precision and low offset voltages, then an op amp might be a better choice than most standard voltage comparators. But since most op amps have internal phase/frequency compensation for stability with feedback, it's difficult to get them to respond in nanoseconds. On the other hand, a low-cost popular comparator, the LM311, has a response time of 200 ns.

Also the output of an operational amplifier is not readily matched to standard logic levels. Without external clamping or level-shifting, an op amp operating as a comparator will swing to within a few volts of the positive and negative supplies, which is incompatible with standard TTL or CMOS logic levels.

My comparator oscillates uncontrollably. Why does this happen?

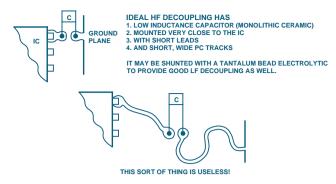

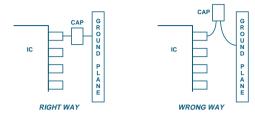

Examine the power-supply bypassing. Even a few inches of PC trace on the supply lines can add unacceptable dc resistance and inductance. As a result, transient currents while the output is switching may cause supply-voltage fluctuations, which are fed back to the input through the ground and supply lines. Install low-loss capacitors (0.1  $\mu F$  ceramic capacitors) as close as possible to the supply pins of the comparator to serve as a low-impedance reservoir of energy during high-speed switching.  $^1$

I've installed bypass capacitors, but I still can't keep my high-speed comparator from oscillating. Now what's the problem?

It could be the comparator's ground connection. Make sure that the ground lead is as short as possible and connected to a lowimpedance ground point to minimize coupling through lead inductance. Use a ground plane if possible and avoid sockets.

Another cause of the oscillation may be a high source impedance and stray capacitance to the input. Even a few thousand ohms of source impedance and picofarads of stray capacitance can cause unruly oscillations. Keep leads short, *including the ground clip of your scope probe*. For best measurement results use the shortest possible ground lead to minimize its inductance (< 1").

With a slowly moving input signal, my comparator seems to "chatter" as it passes through the transition voltage. Why can't I obtain a single clean transition from the device?

A comparator's high gain and wide bandwidth are typically the source of this problem. Any noise is amplified, and as the signal passes through the transition region, the noise can cause a fast-responding amplifier's output to bounce back and forth. Also, since the device's sensitivity (i.e., *gain*) is higher during a transition, the tendency to oscillate due to feedback increases. If possible, filter the signal to minimize noise accompanying it. Then try using hysteresis which, like backlash in gear trains, requires the input to change by a certain amount before a reversal occurs.

For example, after a high-to-low transition on the AD790, its built-in hysteresis requires the input voltage (positive input) to increase by  $500~\mu V$  to produce a low-to-high transition.

If my comparator does not have internal hysteresis, can I add it externally?

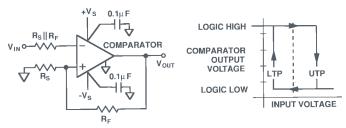

Yes, with external positive feedback. This is done by feeding a small fraction of the output of the comparator back to the positive input. This simple technique is shown in Figure 1. The hysteresis voltage from the lower transition point to the upper transition point will depend on the value of the feedback resistor,  $R_F$ , the source resistance,  $R_S$ , low output level,  $V_{low}$  and high output level,  $V_{high}$ . The low and high transition points are set by:

$$V_{low} \times \frac{R_S}{R_S + R_F}$$

and  $V_{high} \times \frac{R_S}{R_S + R_F}$

Figure 1. Applying external hysteresis to a comparator.

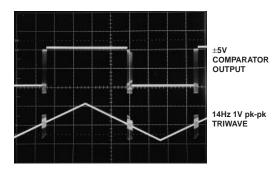

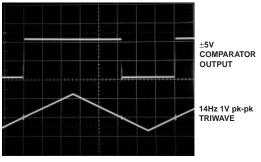

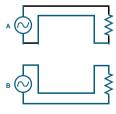

Figure 2 shows how adding external hysteresis can "clean up" a comparator's response. Figure 2a shows the response of a comparator with bipolar output swing without hysteresis. As the triangular-wave input (trace A) passes through the transition point (ground), the device oscillates vigorously (and couples a portion of the oscillation into ground and the signal-source). Figure 2b depicts the response of the same comparator with 5 mV of external hysteresis applied; it shows a much cleaner transition.

No external hysteresis

5 mV external hysteresis

Figure 2. Hysteresis helps clean up comparator response.

<sup>&</sup>lt;sup>1</sup>A useful discussion of comparator foibles can be found in *Troubleshooting Techniques Quash Spurious Oscillations*, by Bob Pease, *EDN*, September 14, 1989, pp. 152-6

A problem encountered with external hysteresis is that output voltage depends on supply voltage and loading. This means the hysteresis voltage can vary from application to application; though this affects resolution, it need not be a serious problem, since the hysteresis is usually a very small fraction of the range and can tolerate a safety margin of two or three (or more) times what one might calculate. Swapping in a few comparators can help confidence in the safety margin. Don't use wirewound resistors for feedback; their inductance can make matters worse.

What's the difference between propagation delay and prop-delay dispersion? Which of the two specifications is of most concern?

Propagation delay is the time from when the input signal crosses the transition point to when the output of the comparator actually switches. Propagation-delay dispersion is the variation in prop delay as a function of overdrive level. If you're using a comparator in pin-drive electronics in an automatic test system, then prop-delay dispersion will determine the maximum edge resolution. In contrast, propagation delay can be considered as a fixed time offset and therefore compensated for by other techniques.

I have a +5-volt system and don't want to add an additional supply voltage; can I use my comparator with a single supply?

Yes, but to establish the threshold use an adequately bypassed stable reference source well within the common-mode range of the device. The signal level is also to be referenced to this source.

I sometimes see unexpected behavior in my comparator. What could be the cause of this problem?

Examine the common-mode range of the input signal. Unlike operational amplifiers, that usually operate with the input voltages at the same level, comparators typically see a large differential voltage swings at their inputs. If the inputs exceed the device's specified common-mode range (even though within the specified signal range), the comparator may respond erroneously. For proper operation, ensure that both input signals do not exceed the common-mode range of the specific comparator. For example, the AD790 has a  $+V_S$  differential input range, but its common-mode range is from  $-V_S$  to 2 volts below  $+V_S$ .

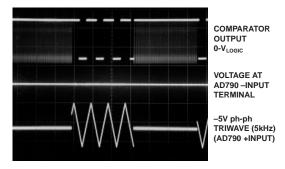

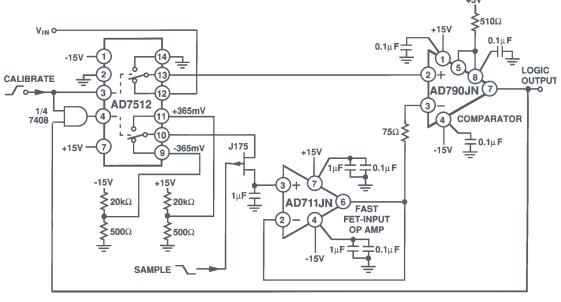

Can you suggest a circuit that performs autozeroing when the comparator is off-line to minimize drift?

Try the circuit shown in Figures 3 and 4. In the Calibrate mode, the input is disconnected and the positive input of the comparator is switched to ground. The comparator is connected in a loop with a pair of low-voltage sources of opposing polarity charging a buffered capacitor in response to the comparator's output state.

If the comparator's minus input terminal is above ground, then the comparator output will be low, the 1- $\mu F$  capacitor will be connected to the negative voltage (–365 mV) and the voltage from the buffer amplifier will ramp down until it is below the plus input (ground)—plus hysteresis and any offsets—at which point the comparator switches. If it is below ground, the comparator's output will be high, the capacitor will be connected to the positive voltage (+365 mV), the output from the buffer amplifier ramps up. In the final state, each time the comparator switches (when the ramped change exceeds the hysteresis voltage), the polarity of the current is reversed; thus the capacitor voltage averages out the offsets of the buffer and comparator.

At the end of the Calibrate cycle, the JFET switch is opened, with the capacitor charged to a voltage equal to the offsets of the comparator and buffer  $\pm$  the hysteresis voltage. At the same time, the Calibrate signal goes low, disabling the feedback to the polarity switch and connecting the input signal to the comparator.

Figure 4. Comparator output, buffer output, and comparator input.

Figure 3. Autozeroed comparator integrates out offsets during calibration cycle.

by James Bryant

### **OP-AMP ISSUES**

- Q. Why are there so many different types of operational amplifier?

- A. Because there are so many parameters that are important in different applications, and because it is impossible to optimize all of them at once. Op amps may be selected for speed, for noise (voltage, current or both), for input offset voltage and drift, for bias current and its drift, and for common-mode range. Other factors might include power: output, dissipation, or supply, ambient temperature ranges, and packaging. Different circuit architectures and manufacturing processes optimize different performance parameters.

- Q. Is there any common factor in the design of op-amps?

- A. Yes—most classical (voltage input) op-amps are three-stage devices, consisting of an input stage with differential input and differential output—with good common-mode rejection—followed by a differential-input, single-ended output stage having high voltage-gain and (generally) a single-pole frequency response; and, finally, an output stage, which usually has unity voltage gain.

- Q. So where are the differences?

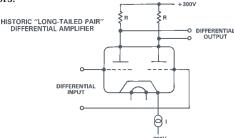

- A. There are many possible variations on this basic design. One of the most fundamental is the structure of the input stage. This stage is almost always a long-tailed pair—that is to say, a pair of amplifying devices connected as in the figure—but the choice of devices has a profound effect on the input parameters of the op amp. The figure was drawn with thermionic tubes to avoid any suggestion of partiality in favour of any particular semiconductor device. Since thermionic devices at present are not generally available in IC chip form, a monolithic op-amp will have an input stage built with bipolar or field-effect transistors.

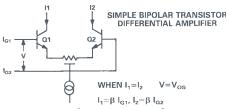

A long-tailed pair built with bipolar transistors is shown in the next figure. Its strong features are its low noise and, with suitable trimming, low voltage offset. Furthermore, if such a stage is trimmed for minimum offset voltage it will inherently have minimum offset drift. Its main disadvantage stems from the proportionality of the emitter and base currents of the transistors; if the emitter current is large enough for the stage to have a reasonable bandwidth, the base current—and hence the bias current—will be relatively large (50 to 1,000 nA in general-purpose op-amps, as much as 10  $\mu A$  in high-speed ones).

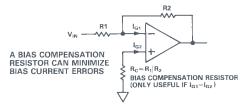

The bias currents in the inverting and non-inverting inputs are unipolar and well matched (their difference is called *offset current*), and they decrease in a minor way with increasing temperature. In many applications, the accurate matching may be used to compensate for their high absolute value. This figure shows a bias compensation circuit where the bias current in the non-inverting input flows in  $R_c$  (known as the bias compensation resistor); this compensates for the voltage drop as the bias current in the inverting input flows through R2.  $R_c$  is made nominally equal to the parallel combination of R1 and R2.—it can be trimmed to minimize error due to non-zero offset current).

Such bias compensation is only useful when the bias currents are well-matched. If they are not well-matched, a bias compensation resistor may actually *introduce* error.

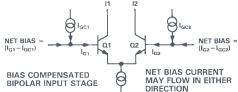

If a bipolar input stage is required without the drawback of such a high bias current, a different form of bias compensation may be used by the chip designer (next figure). The same long-tailed pair is used, but the major portion of the current required by each base is supplied by a current generator on the chip. This can reduce the external bias current to 10 nA or less without affecting the offset, temperature drift, bandwidth or voltage noise. Bias current variation with temperature is quite low.

There are two disadvantages to such an architecture: the current noise is increased and the external bias currents are not well matched (indeed, they may actually flow in opposite directions, or change polarity as chip temperature changes). For many applications these features are no drawback; indeed, one of the most popular low-offset op-amp architectures, the OP-07, uses just such an architecture, as do the OP-27, OP-37 and the AD707, which has a guaranteed offset voltage of only 15  $\mu V$ . Bias-compensated amplifiers of this type are often recognizable when their data sheets explicitly specify  $\it bipolar$  bias current, for example,  $\pm 4.0$  nA.

Where bias currents of even a few nanoamps are intolerable, bipolar transistors are usually replaced by field-effect devices. In the past, MOSFETs have been somewhat noisy for op-amp

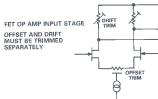

input stages, although modern processing techniques are overcoming this drawback. Since MOSFETS also tend to have relatively high offset voltages, *junction* FETs (JFETs) are used for high-performance low-bias-current op amps. A typical JFET op-amp input stage is shown in this figure.

The bias current of a JFET bears no relationship to the current flowing in the device, so even a wideband JFET amplifier may have a very low bias current—values of a few tens of picoamperes are commonplace, and the AD549 has a guaranteed bias current of less than 60 fA (one electron per three microseconds!) at room temperature.

The qualification "at room temperature" is critical—the bias current of a JFET is the reverse leakage current of its gate diode, and the reverse leakage current of silicon diodes approximately doubles with every 10°C temperature rise. The bias current of a JFET op-amp is thus not stable with temperature. Indeed, between 25°C and 125°C, the bias current of a JFET op-amp increases by a factor of over 1,000. (The same law applies to MOSFET amplifiers, because the bias current of most MOSFET amplifiers is the leakage current of their gate-protection diodes.)

The offset voltage of a JFET amplifier may be trimmed during manufacture, but minimum offset does not necessarily correspond to minimum temperature drift. It has therefore been necessary to trim offset and drift separately in JFET op-amps, which results in somewhat larger values of voltage offset and drift than are available from the best bipolar amplifiers (values of 250  $\mu V$  and 5  $\mu V/^{\circ}C$  are typical of the best JFET op-amps). Recent studies at Analog Devices, however, have resulted in a patented trimming method which is expected to yield much better values in the next generation of JFET op-amps.

We thus see that there are trade-offs between offset voltage, offset drift, bias current, bias current temperature variation, and noise in operational amplifiers—and that different architectures optimize different features. The table compares the features of the three commonest op-amp architectures. We should note one more category, typified by the new AD705, using bipolar superbeta input transistors; it combines low offset voltage and drift with low bias current and drift.

# CHARACTERISTICS OF OP-AMP INPUT STAGES

|                     | SIMPLE<br>BIPOLAR | BIAS-COMPENSATED<br>BIPOLAR                       | FET                                 |

|---------------------|-------------------|---------------------------------------------------|-------------------------------------|

| OFFSET VOLTAGE      | LOW               | LOW                                               | MEDIUM                              |

| OFFSETDRIFT         | LOW               | LOW                                               | MEDIUM                              |

| BIAS CURRENT        | HIGH              | MEDIUM                                            | LOW-VERY LOW                        |

| BIAS MATCH          | EXCELLENT         | POOR (CURRENT CAN<br>BE IN OPPOSITE<br>DIRECTIONS | FAIR                                |

| BIAS/TEMP VARIATION | LOW               | LOW                                               | BIAS DOUBLES FOR<br>EVERY 10°C RISE |

| NOISE               | LOW               | LOW                                               | FAIR                                |

Q. What other features of op amps should the user know about?

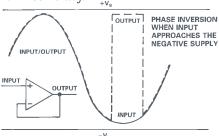

A. A common problem encountered with JFET op-amps is phase inversion. If the input common-mode voltage of a JFET op-amp approaches the negative supply too closely, the

inverting and non-inverting input terminals reverse functions. Negative feedback becomes positive feedback and the circuit may latch up. This latchup is unlikely to be destructive, but power may have to be switched off to correct it. This figure shows the effect of such phase inversion in a circuit where latch-up does not occur. The problem may be avoided by using bipolar amplifiers, or by restricting the common-mode range of the signal in some way.

A more serious form of latchup can occur in both bipolar and JFET op-amps if the input signal becomes more positive or negative than the respective op-amp power supplies. If the input terminals go more positive than  $+Vs+0.7\,V$  or more negative than  $-Vs-0.7\,V$ , current may flow in diodes which are normally biased *off.* This in turn may turn on thyristors (SCRs) formed by some of the diffusions in the op- amp, short-circuiting the power supplies and destroying the device.

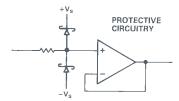

To avoid such destructive latch-up it is important to prevent the input terminals of op-amps from ever exceeding the power supplies. This can have important implications during device turn-on: if a signal is applied to an op-amp before it is powered it may be destroyed at once when power is applied. Whenever there is a risk, either of signals exceeding the voltages on the supplies, or of signals being present prior to power-up of the op-amp, the terminals at risk should be clamped with diodes (preferably fast low-forward-voltage Schottky diodes) to prevent latchup from occurring. Current-limiting resistors may also be needed to prevent the diode current from becoming excessive (see the figure).

This protection circuitry can cause problems of its own. Leakage current in the diode(s) may affect the error budget of the circuit (and if glass-encapsulated diodes are used, their leakage current may be modulated at 100 or 120 Hz due to photoelectric effects if exposed to fluorescent ambient lighting, thus contributing *hum* as well as dc leakage current); Johnson noise in the current-limiting resistor may worsen the circuit's noise performance; and bias current flowing in the resistor may produce an apparent increase in offset voltage. All these effects must be considered when designing such protection.

The important subjects of noise, interference, bypassing, and grounding demand discussion—but we're out of space! We'll come back to them again in future chats; meanwhile you may want to take a look at some of the references in the footnotes on pages 193-4 of The Best of Analog Dialogue, 1967-1991.

by James Bryant and Lew Counts

### **OP-AMP ISSUES—NOISE**

Q. What should I know about op-amp noise?

A. First, we must note the distinction between noise generated in the op amp and its circuit components and *interference*, or unwanted signals and noise arriving as voltage or current at any of the amplifier's terminals or induced in its associated circuitry.

Interference can appear as spikes, steps, sine waves, or random noise, and it can come from *anywhere:* machinery, nearby power lines, r-f transmitters and receivers, computers, or even circuitry within the same equipment (for example, digital circuits or switching-type power supplies). Understanding it, preventing its appearance in your circuit's neighborhood, finding how it got in, and rooting it out, or finding a way to live with it is a big subject. It's been treated in these pages in the past; those, and a few additional references, are mentioned in the Bibliography.

If all interference could be eliminated, there would still be random noise associated with the operational amplifier and its resistive circuits. It constitutes the ultimate limitation on the amplifier's resolution. That's the topic we'll begin to discuss here.

- Q. O.K. Tell me about random noise in op amps. Where does it come from?

- A. Noise appearing at the amplifier's output is usually measured as a voltage. But it is generated by both voltage- and current sources. All internal sources are generally referred to the input, i.e., treated as uncorrelated—or independent—random noise generators (see next question) in series or parallel with the inputs of an ideal noisefree amplifier: We consider 3 primary contributors to noise:

- a noise *voltage* generator (like offset voltage, usually shown in series with the noninverting input)

- two noise-current generators pumping currents out through the two differential-input terminals (like bias current).

- If there are any resistors in the op-amp circuit, they too generate noise; it can be considered as coming from either current sources or voltage sources (whichever is more convenient to deal with in a given circuit).

Op-amp voltage noise may be lower than 1 nV/ $\sqrt{\rm Hz}$  for the best types. Voltage noise is the noise specification that is more usually emphasized, but, if impedance levels are high, current noise is often the limiting factor in system noise performance. That is analogous to offsets, where offset voltage often bears the blame for output offset, but bias current is the actual guilty party. Bipolar op-amps have traditionally had less voltage noise than FET ones, but have paid for this advantage with substantially greater current noise—today, FET op-amps, while retaining their low current noise, can approach bipolar voltage-noise performance.

- Q. Hold it! 1  $nV/\sqrt{Hz}$ ? Where does  $\sqrt{Hz}$  come from? What does it mean?

- A. Let's talk about random noise. Many noise sources are, for practical purposes (i.e., within the bandwidths with which the designer is concerned), both white and Gaussian. White noise is noise whose power within a given bandwidth is independent of frequency. Gaussian noise is noise where the probability of a particular amplitude, *X*, follows a Gaussian distribution.

Gaussian noise has the property that when the rms values of noise from two or more such sources are added, provided that the noise sources are uncorrelated (i.e., one noise signal cannot be transformed into the other), the resulting noise is not their arithmetic sum but the root of the sum-of-their-squares (RSS).\* The RSS sum of three noise sources,  $V_1$ ,  $V_2$ , and  $V_3$ , is

$$V_O = \sqrt{V_1^2 + V_2^2 + V_3^2}$$

Since the different frequency components of a noise signal are uncorrelated, a consequence of RSS summation is that if the white noise in a brick-wall bandwidth of  $\Delta f$  is V, then the noise

in a bandwidth of  $2 \Delta f$  is  $\sqrt{V^2 + V^2} = \sqrt{2} V$ . More generally, if we multiply the bandwidth by a factor K, then we multiply the noise by a factor  $\sqrt{K}$ . The function defining the rms value of noise in a  $\Delta f = 1$  Hz bandwidth anywhere in the frequency range is called the (voltage or current) *spectral density function*, specified in  $nV/\sqrt{Hz}$  or  $pA/\sqrt{Hz}$ . For white noise, the spectral density is constant; it is multiplied by the square root of the bandwidth to obtain the total rms noise.

A useful consequence of RSS summation is that if two noise sources are contributing to the noise of a system, and one is more than 3 or 4 times the other, the smaller is often ignored, since

$$\sqrt{4^2} = \sqrt{16} = 4$$

, while  $\sqrt{4^2 + 1^2} = \sqrt{17} = 4.12$

[difference less than 3%, or 0.26 dB]

$$\sqrt{3^2} = \sqrt{9} = 3$$

, while  $\sqrt{3^2 + 1^2} = \sqrt{10} = 3.16$

[difference less than 6%, or 0.5 dB]

The source of the higher noise has become the *dominant* source.

- Q. O.K. How about current noise?

- A. The current noise of simple (i.e. not bias-current-compensated) bipolar and JFET op-amps is usually within 1 or 2 dB of the Schottky noise (sometimes called the "shot noise") of the bias current; it is not always specified on data sheets. Schottky noise is current noise due to random distribution of charge carriers in the current flow through a junction. The Schottky noise current,  $I_n$ , in a bandwidth, B, when a current, I, is flowing is obtained from the formula

$$I_n = \sqrt{2I \ qB}$$

Where *q* is the electron charge (1.6×10<sup>-19</sup> C). Note that  $\sqrt{2I q}$  is the spectral density, and that the noise is white.

This tells us that the current noise spectral density of simple bipolar transistor op-amps will be of the order of 250 fA/ $\sqrt{\rm Hz}$ , for  $I_b$  = 200 nA, and does not vary much with temperature—and that the current noise of JFET input op-amps, while lower (4 fA/ $\sqrt{\rm Hz}$  at  $I_b$ , = 50 pA), will double for every 20°C chip temperature increase, since JFET op-amps' bias currents double for every 10°C increase.

Bias-compensated op-amps have much higher current noise than one can predict from their input currents. The reason is that their net bias current is the *difference* between the base current of the input transistor and the compensating current source, while the noise current is derived from the *RSS sum* of the noise currents.

Traditional voltage-feedback op-amps with balanced inputs almost always have equal (though uncorrelated) current noise on both

[\*Note the implication that noise *power* adds linearly (sum of squares).]

their inverting and non-inverting inputs. Current-feedback, or transimpedance, op-amps, which have different input structures at these two inputs, do not. Their data sheets must be consulted for details of the noise on the two inputs.

The noise of op-amps is Gaussian with constant spectral density, or "white", over a wide range of frequencies, but as frequency decreases the spectral density starts to rise at about 3 dB/octave. This low-frequency noise characteristic is known as "1/f noise" since the noise power spectral density goes inversely with frequency (actually  $1/f^{\gamma}$ ). It has a -1 slope on a log plot (the noise *voltage* (or *current*)  $1/\sqrt{f}$  spectral density slopes at -1/2). The frequency at which an extrapolated -3 dB/ octave spectral density line intersects the midfrequency constant spectral density value is known as the "l/f corner frequency" and is a figure of merit for the amplifier. Early monolithic IC op-amps had 1/f corners at over 500 Hz, but today values of 20-50 Hz are usual, and the best amplifiers (such as the AD-OP27 and the AD-OP37) have corner frequencies as low as 2.7 Hz. 1/f noise has equal increments for frequency intervals having equal ratios, i.e., per octave or per decade.

- Q. Why don't you publish a noise figure?

- A. The noise figure (NF) of an amplifier (expressed in dB) is a measure of the ratio of the amplifier noise to the thermal noise of the source resistance.

$$V_n = 20 \log \{ [V_n(amp) + V_n(source)] / V_n(source) \}$$

It is a useful concept for r-f amplifiers, which are almost always used with the same source resistance driving them (usually  $50~\Omega$  or  $75~\Omega$ ), but it would be misleading when applied to op amps, since they are used in many different applications with widely varying source impedances (which may or may not be resistive).

- Q. What difference does the source impedance make?

- A. At temperatures above absolute zero all resistances are noise sources; their noise increases with resistance, temperature, and bandwidth (we'll discuss basic resistance noise, or *Johnson noise*, in a moment). *Reactances* don't generate noise, but noise currents through them will develop noise voltages.

If we drive an op-amp from a source resistance, the equivalent noise input will be the RSS sum of the amplifier's noise voltage, the voltage generated by the source resistance, and the voltage caused by the amplifier's  $I_n$  flowing through the source impedance. For very low source resistance, the noise generated by the source resistance and amplifier current noise would contribute insignificantly to the total. In this case, the noise at the input will effectively be just the voltage noise of the op-amp.

If the source resistance is higher, the Johnson noise of the source resistance may dominate both the op-amp voltage noise and the voltage due to the current noise; but it's worth noting that, since the Johnson noise only increases with the square root of the resistance, while the noise voltage due to the current noise is directly proportional to the input impedance, the amplifier's current noise will always dominate for a high enough value of input impedance. When an amplifier's voltage and current noise are high enough, there may be no value of input resistance for which Johnson noise dominates.

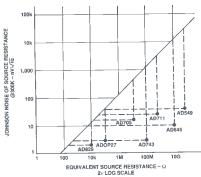

This is demonstrated by the figure nearby, which compares voltage and current noise noise for several Analog Devices op amp types, for a range of source-resistance values. The diagonal line plots vertically the Johnson noise associated with resistances

on the horizontal scale. Let's read the chart for the ADOP27: The horizontal line indicates the ADOP27's voltage noise level of about 3 nV/ $\sqrt{\rm Hz}$  is equivalent to a source resistance of less than about 500  $\Omega$ . Noise will not be reduced by (say) a 100- $\Omega$  source impedance, but it will be increased by a 2-k $\Omega$  source impedance. The vertical line for the ADOP27 indicates that, for source resistances above about 100 k $\Omega$ , the noise voltage produced by amplifier's current noise will exceed that contributed by the source resistance; it has become the dominant source.

Remember that any resistance in the non-inverting input will have Johnson noise and will also convert current noise to a noise voltage; and Johnson noise in feedback resistors can be significant in high-resistance circuits. All potential noise sources must be considered when evaluating op amp performance.

- Q. You were going to tell me about Johnson noise.

- A. At temperatures above absolute zero, all resistances have noise due to thermal movement of charge carriers. This is called Johnson noise. The phenomenon is sometimes used to measure cryogenic temperatures. The voltage and current noise in a resistance of *R* ohms, for a bandwidth of *B* Hz, at a temperature of T kelvins, are given by:

$$V_n = \sqrt{4kTRB}$$

and  $I_n = \sqrt{4kTB/R}$

Where k is Boltzmann's Constant (1.38 × 10<sup>-23</sup> J/K). A handy rule of thumb is that a 1-k $\Omega$  resistor has noise of 4 nV/ $\sqrt{\rm Hz}$  at room temperature.

All resistors in a circuit generate noise, and its effect must always be considered. In practice, only resistors in the input(s) and, perhaps, feedback, of high-gain, front-end circuitry are likely to have an appreciable effect on total circuit noise.

Noise can be reduced by reducing resistance or bandwidth, but temperature reduction is generally not very helpful unless a resistor can be made very cold—since noise power is proportional to the *absolute* temperature,  $T = {}^{\circ}C + 273^{\circ}$ .

(to be continued)

### **REFERENCES**

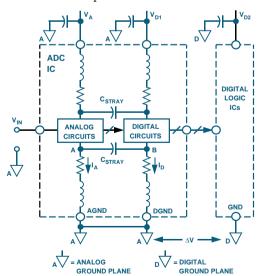

Barrow, J., and A. Paul Brokaw, "Grounding for Low- and High-Frequency Circuits," *Analog Dialogue* 23-3, 1989.

Bennett, W. R., Electrical Noise. New York: McGraw-Hill, 1960.

Freeman, J. J., *Principles of Noise*. New York: John Wiley & Sons, Inc., 1958. Gupta, Madhu S., ed., *Electrical Noise: Fundamentals & Sources*. New York: IEEE Press, 1977. Collection of classical reprints.

Motchenbacher, C. D., and F. C. Fitchen, *Low-Noise Electronic Design*. New York: John Wiley & Sons, Inc., 1973.

Rice, S.O., "Math Analysis for Random Noise" *Bell System Technical Journal* 23 July, 1944 (pp 282–332).

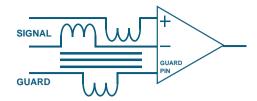

Rich, Alan, "Understanding Interference-Type Noise," Analog Dialogue 16-3, 1982.

---, "Shielding and Guarding," Analog Dialogue 17-1, 1983.

Ryan, Al, and Tim Scranton, "DC Amplifier Noise Revisited," *Analog Dialogue* 18-1, 1984.

van der Ziel, A. Noise. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1954.

ightharpoons

by James Bryant

### **OP-AMP ISSUES**

(Noise, continued from the last issue, 24-2)

- Q. What is "noise gain"?

- A. So far we have considered noise sources but not the gain of the circuits where they occur. It is tempting to imagine that if the noise voltage at the input of an amplifier is  $V_n$  and the circuit's signal gain is G, the noise voltage at the output will be  $GV_n$ ; but this is not always the case.

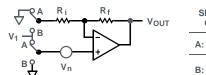

Consider the basic op-amp gain circuit in the diagram. If it is being used as an inverting amplifier (B), the non-inverting input will be grounded, the signal will be applied to the free end of  $R_i$  and the gain will be  $-R_{f}R_i$ . On the other hand, in a non-inverting amplifier (A) the signal is applied to the non-inverting input and the free end of  $R_i$  is grounded; the gain is  $(1 + R_f/R_i)$

$\left(1 + \frac{R_f}{R_i}\right)$

The amplifier's own voltage noise is always amplified in the non-inverting mode; thus when an op-amp is used as an inverting amplifier at a gain of G, its voltage noise will be amplified by the noise gain of G+1. For the precision attenuation cases, where G<1, this may present problems. (A common example of this is an active filter circuit where stopband gain may be very small but stop-band noise gain is at least unity.)

Only the amplifier voltage noise—and any noise developed by the noninverting-input current noise flowing in any impedance present in that input (for example, a bias-current compensation resistor)—is amplified by the noise gain. Noise in  $R_i$ , either Johnson noise or arising from inverting input noise current, is amplified by G in the same way as the input signal, and Johnson noise voltage in the feedback resistor is not amplified but is buffered to the output at unity gain.

- Q. What's "popcorn" noise?

- A. Twenty years ago this column would have spent a great deal of space discussing popcorn noise, which is a type of low frequency noise manifesting itself as low level (but random amplitude) step changes in offset voltage occurring at random intervals. When played through a loudspeaker it sounds like cooking popcorn—hence the name.

While no integrated circuit process is entirely free from the problem, high levels of popcorn noise result from inadequate processing techniques. Today its causes are sufficiently well understood that no reputable op-amp manufacturer is likely to produce op-amps where popcorn noise is a major concern to the user. {Oat-bran noise is more likely to be an issue in situations where cereal data is concerned[:-)]}

Q. Pk-pk noise voltage is the most convenient way to know whether noise will ever be a problem for me. Why are amplifier manufacturers reluctant to specify noise in this way?

A. Because noise is generally Gaussian, as we pointed out in the last issue. For a Gaussian distribution it is meaningless to speak of a maximum value of noise: if you wait long enough any value will, in theory, be exceeded. Instead it is more practical to speak of the rms noise, which is more or less invariant—and by applying the Gaussian curve to this we may predict the probability of the noise exceeding any particular value. Given a noise source of *V* rms, since the probability of any particular value of noise voltage follows a Gaussian distribution, the noise voltage will exceed a pk-pk value of 2 V for 32% of the time, 3 V for 13% of the time, and so on:

| Pk-pk value      | % of time pk-pk value is exceeded |  |  |  |

|------------------|-----------------------------------|--|--|--|

| $2\times rms$    | 32%                               |  |  |  |

| $4 \times rms$   | 4.6%                              |  |  |  |

| $6 \times rms$   | 0.27%                             |  |  |  |

| $6.6 \times rms$ | 0.10%                             |  |  |  |

| $8 \times rms$   | 60 ppm                            |  |  |  |

| $10 \times rms$  | 0.6 ppm                           |  |  |  |

| $12\times rms$   | $2 \times 10^{-9} \text{ ppm}$    |  |  |  |

| $14 \times rms$  | $2.6 \times 10^{-12} \text{ ppm}$ |  |  |  |

So if we define a peak value in terms of the probability of its occurrence, we may use a peak specification—but it is more desirable to use the rms value, which is generally easier to measure. When a peak noise voltage is specified, it is frequently  $6.6 \times \text{rms}$ , which occurs no more than 0.1% of the time.

- Q. How do you measure the rms value of low-frequency noise in the usually specified band, 0.1 to 10 Hz? It must take a long time to integrate. Isn't this expensive in production?

- A. Yes, it is expensive, but—Although it's necessary to make many careful measurements during characterization, and at intervals thereafter, we cannot afford the time it would take in production to make an rms measurement. Instead, at very low frequencies in the 1/f region (as low as 0.1 to 10 Hz), the peak value is measured during from one to three 30-second intervals and must be less than some specified value. Theoretically this is unsatisfactory, since some good devices will be rejected and some noisy ones escape detection, but in practice it is the best test possible within a practicable test time and is acceptable if a suitable threshold limit is chosen. With conservative weightings applied, this is a reliable test of noise. Devices that do not meet the arbitrary criteria for the highest grades can still be sold in grades for which they meet the spec.

- Q. What other op-amp noise effects do you encounter?

- A. There is a common effect, which often appears to be caused by a noisy op amp, resulting in missing codes. This potentially serious problem is caused by ADC input-impedance modulation. Here's how it happens:

Many successive-approximation ADCs have an input impedance which is modulated by the device's conversion clock. If such an ADC is driven by a precision op amp whose bandwidth is much lower than the clock frequency, the op amp cannot develop sufficient feedback to provide a stiff voltage source to the ADC input port, and missing codes are likely to occur. Typically, this effect appears when amplifiers like the OP-07 are used to drive AD574s.

It may be cured by using an op amp with sufficient bandwidth to have a low output impedance at the ADC's clock frequency, or by choosing an ADC containing an input buffer or one whose input impedance is not modulated by its internal clock (many sampling ADCs are free of this problem). In cases where the op amp can drive a capacitive load without instability, and the reduction of system bandwidth is unimportant, a shunt capacitor decoupling the ADC input may be sufficient to effect a cure.

- Q. Are there any other interesting noise phenomena in high-precision analog circuits?

- A. The tendency of high-precision circuitry to drift with time is a noise-like phenomenon (in fact, it might be argued that, at a minimum, it is identical to the lower end of 1/f noise). When we specify long-term stability, we normally do so in terms of  $\mu V/1,000$  hr or ppm/1,000 hr. Many users assume that, since there are, on the average, 8,766 hours in a year, an instability of x/1,000 hr is equal to 8.8 x/yr.

This is not the case. Long-term instability (assuming no long-term steady deterioration of some damaged component within the device), is a "drunkard's walk" function; what a device did during its last 1,000 hours is no guide to its behavior during the next thousand. The long-term error mounts as the squareroot of the elapsed time, which implies that, for a figure of x/1,000 hr, the drift will actually be multiplied by  $\sqrt{8.766}$ , or about  $3\times$  per year, or  $9\times$  per 10 years. Perhaps the spec should be in  $\mu V/1,000 \sqrt{hr}$ .

In fact, for many devices, things are a bit better even than this. The "drunkard's walk" model, as noted above, assumes that the properties of the device don't change. In fact, as the device gets older, the stresses of manufacture tend to diminish and the device becomes more stable (except for incipient failure sources). While this is hard to quantify, it is safe to say that—provided that a device is operated in a low-stress environment—its rate of long-term drift will tend to reduce during its lifetime. The limiting value is probably the 1/f noise, which builds up as the *square-root of the natural logarithm* of the ratio, i.e.,  $\sqrt{\ln 8.8}$  for time ratios of 8.8, or  $1.47 \times \text{for 1 year}$ ,  $2.94 \times \text{for 8.8 years}$ ,  $4.4 \times \text{for 77 years}$ , etc.

# A READER'S CHALLENGE:

Q. A reader sent us a letter that is just a wee bit too long to quote directly, so we'll summarize it here. He was responding to the mention in these columns (Analog Dialogue 24-2, pp. 20-21) of the shot effect, or Schottky noise (Schottky was the first to note and correctly interpret shot effect—originally in vacuum tubes¹). Our reader particularly objected to the designation of shot noise as solely a junction phenomenon, and commented that we have joined the rest of the semiconductor and op-amp engineering fraternity in disseminating misinformation.

In particular, he pointed out that the shot noise formula-

$$I_n = \sqrt{2q \ IB}$$

amperes,

where  $I_n$  is the rms shot-noise current, I is the current flowing through a region, q is the charge of an electron, and B is the bandwidth—does not seem to contain any terms that depend on the physical properties of the region. Hence (he goes on) shot noise is a *universal* phenomenon associated with the fact

that any current, *I*, is a flow of electrons or holes, which carry discrete charges, and the noise given in the formula is just an expression of the graininess of the flow.

He concludes that the omission of this noise component in any circuit carrying current, including purely resistive circuits, can lead to serious design problems. And he illustrates its significance by pointing out that this noise current, calculated from the flow of dc through any ideal resistor, becomes equal to the thermal Johnson noise current at room temperature when only 52 mV is applied to the resistor—and it would become the dominant current noise source for applied voltages higher than about 200 mV.

A. Since designers of low-noise op amps have blithely ignored this putative phenomenon, what's wrong? *The assumption that the above shot noise equation is valid for conductors.*

Actually, the shot noise equation is developed under the assumption that the carriers are independent of one another. While this is indeed the case for currents made up of discrete charges crossing a barrier, as in a junction diode (or a vacuum tube), it is not true for metallic conductors. Currents in conductors are made up of very much larger numbers of carriers (individually flowing much more slowly), and the noise associated with the flow of current is accordingly very much smaller—and generally lost in the circuit's Johnson noise.

Here's what Horowitz and Hill<sup>2</sup> have to say on the subject:

"An electric current is the flow of discrete electric charges, not a smooth fluidlike flow. The finiteness of the charge quantum results in statistical fluctuations of the current. *If the charges act independently of each other*,\* the fluctuating current is . . .

I noise (rms) =

$$I_{nR}$$

=  $(2 qI_{dc} B)^{1/2}$

where q is the electron charge  $(1.60 \times 10^{-19}~C)$  and B is the measurement bandwidth. For example, a "steady" current of 1 A actually has an rms fluctuation of 57 nA, measured in a 10-kHz bandwidth; i.e., it fluctuates by about 0.000006%. The relative fluctuations are larger for smaller currents: A "steady" current of 1  $\mu$ A actually has an rms current-noise fluctuation, over 10 kHz, of 0.006%, i.e., –85 dB. At 1 pA dc, the rms current fluctuation (same bandwidth) is 56 fA, i.e., a 5.6% variation! Shot noise is 'rain on a tin roof.' This noise, like resistor Johnson noise, is Gaussian and white.

"The shot noise formula given earlier assumes that the charge carriers making up the current act independently. That is indeed the case for charges crossing a barrier, as for example the current in a junction diode, where the charges move by diffusion; but it is not true for the important case of metallic conductors, where there are long-range correlations between charge carriers. Thus the current in a simple resistive circuit has far less noise than is predicted by the shot noise formula.\* Another important exception to the shot-noise formula is provided by our standard transistor current-source circuit, in which negative feedback acts to quiet the shot noise."

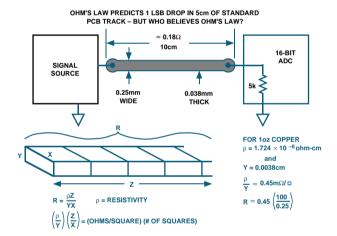

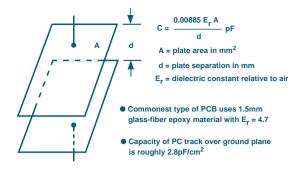

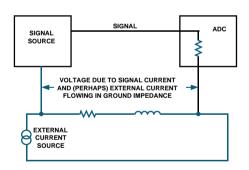

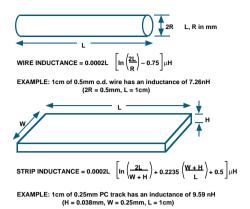

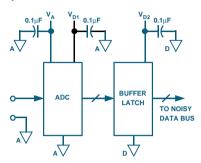

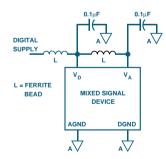

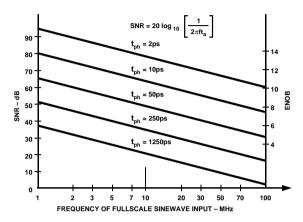

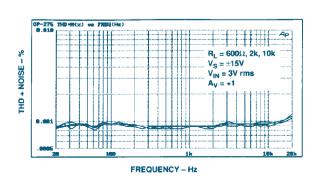

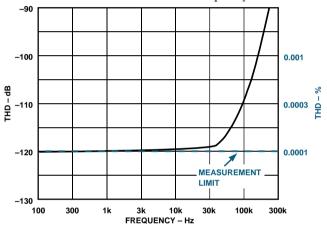

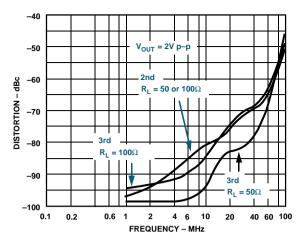

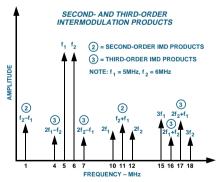

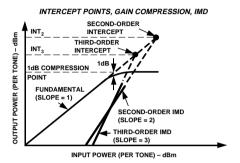

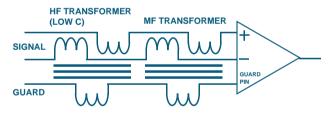

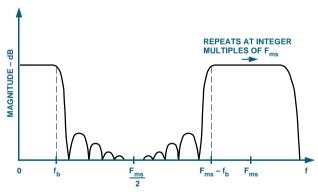

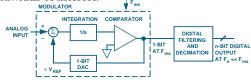

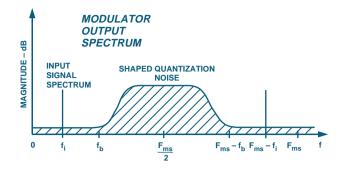

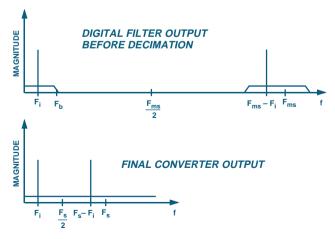

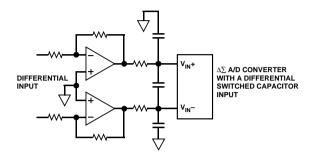

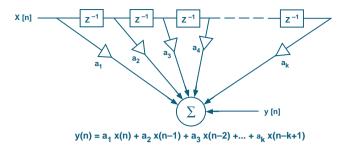

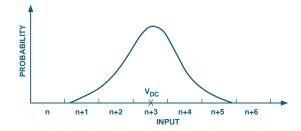

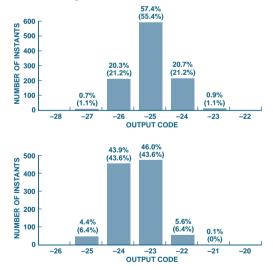

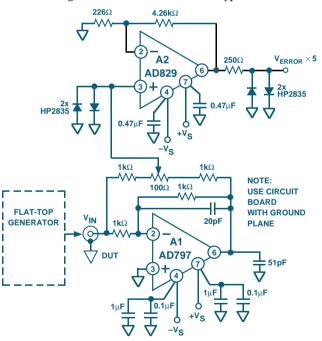

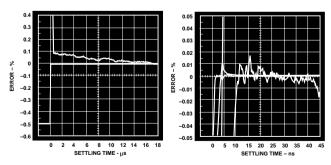

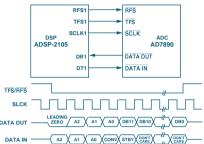

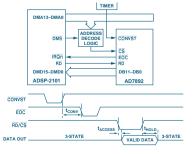

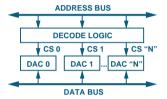

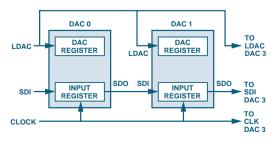

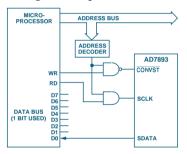

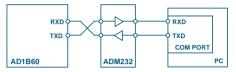

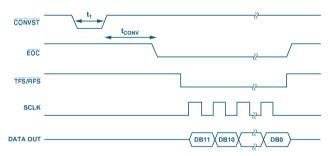

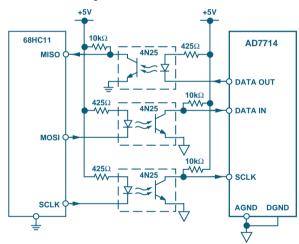

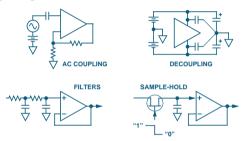

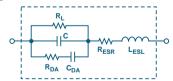

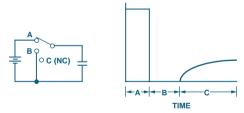

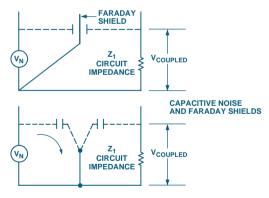

<sup>\*</sup>Italics ours