# Direct Digital Synthesis (DDS)

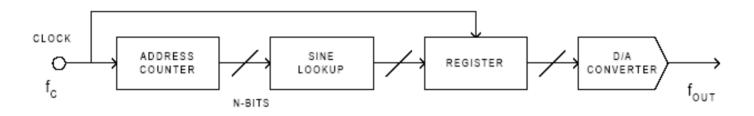

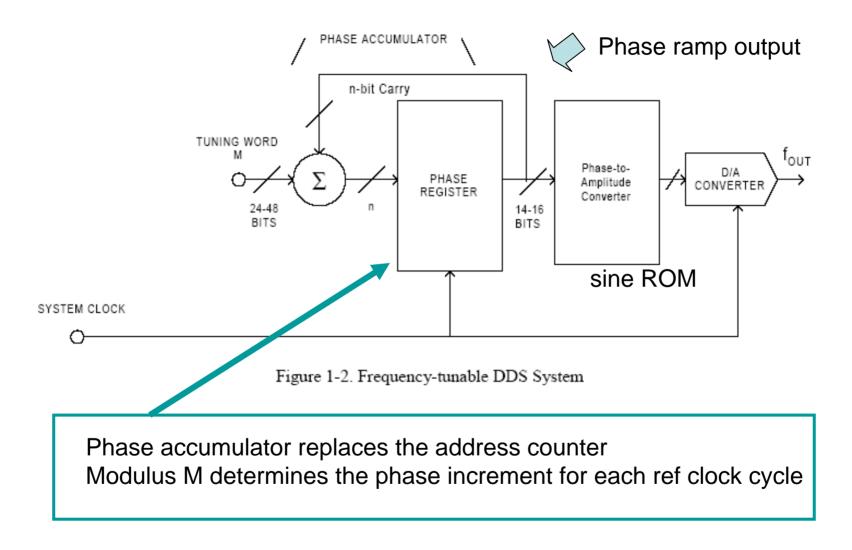

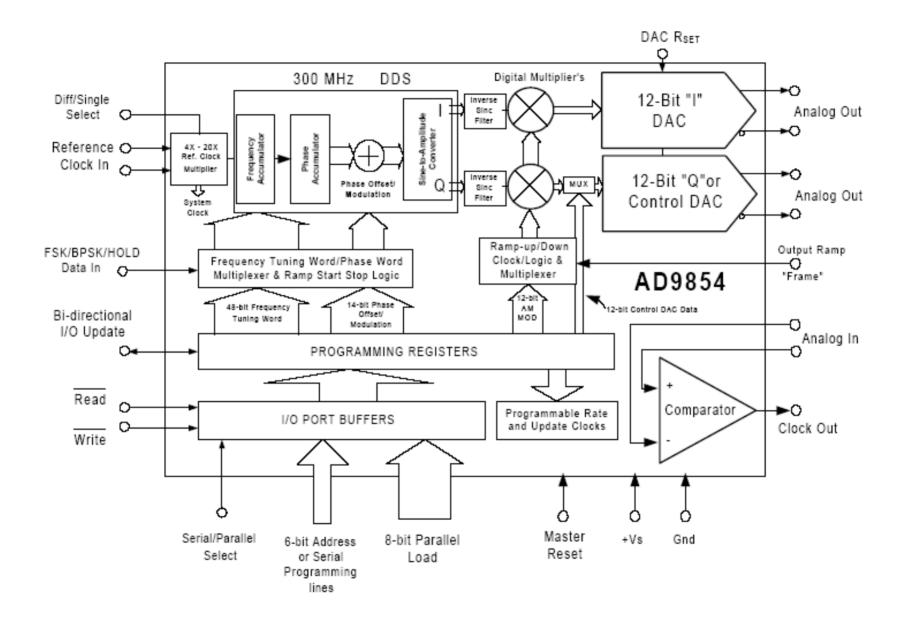

Figure 1-1. Simple Direct Digital Synthesizer

- Micro-Hertz frequency, sub-degree phase resolution

- Extremely fast hopping no settling time constraints

- Phase-continuous frequency hops

- Digital control

- Precise quadrature phase generation for I Q

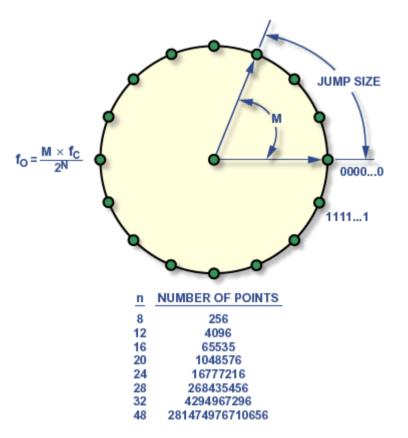

## Phase Wheel

Each rotation around the wheel corresponds to one cycle

$$F_{out} = M \bullet F_{REF} / 2^N$$

N = # bits of phase accumulator M = binary tuning word

Ex. N = 32; M = 1 One full cycle every  $2^{32}$  clocks N = 32; M = 31 One full cycle every 2 clocks

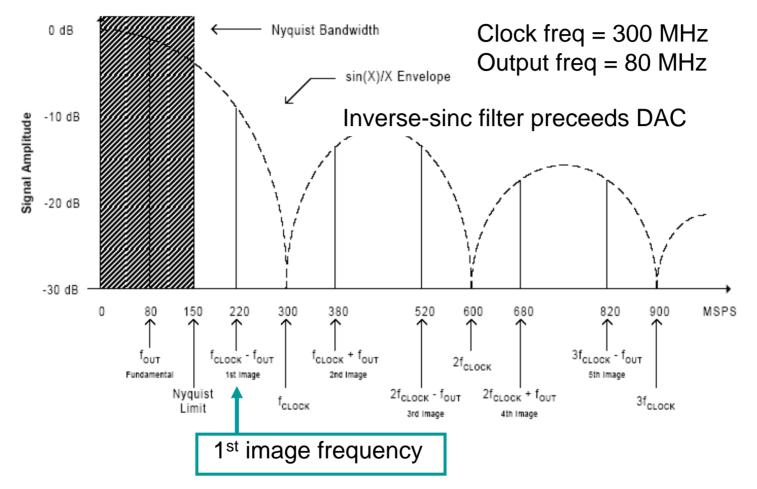

Analog low-pass anti-aliasing filter Is needed at the output

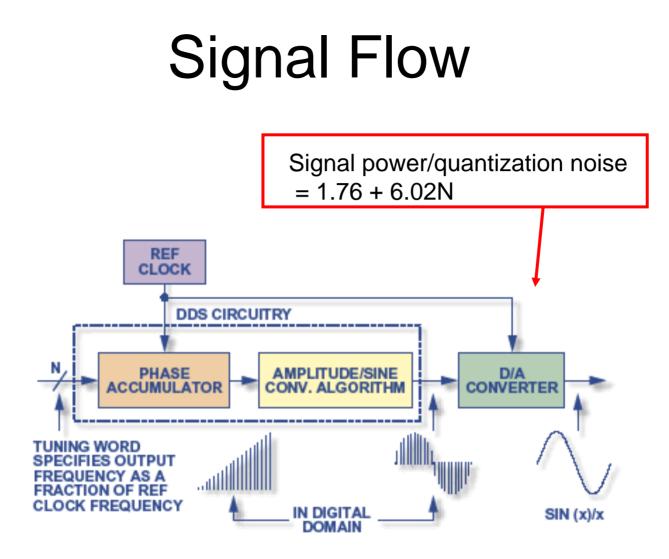

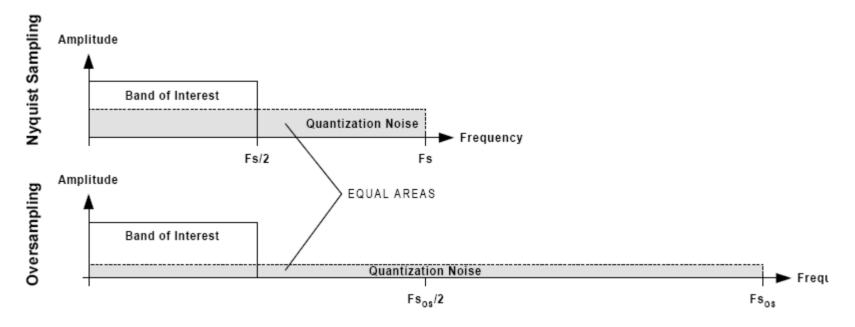

#### Oversampling can be used to reduce the quantization noise

Figure 4.3. The Effect of Oversampling on SQR

```

10\log(F_{OS} / F_{Nyquist})

```

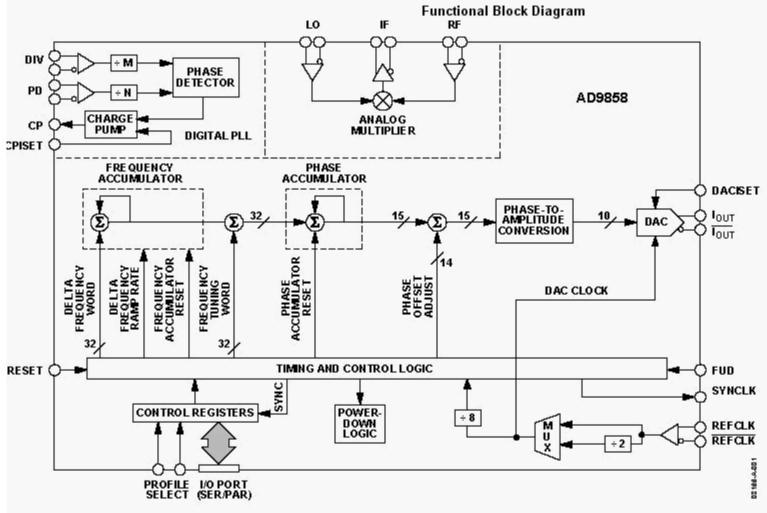

### AD9858 DDS

Clock freq = 1 GHz

Resolution: 10 bits

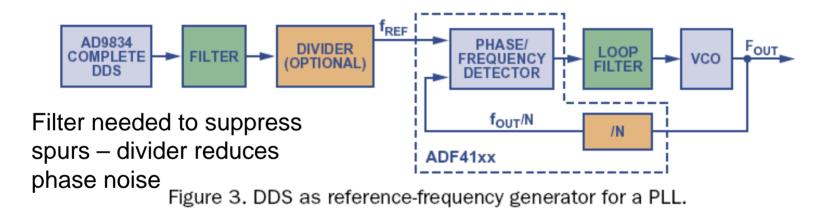

## Hybrid synthesizers

- Integer-N and DDS synthesizers can be combined for

- better SNR

- Finer tuning steps with wide loop BW

- Higher reference frequency

- Avoid complications of Fractional-N

Ex.  $f_{REF} = 5 \text{ MHz}$ ;  $F_{out} = 100 - 500 \text{ MHz}$ ; N = 20 - 100 each step is 5 MHz

But: f<sub>REF</sub> can be very finely adjusted to give frequencies between steps

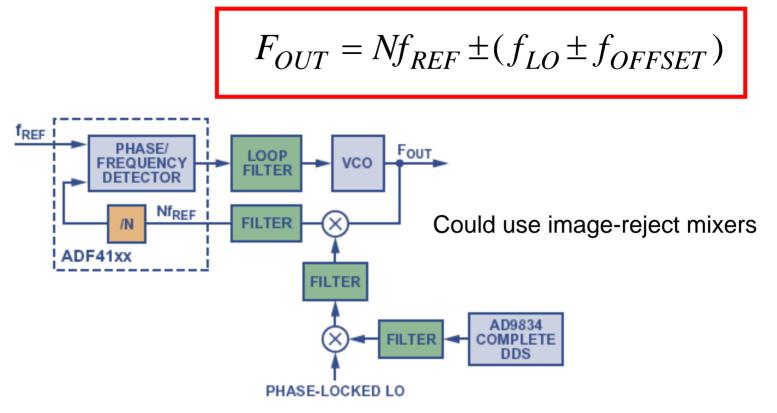

Analog Dialogue, 39-08, Aug. 2005

Figure 4. The AD9834 DDS generates the frequency offset for the ADF41xx PLL.

DDS provides small incremental frequency steps between each coarse step of the PLL.

Analog Dialogue, 39-08, Aug. 2005