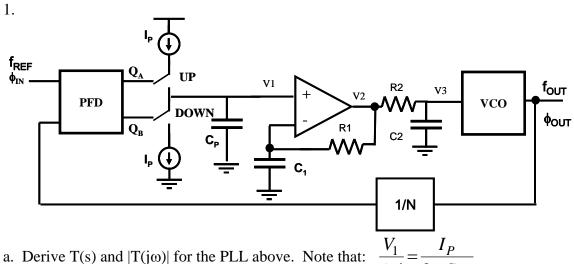

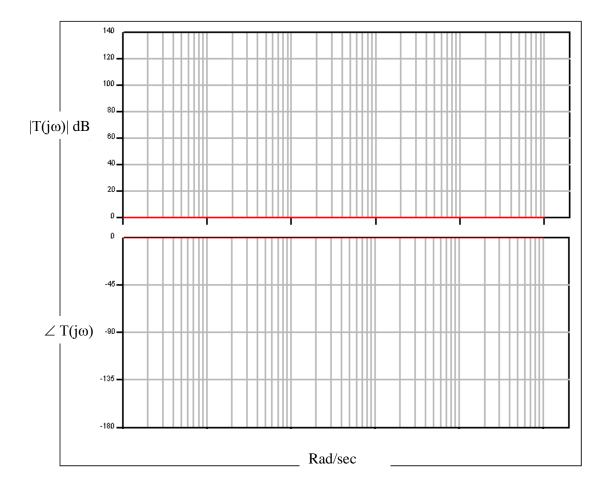

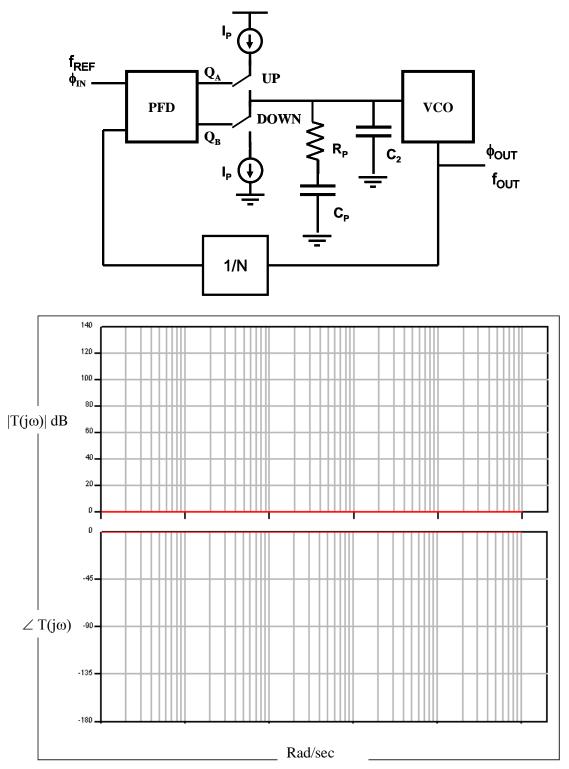

a. Derive T(s) and  $|T(j\omega)|$  for the PLL above. Note that:  $\frac{1}{\Delta \phi} = \frac{1}{2\pi C_F}$

b. The magnitude of T at 1 rad/sec is 120 dB. Also,

| $I_P$            | 0.1 mA                           |

|------------------|----------------------------------|

| Ko               | 6.28 x 10 <sup>5</sup> rad/sec/V |

| F <sub>ref</sub> | 100 kHz                          |

| Fout             | 100 MHz                          |

## Determine C<sub>P</sub>

- c. Assuming C2 = 0, determine the zero frequency needed to set the crossover frequency,  $\omega c = 3000 \text{ rad/sec}$ . If R1 = 10k, find C1.

- d. Now add the third pole to make the phase margin 60 degrees. If R2 = 10k, find C2. What will be the phase margin for this crossover frequency?

- e. How much spur rejection is expected for this combination?

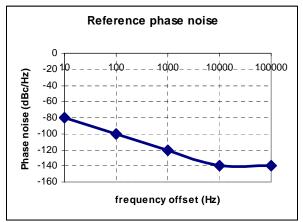

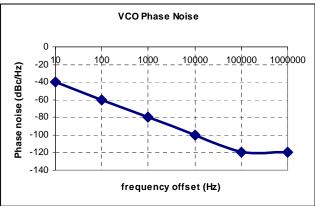

f. The phase noise power to carrier power ratio,  $L(\Delta f)$ , vs. offset frequency is displayed in the plots below for the reference oscillator and the VCO of the PLL in part a.

What will be the phase noise N/C ratio at the output of the VCO at a 100 Hz offset frequency  $(\Delta f)$ ? Explain why.

What will it be at 10 kHz offset? Explain why.

g. Explain why low phase noise is important for local oscillator PLL applications.

2. a. Using your VCO from Lab 2, design a third-order CP PLL with the required frequency step, settling time and reference spur specifications. Choose Ip to be either 1.176mA or 2.5 mA. Use the procedure from the PLL Notes 2 or Vaucher for your design.

b. Verify with ADS.