lec. 6 analog to Digital Converters Anabog input is quantized. Output is a digital code. Performance metrics are similar to Trade-Hold and DACS.

| Static:         | Dynamic :        |

|-----------------|------------------|

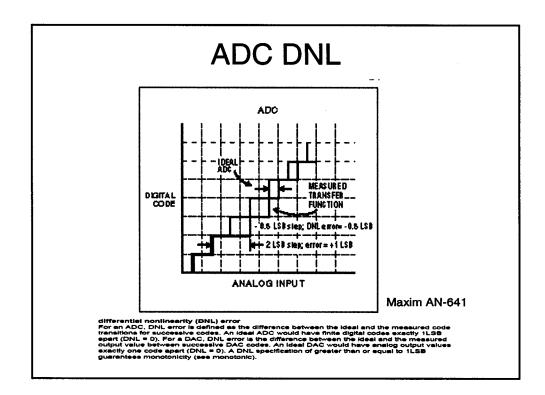

| DNL             | SNR              |

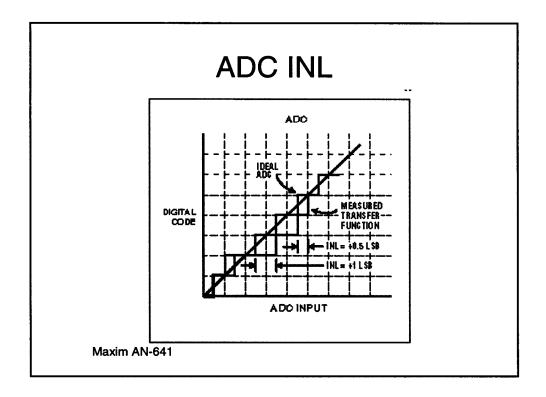

| INL             | SNDR             |

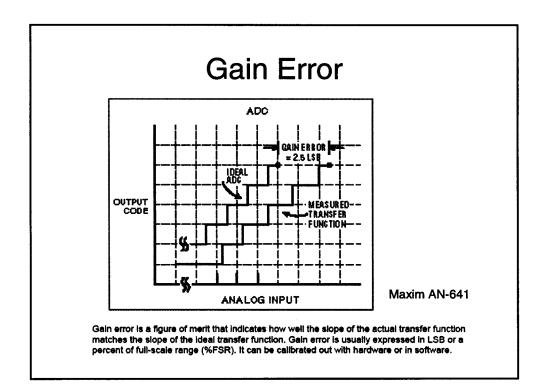

| gain error      | SFDR             |

| offset enor     | aperture jitter  |

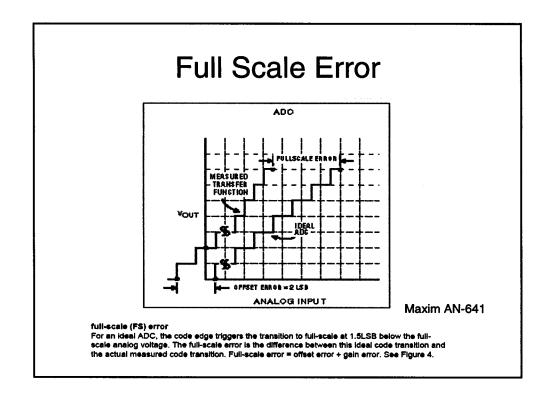

| fill-scale ener | Settling time    |

|                 | acquisition time |

For frequency domain applications, the accuracy of the ADC is limited by Spurs, just as was true for the DAC.

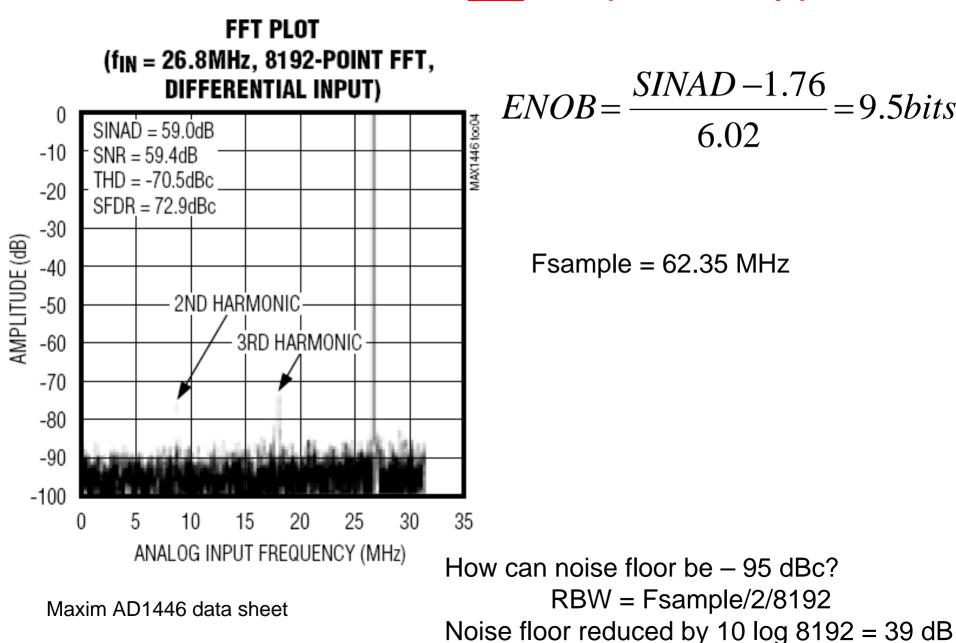

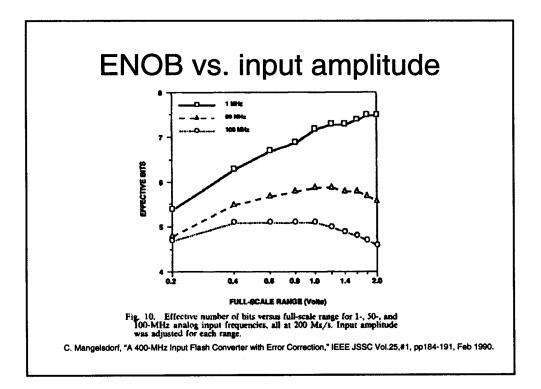

Define an effective # of bits (ENOB)

$$ENOB = \frac{SND_R(orSFDR) - 1.76}{6.02}$$

So, taking the dynamic range that is given by hamonics, aliases, intermods and using that to judge the converter.

Extend noise.

Input wideband noise will be aliased into the Nyquist band. So, a low-pass filter must be used to attenuate extend noise. Otherwise, SNR or SFDR will be compromised.

#### SNR = 6 x 10bits + 1.76 = 62 dB = *total* noise power over Nyquist BW

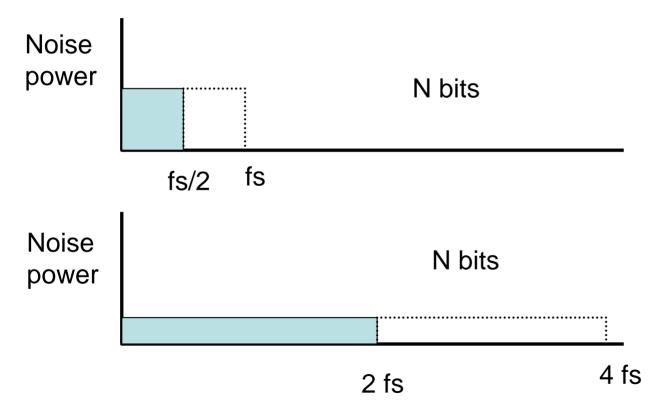

# Oversampling

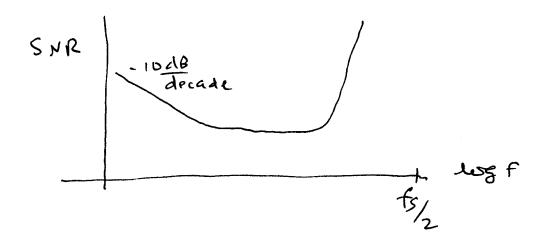

- Sampling frequency can be increased to spread quantization noise over wider Nyquist bandwidth.

- Then, noise power in a given signal bandwidth will be reduced.

## Effective Resolution Bandwidth

- Increase input frequency at fixed fs

- ERBW = The frequency at which the SNR drops by 3 dB (1/2 LSB) compared with SNR at low input frequency.

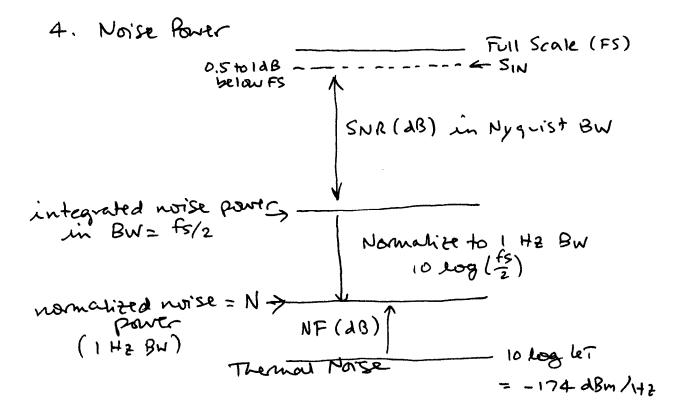

Noise Figure  $F = \frac{(S_{N})_{in}}{(S_{N})_{out}}$  NF = 10 log F

Nyquist ADCS are used in receivers, generally at IF, although for lower RF frequencies and lower SDFR, in front ends. NF needed for system analysis. We can calculate an effective noise figure for an ADC:

- 1. assume white noise across Nygust band. fs/2

- 2. SNR is determined for continuous sinusoridal input signal 0.5 to 1 dB below full scale level.

ideally SNR = 6.02N+1.76 dB

but there are many factors that can degrade this \_

3. Full Scale Power Peak voltage Vp Signal Power =  $\sin = \frac{V_p^2}{2R_{IN}}$  (watts)  $dBm = 10 \log(S_{in}) + 30 dB$

$$S_{in}(dBm) - SNR - 10 \log(\frac{fs}{2}) = \text{effective} = N$$

noise perer

normalized to

1 Hz BW.

50 NF = -224 ale N- (-174) dB

example.

1. Suppose

$$FS = 2V$$

.  $P_{IN} = 50D$

$Vp = 1V$   $S_{in} = \frac{1}{100} = 01W = 10MW$

$= 10dBm$

Drop back IdB -> 9dBm

10

$$\log\left(\frac{fs}{2}\right) = 10 \log(5 \times 10^7) = 77 dB$$

3. Normalized Noise Power = -56 dBm - 77 dB

= -133 dBm

So you would expect to see SNR improve with fs up to the point where jitter or TH guitches start to dominate

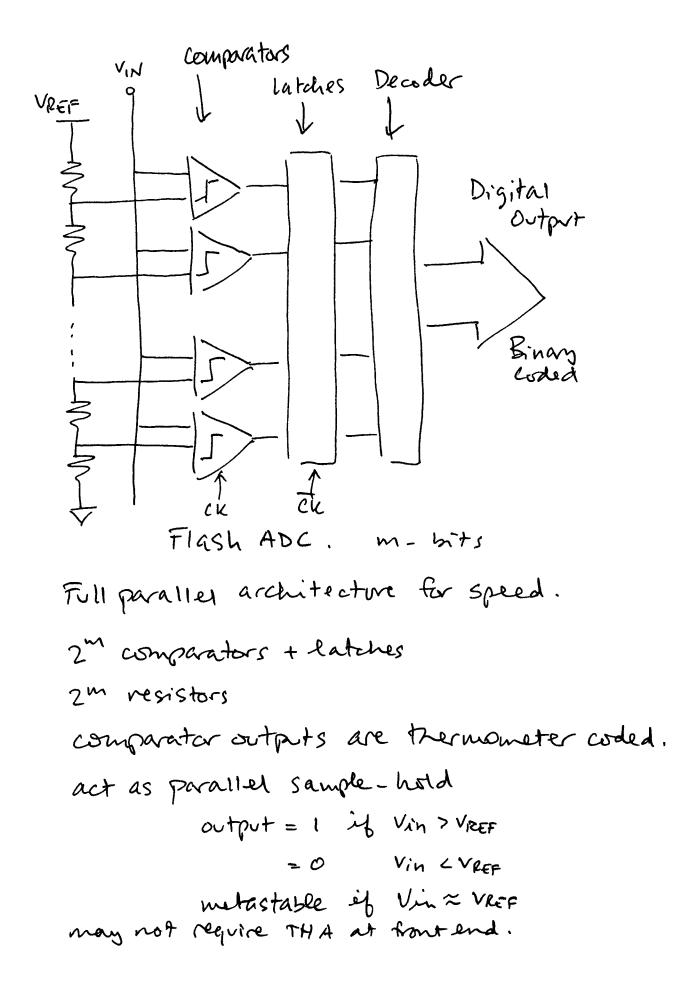

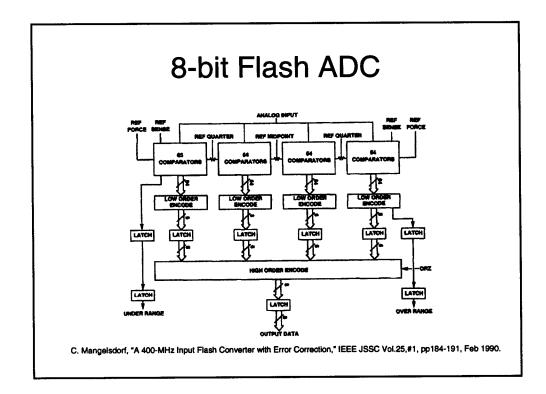

### large number of components generally limits flash converters to 8 bits or less.

### Errors! 1. Reference static and dynamic errors. A. resistor mismatch. same considerations as in resistor chain DAC. D. him wore te

each tap voitage is decreased.

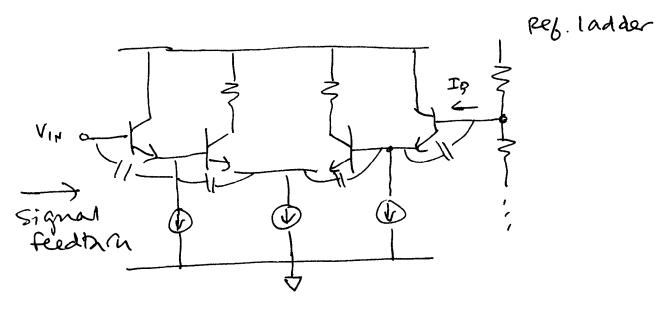

C. signal feedtrin is worse at higher freq, disturbs reference voltages dynamically.

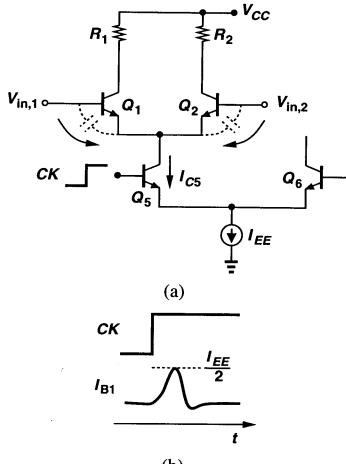

Fig. 7.23 Generation of kickback noise in a bipolar comparator.

B. Razavi, Data Conversion System Design, IEEE Press, 1995.

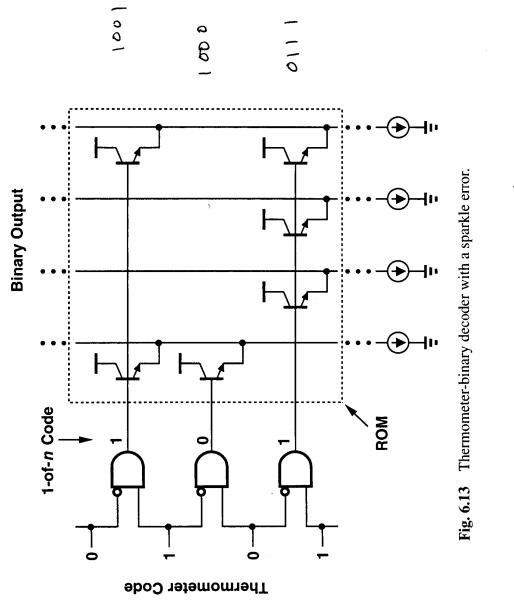

churd be 1000 > instead we get 1111 half of full scale error

0 -

6

E. Kickback, when comparators are strobbed, noise is generated at Their inputs.

( Fig. 7.21, 7.23)

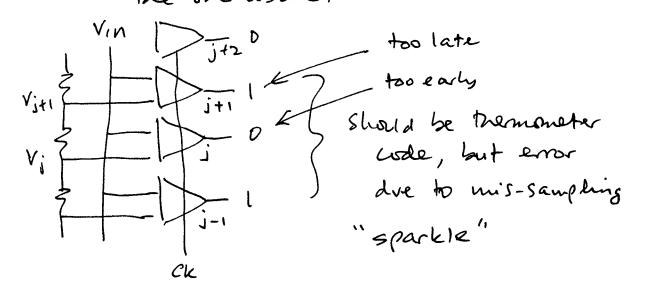

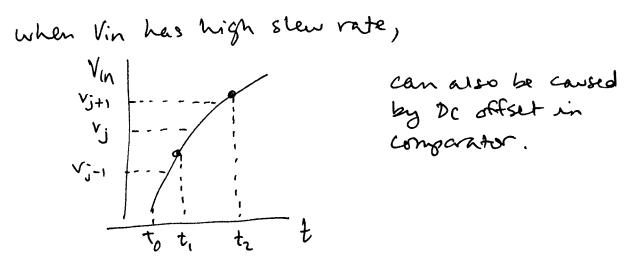

- F. comparator aperture uncertainty.

- · comparators may not be identical or

- · clock delay causes a laver comparator to latch earlier than the one above.

Figs. 6.12, 6.13 Razavi, can cause huge errors in themd. -> binary conversion. Degrades SNR, creates distortion

#### lec. 7

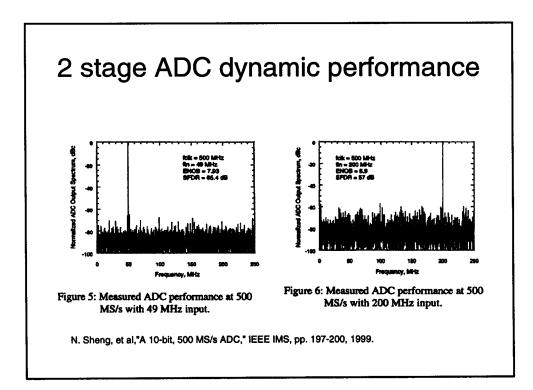

Last time: ADC Static performance dynamic performance  $ENOB = \frac{SFDR - 1.76}{6.02}$ Norse figure Flash ADC architecture errors: mismatch londing delay on RC impet network bubbles or sparleles in them. code Today : Comparator metastability 2-step converters

interpolation

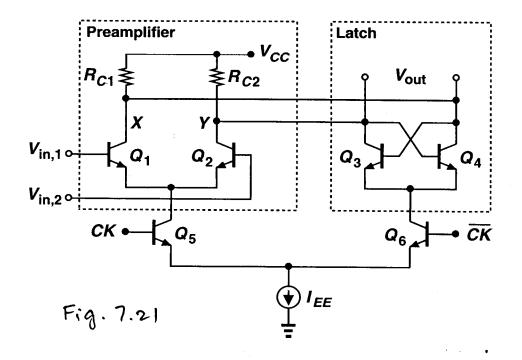

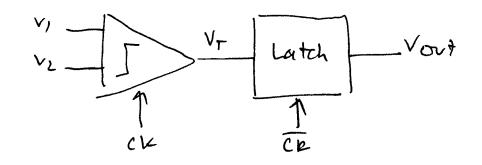

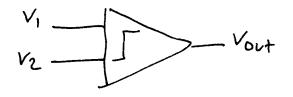

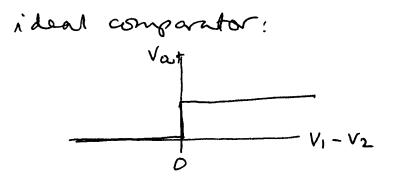

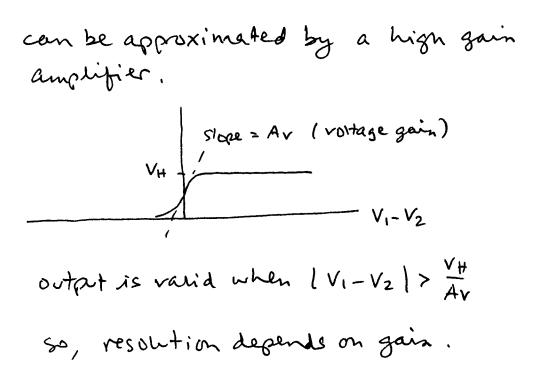

Since linearity isn't needed, use positive feedback in the latch to effectively increase the gain. This also is used to define the sampling instant (like the track-hold)

- Track: Ck = 1 VT tracks input; Latch is disabled

- Latch : CK=0 amp. is disabled; Latch holds present value of VT. Senses polarity.

This works well when VI-V2 is not small, when small we can have metastable case where latch can take a long time (or never) to respond, dynamic error.

Likewise,

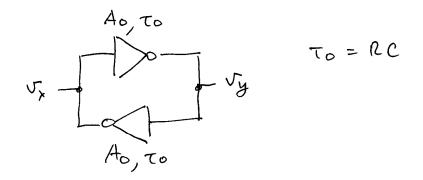

$$N_{\chi} + \tau_0 \frac{dN_{\chi}}{dt} = -A_0 N_{\chi}$$

subtract

$$T_{0} = \frac{d(N_{X} - V_{y})}{At} = -(1 - A_{0})(N_{X} - V_{y})$$

initial condition  $V_{Xy0} = (N_{X} - V_{y})|_{t=0}$

$$V_{X} - V_{y} = V_{Xy0} \exp[(A_{0} - 1)\frac{t}{T_{0}}]$$

growing with time since  $A_{0} \gg 1$

$$B_{0}T = \frac{1}{2}$$

with time constant  $T_{0}/(A_{0} - 1)$

and if  $V_{Xy0}$  is very small, it

will take a long time to reach

valid logic levels.

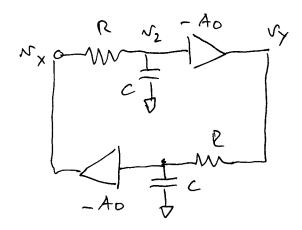

Simple latch model.

represent as single dominant pole for determining transient response.

$\frac{N_{x} - N_{z}}{P} - C \frac{dN_{z}}{dt} = 0$   $-N_{z} - T_{0} \frac{dN_{z}}{dt} = -N_{x}$   $N_{z} = \frac{-N_{y}}{A_{0}}$   $\frac{N_{y}}{A_{0}} + \frac{T_{0}}{A_{0}} \frac{dN_{y}}{dt} = -N_{x}$   $N_{y} + T_{0} \frac{dN_{y}}{dt} = -A_{0} \sqrt{x}$

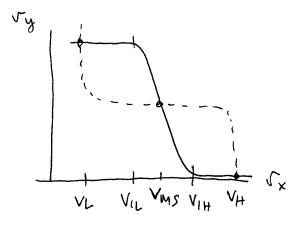

starting at metastable point Vms, we must reach VIH or VIL before logic as fully stable.

How long will this take?

$$T_{I} = \frac{T_{0}}{A_{0}-I} ln\left(\frac{V_{IH}}{V_{XY0}}\right)$$

if Nxyo is very small, this can take a eng time. Then, a sparkle can be produced because a valid logic state has not been obtained yet.

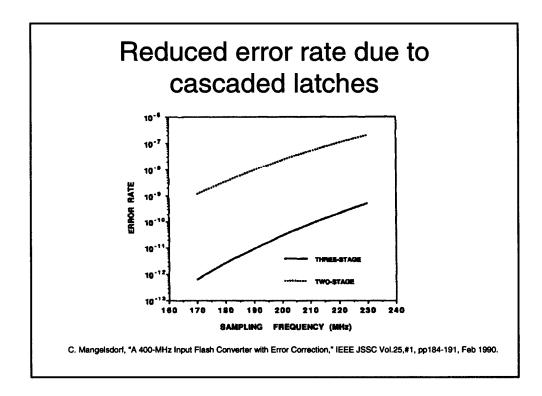

where is the probability? if  $T_c = negeneration time = \frac{1}{2}T$  $P(T_1, T_c) = exp - \frac{(Ao-1)T_c}{T_o}$

in crease AD. de crease To.

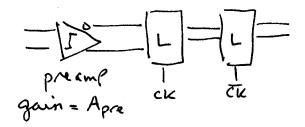

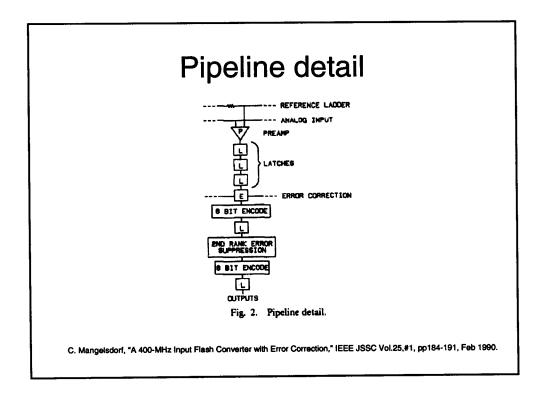

The effective gain in the latch stage can be increased by cascading.

For single latch stage,  $V_0 \cong Apre Vin \exp(\frac{t}{t})$ where  $V_0$ , Vin are usually differential and  $T = \frac{\tau_0}{(A_{0}-1)}$   $t \cong \frac{T}{2}$   $(\frac{1}{2} \text{ period of clock})$ By adding a second latch in cascade, we increase the regeneration time by another hay clock cycle. NOW,  $V_0 \cong Apre Vin \exp(\frac{t}{t}) \exp(\frac{t}{t})$

= Aprevin

$$exp(\frac{t_1+t_2}{z})$$

a third latch stage can also be used to further increase gain at the wet of latency. Ref: C. Mangelsdorf, JSSC, Vol 25, #1, Pp. 184-191, Feb. 1990.

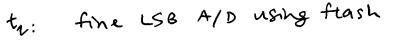

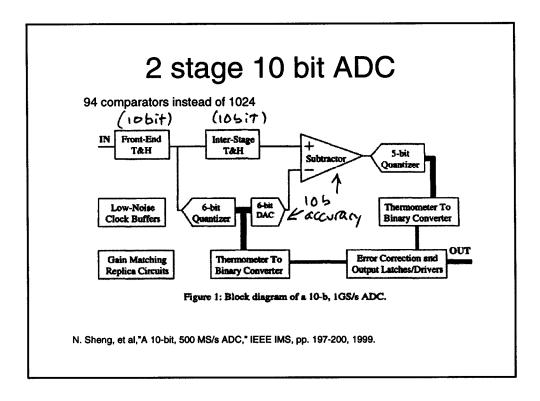

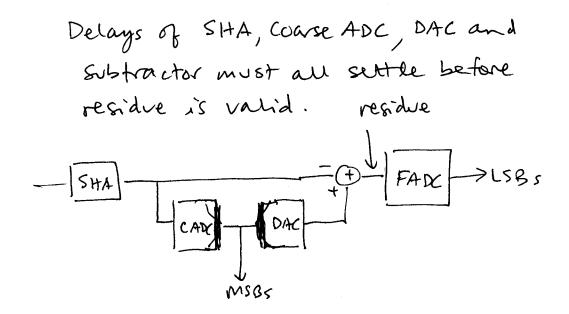

Two-step ADCS

TH is needed because of time delay between t, and DAC settling. Otherwise we have an error AV. This would greatly limit maximum input frequency to were below Nyquist.

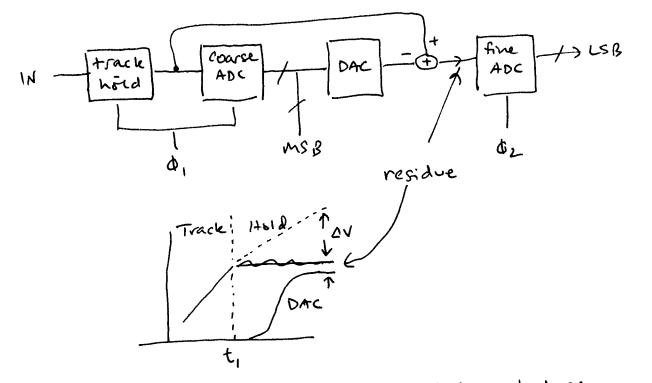

Coarse stage static error carries through since the coarse estimate and the signal are subtracted (analog). So, DNL, INL, offset and gain errors are all deadly.

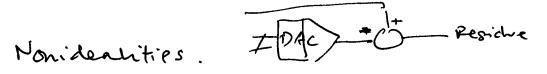

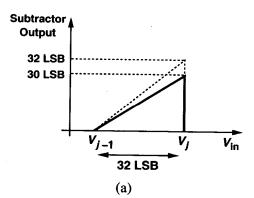

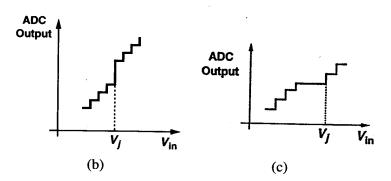

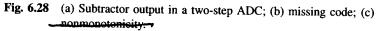

This difference is carred a residue, a plot of this residue over a surept input can reveal the error type:

(Razari)

122

>-Digital Converter Architectures Chap. 6

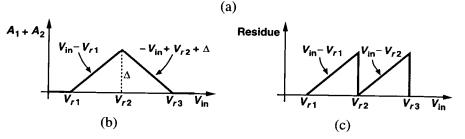

In order to obtain a better view of these effects, the concept of the quantization error plot (Section 6.1) can be generalized to a residue plot wherein the difference between the actual and ideal characteristics is depicted as a function of the input (Figure 6.27). In a residue plot, gain error appears as peaks that follow a nonhorizontal straight line, DNL as shifted transition points, INL as peaks that do not follow a straight line, and offset as a vertical shift [Figure 6.27(b)].

**Fig. 6.27** Residue plot derived from characteristic of Figure 6.26. (a) Ideal; (b) including errors.

If these errors exceed I LSB, you can actually have missing coder because the subtractor output might not reach the full m-bits of the course ADC before it switches to the next course code.

see book for example (p123)

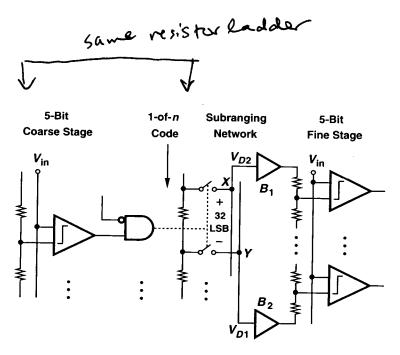

Fig. 6.31 Section of a 10-bit subranging ADC architecture.

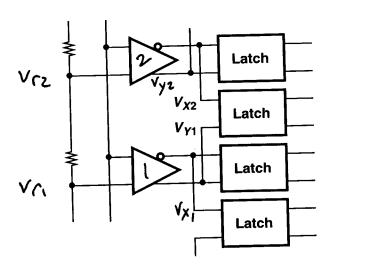

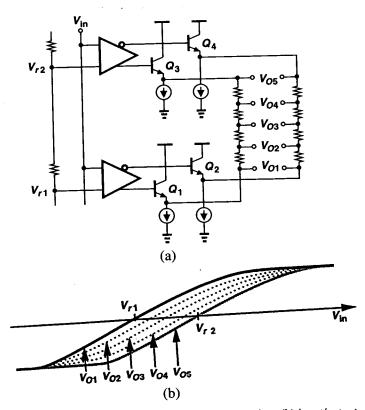

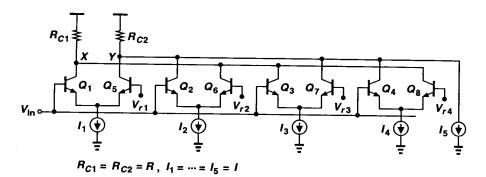

Interpolation. Make use of linearity of concarator preamp to obtain extra resolution while retaining one-stage ADC topology.

How it workes: plot amplifier outputs VXI VXZ VYZ VYI----- VYZ VYI----- VII Vri I Vrz I VM

Note that the relative values of Vx2 and Vy1 exactly represent the difference between Vin and Vm =  $\frac{V_{r1} + V_{r2}}{2}$ . So, we interpolate between two ref. levels Latch senses polarity and gives extra but.

you can increase the degree of interpolation by using a resistor chain to further increase # of bits between two taps of a flach concele.

Fig. 6.36 Higher order interpolation. (a) Implementation; (b) input/output characteristics.

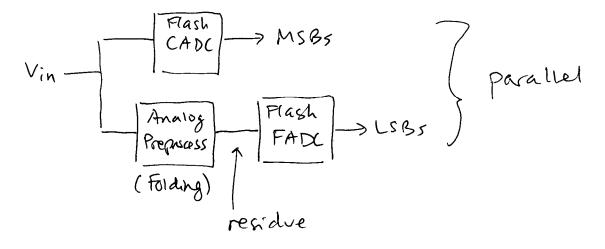

#### Folding ADC Architecture

2 step ADCs split the data conversion into two or more time phases.

Subranging eliminates the DAC and Subtractor but still is a two-step process.

> CADC activates switches to select subrange for FADC.

Folding is an approach which generates the refidue in a one step process.

134 Analog-to-Digital Converter Architectures Chap. 6

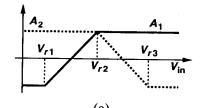

Fig. 6.40 (a) Input/output characteristics of two amplifiers; (b) sum of characteristics in (a); (c) residue in a two-step ADC.

Fig. 6.41 Folding circuit.