#### Behrooz Parhami

Department of Electrical and Computer Engineering University of California, Santa Barbara, USA

parhami@ece.ucsb.edu

#### Outline

- Intro: HW Design and Recursion

- Iterative Refinement (SW & HW)

- Algor/SW/HW Recursion Example

- Example 1: Fast Fourier Transform

- Example 2: Recursive Multipliers

- Example 3: Counting Networks

- Parallel Counters

- Weight-Checkers

- Threshold Counters

- Variations in Counting

- Conclusion and Future Work

## Introduction: Hardware Design

- Time- and work-intensive; expensive; error-prone

- Choice of algorithm, technology, design methodology

- Quick proof-of-concept, followed by fine-tuning

- Fine-tuning adds complexity and thus errors

- In some cases, correctness / reliability more important

- Modularity, packageability, reusability are key attributes

- Ditto for testability, serviceability, availability

- We may opt for simpler designs, older technologies

- $O(\sqrt{n}) \& O(\lg n)$  complexities about the same for small n

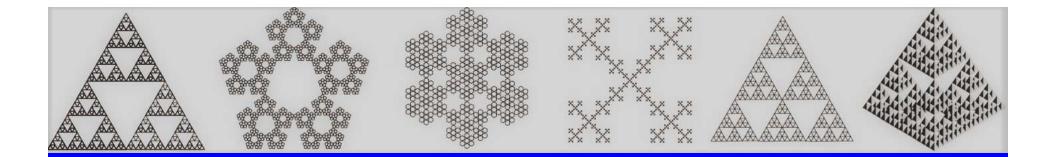

## The Concept of Recursion

To iterate is human, to recurse divine!

#### **Textbook definition:**

Recursion is a method where the solution to a problem depends on solutions to smaller instances of the same problem.

Problem

$$\begin{cases} Base case \\ Subproblem(s) \end{cases}$$

$$n! = \begin{cases} if n \le 1 \text{ then } 1 \\ else n \times (n-1)! \end{cases}$$

$$fib(n) = \begin{cases} \text{if } n \le 2 \text{ then } 1 \\ \text{else } fib(n-1) + fib(n-2) \end{cases}$$

## Recursive Pizzas

## **Iterative Refinement**

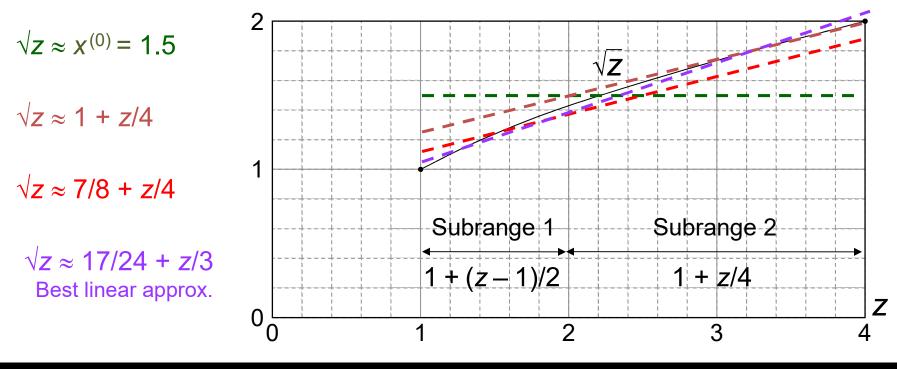

- Compute f(z) by iteratively refining an approximation  $\bullet$

- Example  $x = \sqrt{z}$ :  $x^{(i+1)} = 0.5(x^{(i)} + z/x^{(i)})$

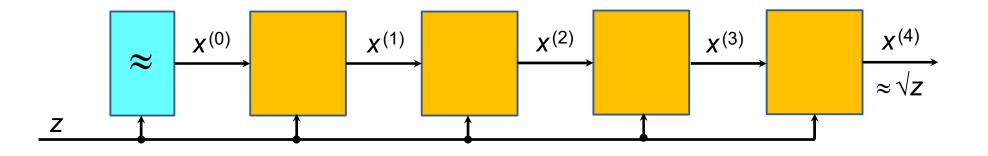

## **Unrolling and Pipelining**

- Compute *f*(*z*) by iteratively refining an approximation

- Example  $x = \sqrt{z}$ :

$$x^{(i+1)} = 0.5(x^{(i)} + z/x^{(i)})$$

- Pipelining: Five different square-rootings in progress

- No unrolling: One orange box, used four times

- Partial unrolling: Two orange boxes, used twice

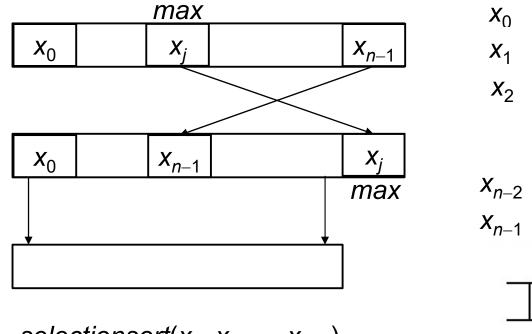

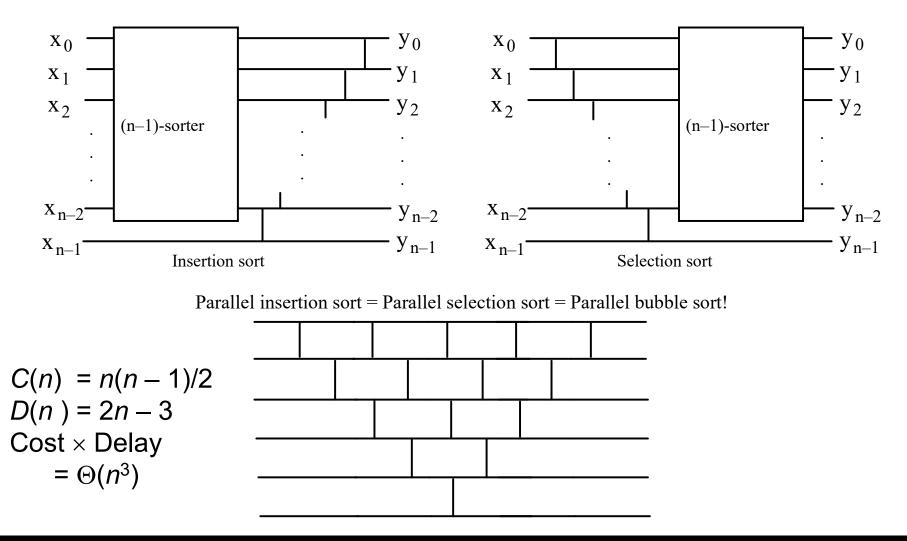

### Algorithm/SW/HW Example: Selection Sort

selectionsort( $x_0, x_1, \dots, x_{n-1}$ ) if n = 1 then exit find  $x_j = max(x_0, x_1, \dots, x_{n-1})$ swap  $x_j$  and  $x_{n-1}$ selectionsort( $x_0, x_1, \dots, x_{n-2}$ )

## **Recursion Drawbacks and Benefits**

- Many procedure calls, with associated overheads

- Overhead not as bad on modern hardware

- Tail-recursion: Recursive call is in last statement

- Unroll the recursion into a loop (smart compiler?)

- Partial unrolling:  $n! = n \times (n-1) \times (n-2) \times (n-3)!$

- May be preferred, even if not the most efficient

- In the case of hardware, the <u>design</u> is recursive

- +

- The circuit-level realization is often fully unrolled

- Recursive design provides analyzability & reliability

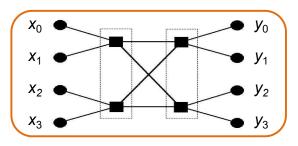

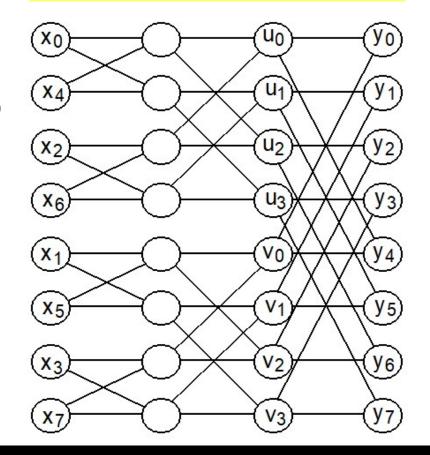

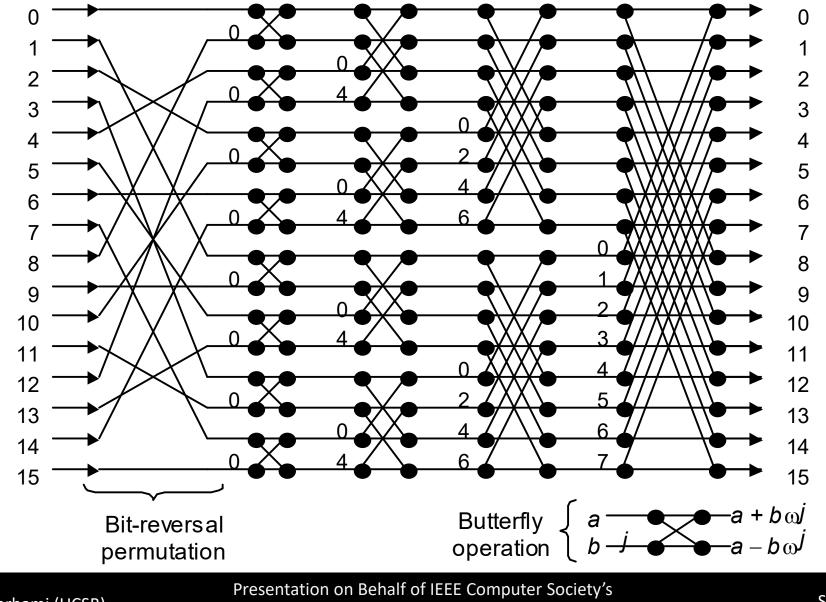

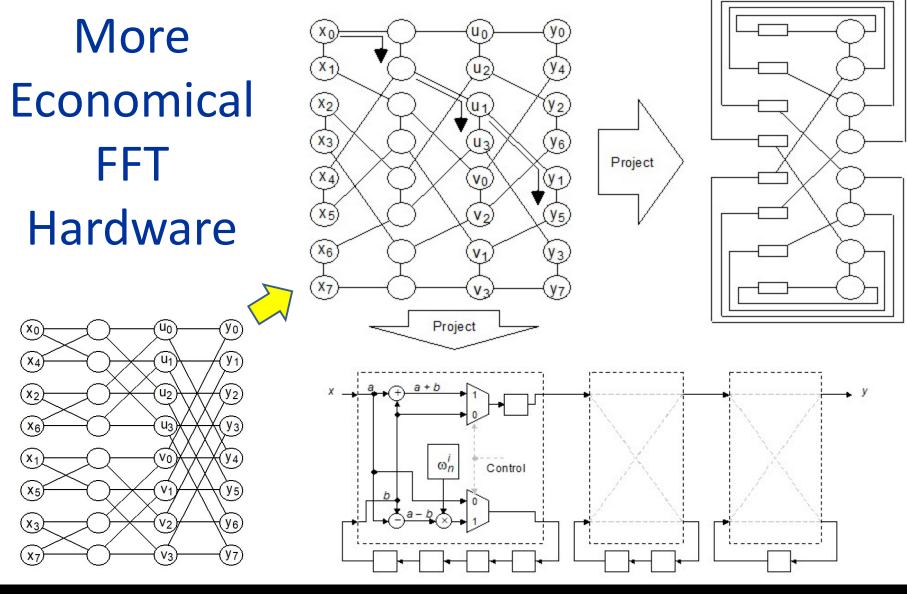

#### Discrete Fourier Transform: FFT Network

DFT:

$$y_i = \sum_{j=0}^{n-1} \omega_n^{ij} x_j$$

Naïve algorithm:  $T(n) = O(n^2)$

FFT:

$$y_i = u_i + \omega_n^i V_i \ (0 \le i < n/2)$$

$y_{i+n/2} = u_i - \omega_n^i V_i$

Seq:

$$T(n) = 2T(n/2) + n = O(n \log n)$$

Par:  $T(n) = T(n/2) + 1 = O(\log n)$

Inverse DFT is almost exactly the same computation:

IDFT:

$$x_i = (1/n) \sum_{j=0}^{n-1} \omega_n^{-ij} y_j$$

*u*: DFT of even-indexed inputs *v*: DFT of odd-indexed inputs

Distinguished Visitors Program

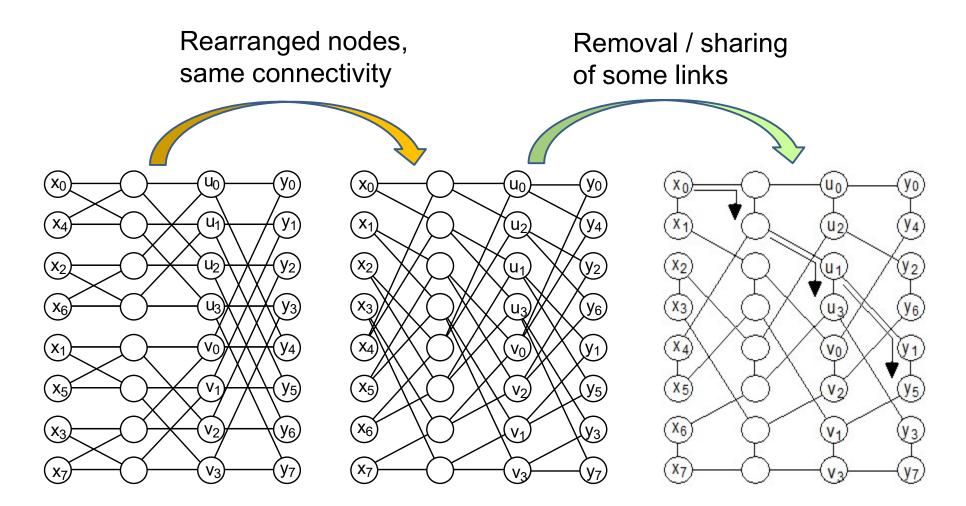

## Regularized Butterfly: Shuffle-Exchange

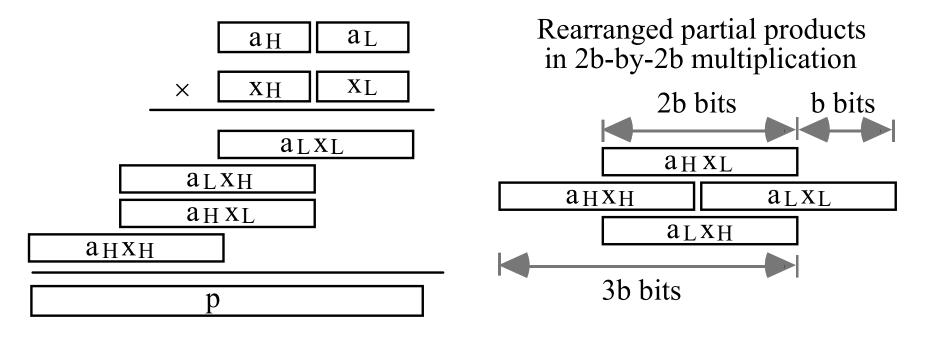

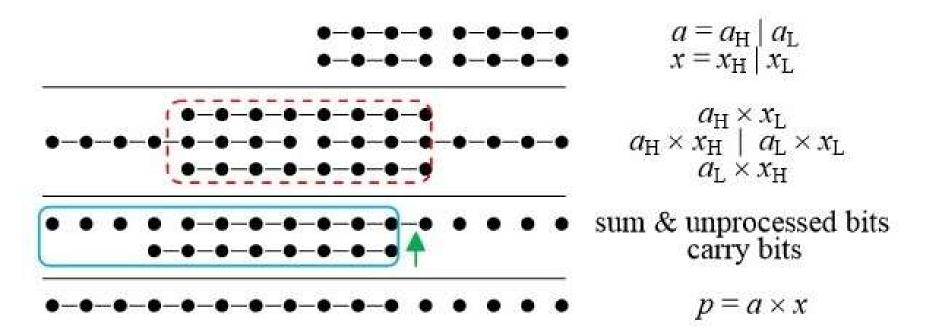

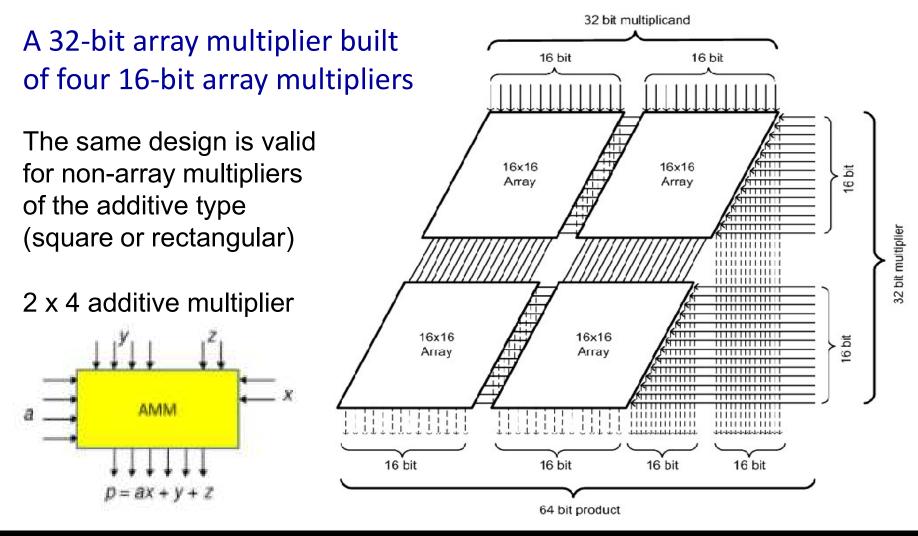

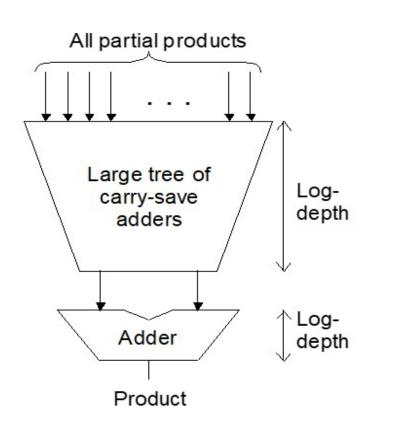

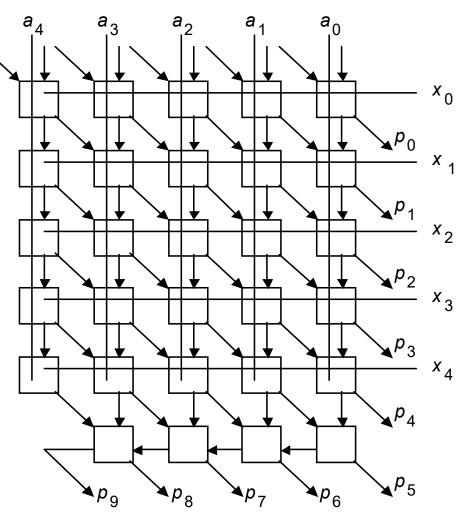

## **Recursive Multipliers: Concept**

Building wide multiplier from narrower ones

Form the 4 half-products Add the resulting 4 (3) numbers Add much faster than multiply

$D(n) = D(n/2) + O(\log n) = O(\log^2 n)$  $C(n) = 4C(n/2) + O(n) = O(n^2)$

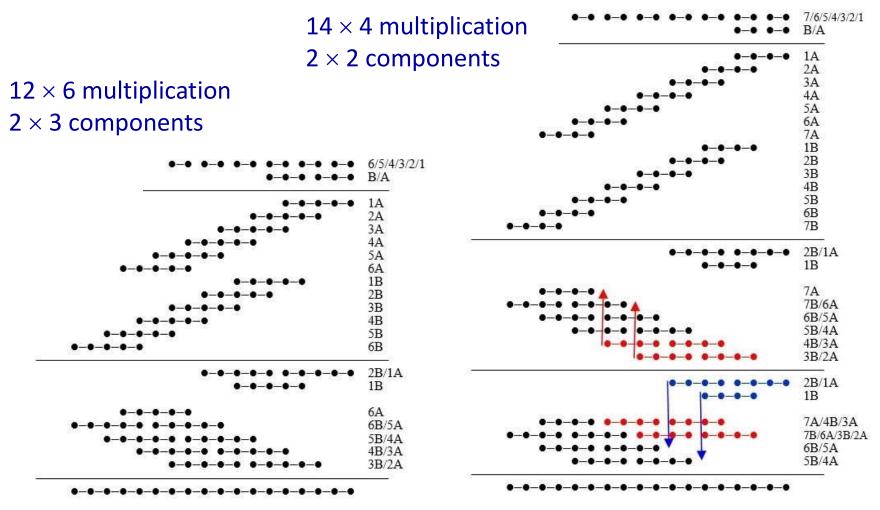

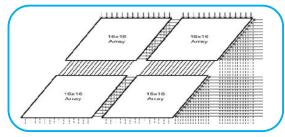

#### **Recursive Multipliers: Example**

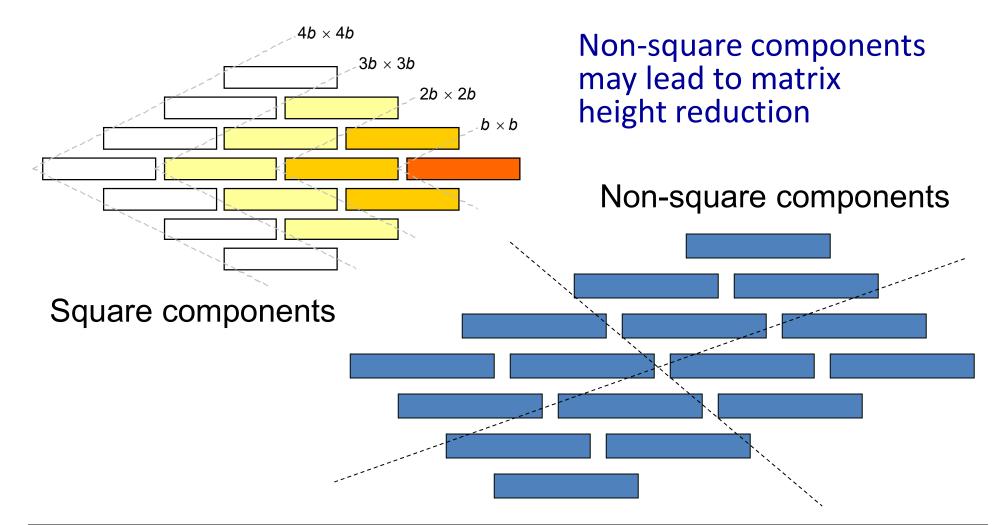

Multipliers can be built recursively from square or non-square component multipliers

An  $8 \times 8$  multiplier built from  $4 \times 4$  component multipliers

#### **Recursive Multipliers: Circuit**

#### **Karatsuba Multiplication**

$2b \times 2b$  multiplication requires four  $b \times b$  multiplications:

$(2^{b}a_{H} + a_{L}) \times (2^{b}x_{H} + x_{L}) = 2^{2b}a_{H}x_{H} + 2^{b}(a_{H}x_{L} + a_{L}x_{H}) + a_{L}x_{L}$

Karatsuba noted that one of the four multiplications can be removed at the expense of a few extra additions:

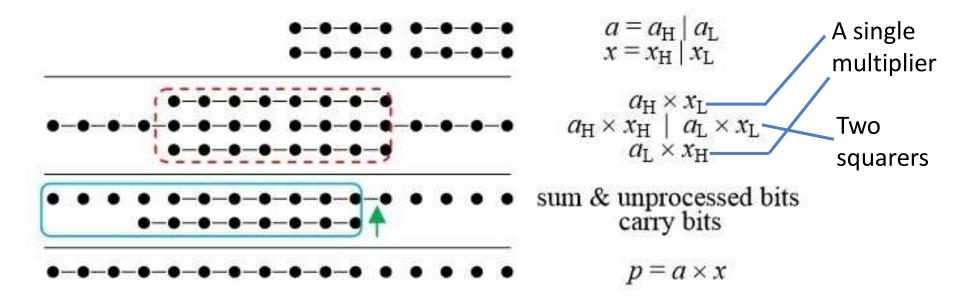

### **Special Case of Squaring**

Non-square building blocks not beneficial for squarers because we won't be able to use squarers

An  $8 \times 8$  squarer built from  $4 \times 4$  component multipliers/squarers

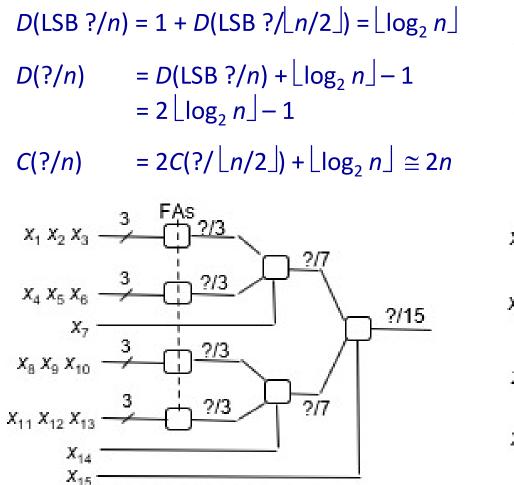

## **Counting Networks**

- Circuits that compute (symmetric) logic functions based on the number of 1s among the inputs

- ?/n How many 1s are there? (Parallel counters)

- =k/n Are there exactly k 1s?

- $\geq l/n$  Are there at least l 1s?

- < m/n Are there fewer than m 1s? (or  $\le (m-1)/n$ )

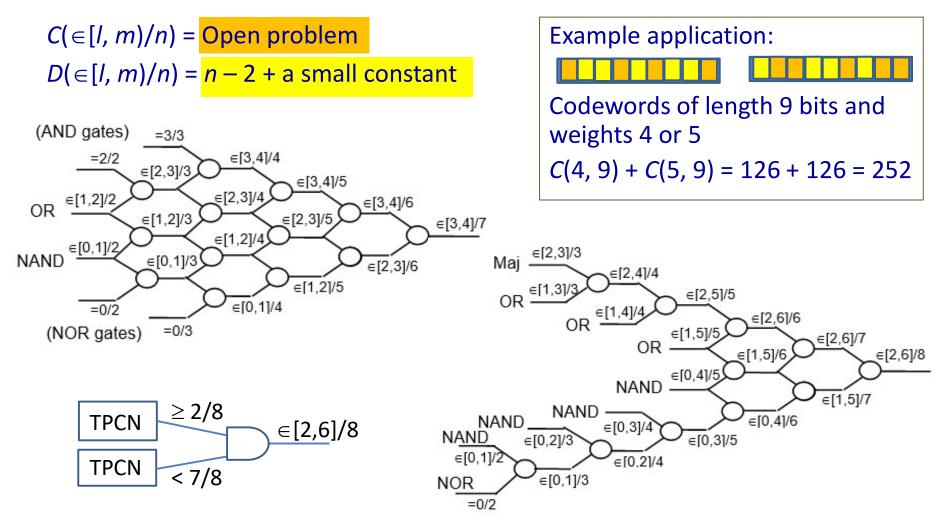

- $\in [l,m)/n$  Are there at least l and fewer than m 1s?

- $\in [l, m-1]/n$  Are there at least l and at most m-1 1s?

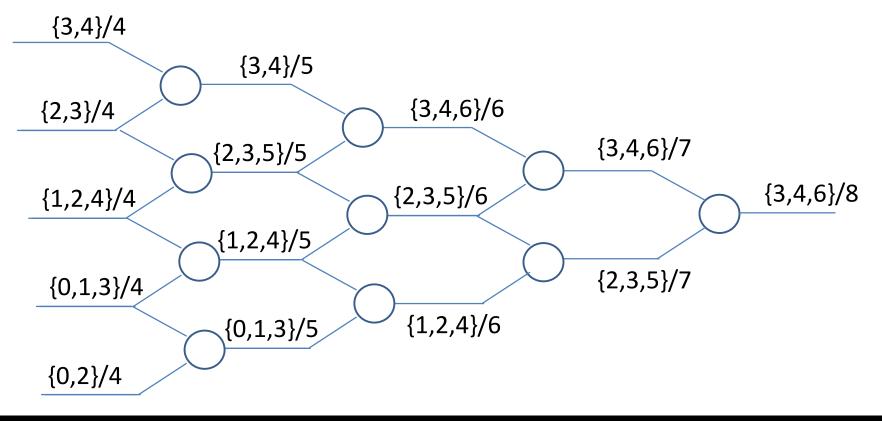

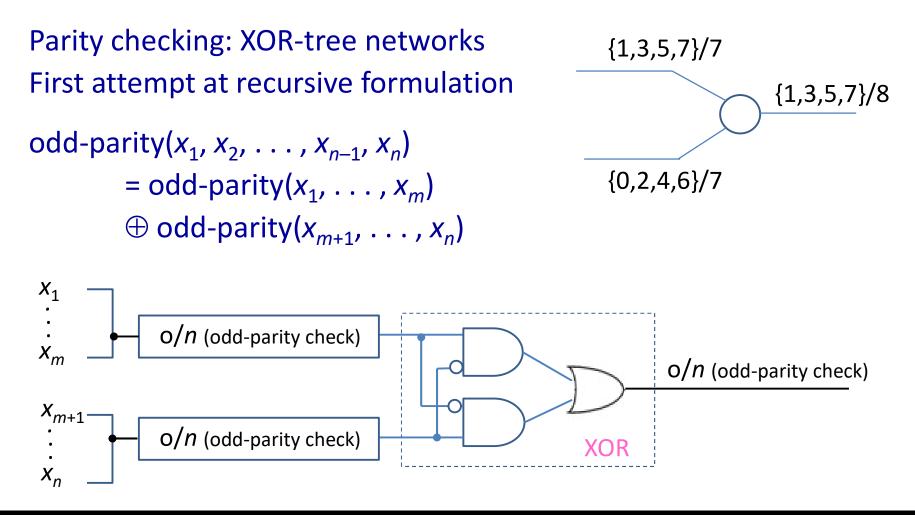

- $\{j_1, j_2, ..., j_k\}/n$  Is the number of 1s in the set  $\{j_1, j_2, ..., j_k\}$ ?

- Also, Hamming-weight-comparators, not discussed here

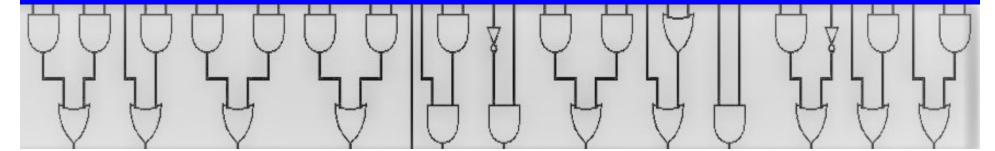

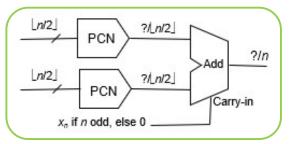

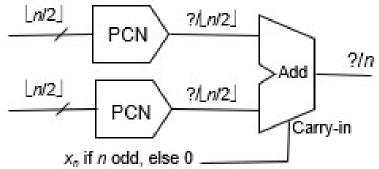

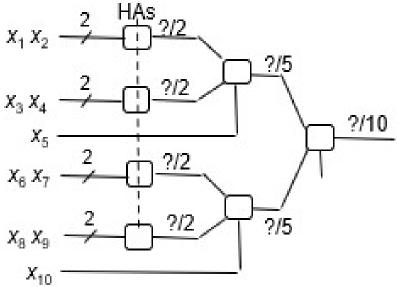

#### **Recursive Design of Parallel Counters**

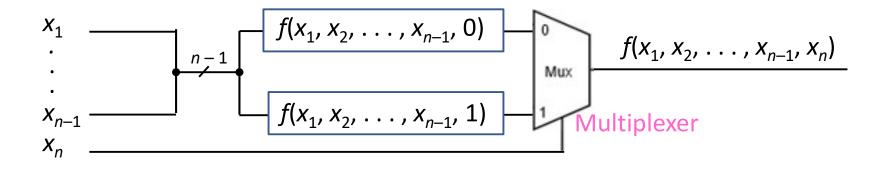

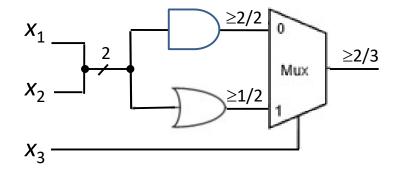

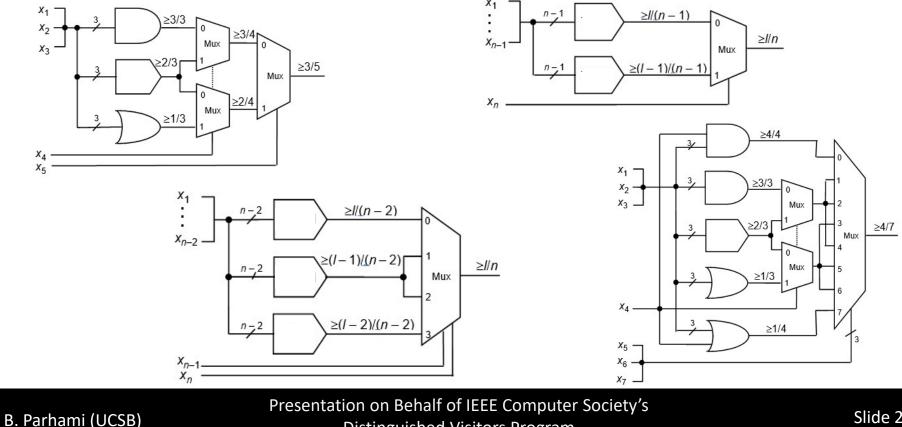

### **Mux-Based Hardware Realizations**

Shannon expansion or decomposition

$f(x_1, x_2, \ldots, x_{n-1}, x_n) = x_n' f(x_1, x_2, \ldots, x_{n-1}, 0) \vee x_n f(x_1, x_2, \ldots, x_{n-1}, 1)$

Example: Majority voter  $f(x_1, x_2, x_3) = x_1 x_2 \lor x_2 x_3 \lor x_3 x_1$  $= x_3'(x_1 x_2) \lor x_3(x_1 \lor x_2)$

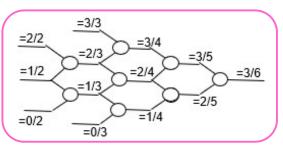

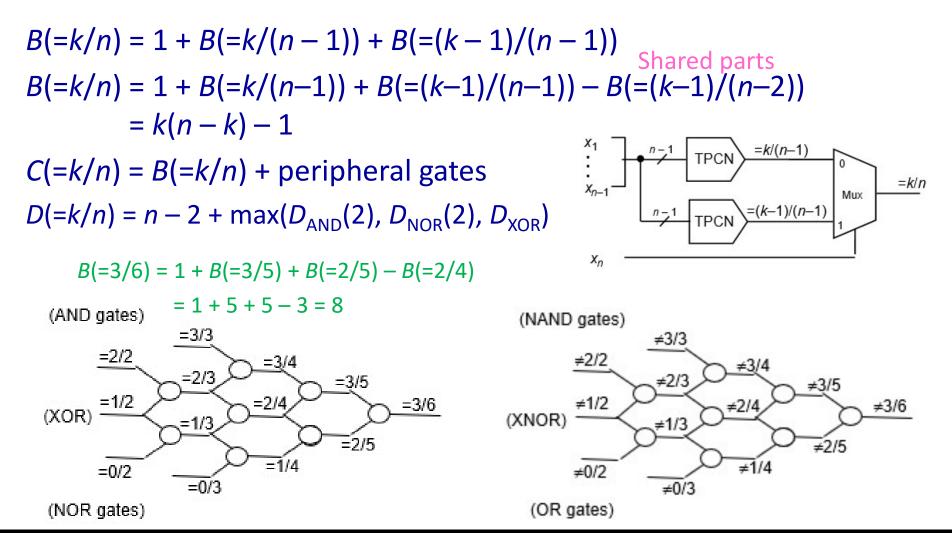

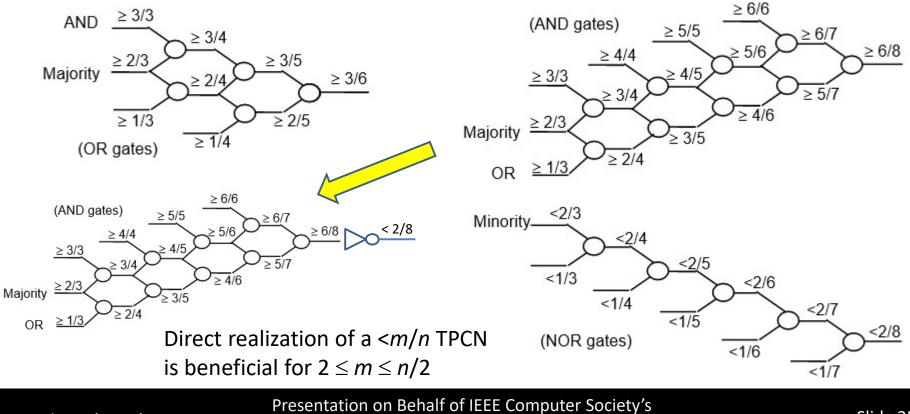

#### **Recursive Design of Weight-Checkers**

B. Parhami (UCSB)

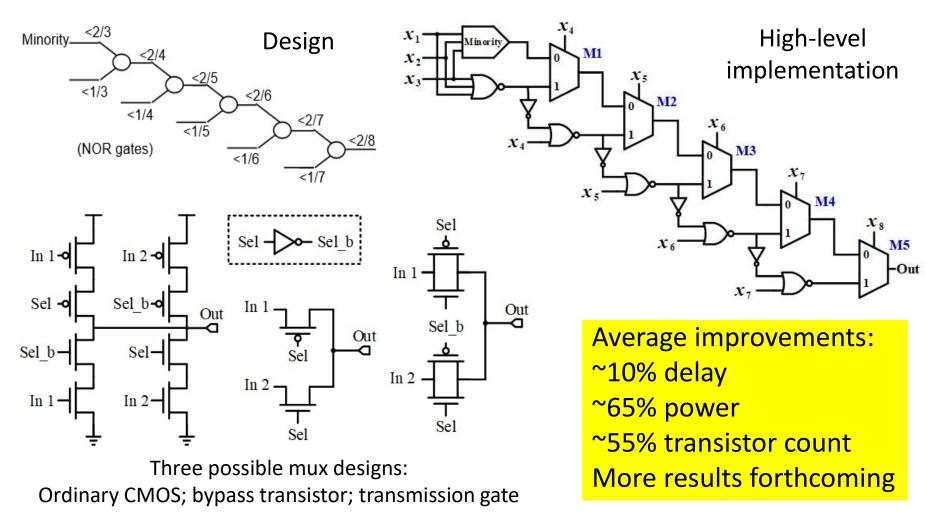

#### **Recursive Design of Threshold Counters**

$B(\geq l/n) = 1 + B(\geq l/(n-1)) + B(\geq (l-1)/(n-1)) - B(\geq (k-1)/(n-1)) = (n-l)(l-1) - 1$  $C(\geq k/n) = B(\geq k/n) + peripheral gates$

$D(\geq l/n) = 1 + \max[D(\geq l/(n-1)), D(\geq (l-1)/(n-1))] = n-3 + \text{small constant}$

Example (Inverse) Threshold Counters  $B(\ge l/n) = 1 + B(\ge l/(n-1)) + B(\ge (l-1)/(n-1)) - B(\ge (k-1)/(n-1)) = (n-l)(l-1) - 1$  $C(\ge k/n) = B(\ge k/n) + peripheral gates$

$D(\geq l/n) = 1 + \max[D(\geq l/(n-1)), D(\geq (l-1)/(n-1))] = \frac{n-3}{n-3} + \text{small constant}$

Distinguished Visitors Program

## **Example CMOS Implementation**

#### **Between-Limits Threshold Counters**

Presentation on Behalf of IEEE Computer Society's Distinguished Visitors Program

B. Parhami (UCSB)

## **Membership Checkers**

{3,4,6}/8 membership checker

Negative terms and terms larger than *n* are dropped

## **Even- or Odd-Parity Checker**

#### Advantages and Drawbacks

- Recursion not applicable to all of our needs

- May not lead to theoretically-optimal design

- But ... Optimal designs tend to be complex

→ Long design times and many design errors

- Recursive designs: Analyzable and verifiable

- Stop recursion upon hitting a known design

- Commonly-used parts can be fully optimized

- Good for prototyping, if not for final circuit

#### Speed vs. Regularity

- Tree: Fast, but irregular

- Array: Slow, but regular

#### **Conclusion and Future Work**

- Recursive hardware design is feasible and beneficial

- I covered three examples: FFT; Multiplier; Counter

- Counting-network designs are new

- There are other examples: e.g., sorting networks

- Benefits: Ease of analysis and correctness proof

- May be preferred, even if not the most efficient

- All designs can be pipelined for higher throughput

- Latency, cost, power for implemented networks

## Questions?

parhami@ece.ucsb.edu PDF files of B. Parhami's publications are available at: www.ece.ucsb.edu/~parhami/publications.htm

B. Parhami (UCSB)

Presentation on Behalf of IEEE Computer Society's Distinguished Visitors Program

Slide 33

# Back-up Slides

parhami@ece.ucsb.edu www.ece.ucsb.edu/~parhami

B. Parhami (UCSB)

Presentation on Behalf of IEEE Computer Society's Distinguished Visitors Program

Slide 34

#### **Insertion Sort and Selection Sort**

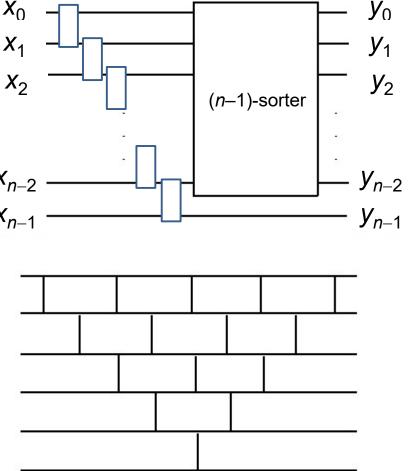

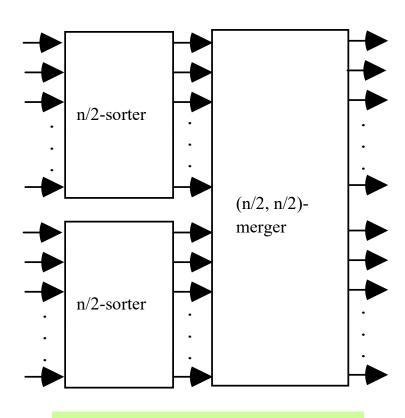

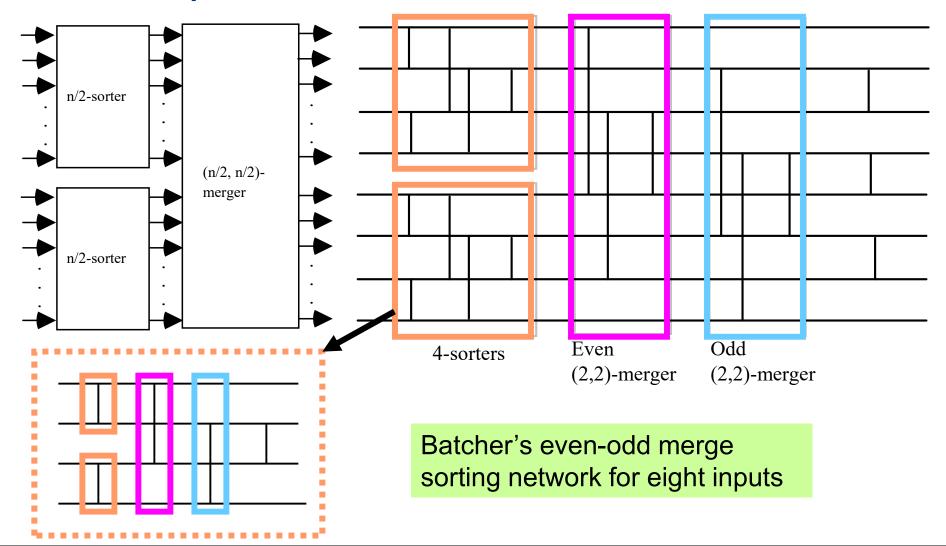

## Batcher's Even-Odd Merge Sorting

The recursive structure of Batcher's even-odd merge sorting network. Batcher's (m, m) even-odd merger, for *m* a power of 2:

$$C(m) = 2C(m/2) + m - 1$$

= (m-1) + 2(m/2-1) + 4(m/4-1) + . . .

= m log<sub>2</sub>m + 1

$$D(m) = D(m/2) + 1 = \log_2 m + 1$$

$\operatorname{Cost} \times \operatorname{Delay} = \Theta(m \log^2 m)$

Batcher sorting networks based on the even-odd merge technique:

$$C(n) = 2C(n/2) + (n/2)(\log_2(n/2)) + 1$$

$$\cong n(\log_2 n)^2/2$$

$$D(n) = D(n/2) + \log_2(n/2) + 1$$

$$= D(n/2) + \log_2 n$$

$$= \log_2 n (\log_2 n + 1)/2$$

$Cost \times Delay = \Theta(n \log^4 n)$

#### Example Batcher's Even-Odd 8-Sorter

Presentation on Behalf of IEEE Computer Society's Distinguished Visitors Program

B. Parhami (UCSB)

#### (Non-)Square Recursive Multipliers

### **Example with No Height Reduction**

| $12 \times 8$ multiplication<br>$3 \times 4$ components | 0-0-0 0-0-0 0-0-0 0-0-0<br>0-0-0-0 0-0-0-0 | 4/3/2/1<br>B/A |

|---------------------------------------------------------|--------------------------------------------|----------------|

| 2                                                       |                                            | 1A             |

|                                                         | 0-0-0-0-0-0                                | 2A             |

|                                                         | 0-0-0-0-0-0                                | 3A             |

| 0-0-0-0-0-0                                             |                                            | 4A             |

|                                                         | 0-0-0-0-0-0                                | 1B             |

|                                                         |                                            | 2 <b>B</b>     |

| 0-0-0-0                                                 |                                            | 3B             |

| 0-0-0-0-0-0                                             |                                            | 4B             |

|                                                         |                                            | 2B/1A          |

|                                                         | 0-0-0-0-0-0                                | 1B             |

| 0-0-0-0-0-0                                             |                                            | 4A             |

| 0-0-0-0-0 0-0-0-0-0-0                                   |                                            | 4B/3A          |

| 0-0-0-0                                                 |                                            | 3B/2A          |

| 0-0-0-0-0-0                                             |                                            |                |

#### **Examples of Matrix Height Reduction**