# 3-D Memristor Crossbars for Analog and Neuromorphic Computing Applications

Gina C. Adam, Brian D. Hoskins, Mirko Prezioso, Farnood Merrikh-Bayat, Bhaswar Chakrabarti, and Dmitri B. Strukov, *Member, IEEE*

Abstract—We report a monolithically integrated 3-D metal-oxide memristor crossbar circuit suitable for analog, and in particular, neuromorphic computing applications. The demonstrated crossbar is based on Pt/Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2-x</sub>/TiN/Pt memristors and consists of a stack of two passive 10  $\times$  10 crossbars with shared middle electrodes. The fabrication process has a low, less than 175 °C, temperature budget and includes a planarization step performed before the deposition of the second crossbar layer. These features greatly improve yield and uniformity of the crosspoint devices and allows for utilizing such a fabrication process for integration with CMOS circuits as well as for stacking of multiple crossbar layers. Furthermore, the integrated crosspoint memristors are optimized for analog computing applications allowing successful forming and switching of all 200 devices in the demonstrated crossbar circuit, and, most importantly, precise tuning of the devices' conductance values within the dynamic range of operation. We believe that the demonstrated work is an important milestone toward the implementation of analog artificial neural networks, specifically, those based on 3-D CMOL circuits.

Index Terms—3-D integrated circuits, analog processing circuits, memristors, nonvolatile memory.

# I. INTRODUCTION

UE to excellent scalability, compatibility with conventional semiconductor fabrication technology, and fast write and read speed combined with long retention, metal-oxide resistive switching devices [1] (also called metal-oxide memristors [2] or ReRAM [3]) are very promising emerging components for a variety of memory and computing

Manuscript received July 12, 2016; revised October 12, 2016; accepted November 11, 2016. Date of publication December 1, 2016; date of current version December 24, 2016. This work was supported in part by the AFOSR under MURI under Grant FA9550-12-1-0038, in part by DARPA through BAE Systems under Contract HR0011-13-C-0051UPSIDE, and in part by the Department of State under the International Fulbright Science and Technology Award. The review of this paper was arranged by Editor U. E. Avci.

G. C. Adam was with the Department of Electrical and Computer Engineering, University of California Santa Barbara, CA 93106 USA. She is now with the National Institute for Research and Development in Microtechnologies, 077190 Bucharest, Romania (e-mail: gina\_adam@engineering.ucsb.edu).

B. D. Hoskins is with the Materials Department, University of California at Santa Barbara, Santa Barbara, CA 93106 USA.

M. Prezioso, F. Merrikh-Bayat, B. Chakrabarti, and D. B. Strukov are with the Department of Electrical and Computer Engineering, University of California at Santa Barbara, Santa Barbara, CA 93106 USA (e-mail: strukov@ece.ucsb.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2016.2630925

applications [4], [5]. Successful demonstrations of digital memory and logic applications based on metal-oxide ReRAM are abundant in the literature [6]-[14]. However, one of the most exciting applications of such devices could be in neuromorphic computing [15]-[20] due to the potential for tuning the memory state, i.e., device conductance, with very high (<1%) precision [21]. Because of an ionic memory mechanism, analog memory functionality is sustained upon aggressive scaling [22], [23] making such devices ideal candidates for the implementation of artificial synapses, the most numerous elements of artificial neural networks [15], [24]. The potentially high integration density for artificial synapses and their tight integration with other elements of the circuit would eliminate costly OFF-chip communications and is crucial for low-energy operation of memristor-based artificial neural networks. An example of such a circuit is the CMOL (Cmos + MOLecular) [4]–[6], [15] concept, in which the CMOS subsystem implements neurons' soma functionality, while back-end-of-line-integrated passive memristive crossbar circuits with analog tuning capability mimic synapses' functionality and routing among neurons.

In 3-D CMOL, [25] the most advanced version of CMOL circuits, multiple crossbar layers are utilized to further increase the effective density of synapses and connectivity among neurons. Obviously, monolithic integration of multiple crossbar layers comes with additional fabrication challenges, while the analog tuning requirement enforces tighter margins on the permissible variations in the memristors. Though there have already been demonstrations of multilayer crossbar circuits, the primary target applications were digital memories [7], [9]–[13], [26]–[28] and typically, only very limited characterization statistics were reported. Statistics about the device behavior across the entire crossbar are needed to understand if the system shows the tight switching variations needed to successfully implement neuromorphic networks. The sidewall-integrated vertical memristive architecture allows for cost-effective multilevel functionality, but it has only been shown so far in small linear arrays [29], [30] not crossbars. Moreover, such an approach is not suitable for CMOL circuit integration and may not be readily scalable to large numbers of layers because of the required high aspect ratios during deposition [31] or even due to the low current drivability of the vertical selector [32].

A particular challenge for 3-D circuits is the presence of thermal effects that can play an important role during the fabrication and operation of multilayer systems [33], [34].

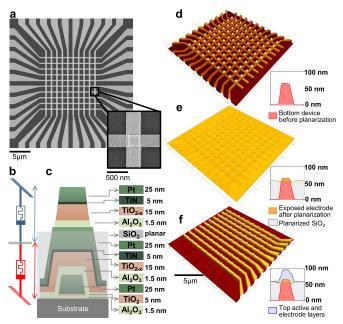

Fig. 1. Fabrication details. (a) Scanning electron microscopy top-view image of the fabricated circuit with a zoom on a stacked device to highlight the clean electrode edges. (b) Equivalent circuit for two memristors in the stacked configuration, in particular, highlighting that the middle electrode (gray) is shared between bottom (red) and top (blue) devices. (c) Cartoon of device's cross section showing the material layers and their corresponding thicknesses. AFM images and step heights of the crossbar devices during different stages of fabrication, in particular, showing (d) bottom crossbar, (e) planarization to reduce step height, and (f) top crossbar.

A low temperature budget is needed during fabrication in order to preserve the material properties of the already fabricated layers. The use of high temperatures during deposition or photoresist baking can lead to interlayer diffusion and decrease the control over the dopant concentration and nonstoichiometry. Additionally, the switching mechanism for the most practical metal-oxide memristors involves significant Joule heating. Maximum temperatures during the switching might be fairly high, exceeding 700 K [35]. This can cause disturbances in the state of a vertical neighbor if such devices are separated by a thin middle electrode from the device in question. A recent theoretical work [36] suggested that the thermal crosstalk in 3-D ReRAM stacks can deteriorate device performance and produce failures—a problem particularly severe during the power intensive reset step.

This paper reports the first 3-D monolithic back-end-of-line integration of two  $TiO_{2-x}$ -based passive crossbars for analog computing applications, which we believe is an important step toward energy-efficient neuromorphic circuits, in particular 3-D CMOL networks [15].

## II. FABRICATION AND CHARACTERIZATION

Two memristive crossbar circuits were monolithically integrated in a conventional configuration, with middle lines shared between the bottom and top crossbar circuits (Fig. 1). (This is in contrast to the recently demonstrated sidewall vertical integration approach [30]–[32].) Devices were fabricated on a Si wafer coated with 200-nm thermal SiO<sub>2</sub> and had  $\sim\!\!350$  nm  $\times$  350 nm feature sizes. Circuit fabr

rication involved four lithography steps using an ASML S500/300 DUV stepper with a 248-nm laser. A stack of nondevelopable antireflective coating (DUV-42P-6 from Brewer Science, spin speed 2500 rpm, bake 175 °C, thickness  $\sim$ 60 nm) and positive photoresist (UV210-0.3 from Dow, spin speed 2500 rpm, bake 135 °C, thickness ~300 nm) together with the AZ300MIF developer from Clariant was used for patterning. An O<sub>2</sub>-based plasma (100 W, 300-mTorr pressure for 75 s) was then used to etch the nondevelopable antireflective coating and to clean any organic residue. An AJA ATC 2000-F sputter system with Ti, Al, and Pt targets and Ar,  $O_2$ , and  $N_2$  gases was used to deposit in blanket the material stacks for the: 1) the bottom electrodes; 2) bottom active layer and middle electrodes; and 3) top active layer and top electrodes. TiO<sub>2-x</sub> with nonstoichiometry precisely controlled during the reactive dc sputtering deposition was used as an active layer for both crossbar circuits due to its excellent analog switching properties. The Al<sub>2</sub>O<sub>3</sub> barrier layer, the  $TiO_{2-x}$  active layer, and the TiN and Pt layers together with an Al<sub>2</sub>O<sub>3</sub> hard mask layer (~25 nm) were deposited in situ without breaking the vacuum and then patterned using an Ar ion beam etching (IBE) in an Oxford Flexal system at 30-mA source current. The active layers have similar properties, since they were deposited in the same chamber conditions a few hours apart [Fig. 1(c)].

The particular reason for using Ar IBE for patterning the metal layers is that the structures with clean edges are crucial for multilayer stacking. "Rabbit ear" and other formations can easily appear during lift-off processes of sputtered films due to side-wall redeposition and they pose the risk of electrical shorts. In comparison with the previously used lift-off techniques [20], [37], [38], the IBE has the advantage of allowing *in situ* deposition of the stack and provide clean metal electrodes.

To control the shape of the electrode, we investigated three different Ar ion beam incident angles. Etching with no tilt (beam angle  $0^{\circ}$ ) created an electrode with a  $40.2^{\circ}$  slope. When tilt was used, the electrode slope decreased to  $-22.8^{\circ}$  for partial tilt (i.e., with no tilt initially and then milling at a  $40^{\circ}$  angle) and to  $12.8^{\circ}$  for purely tilted ( $40^{\circ}$  angle). Partially tilted conditions were chosen, since they provided lower electrode slope while preserving the feature sizes. After IBE, the remaining traces of  $Al_2O_3$  hard mask were removed in AZ300MIF developer, and the sample was cleaned thoroughly in solvents.

The top stack of active layer and metal was deposited only after a planarization step in order to minimize the risks of shorts and large variations due to the high step height,  $\sim$ 69 nm on average [Fig. 1(d)–(f)]. The first step in the planarization process was to deposit  $\sim$ 750 nm of SiO<sub>2</sub> in an advanced vacuum plasma-enhanced CVD Vision 310 system from Veeco at a temperature of 175 °C using 600 sccm of SiH<sub>4</sub> as precursor and 1640 sccm of  $O_2$ . This SiO<sub>2</sub> layer was used with a dual purpose: as the sacrificial layer for planarization and as an isolation layer between the devices. In the second step, fast chemical mechanical polishing (CMP) using a Logitech Orbis system was used to achieve global planarization. The developed recipe (platen rotation 80 rpm

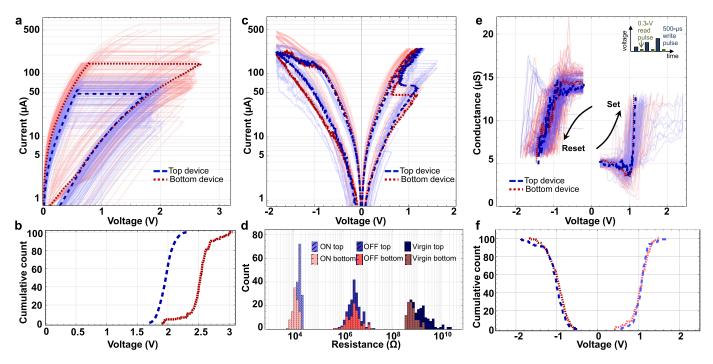

Fig. 2. Forming, switching, and tuning characteristics. (a) I-V curves for forming process for all devices with two representative curves being highlighted for comparison. Red dotted line: bottom device. Blue dashed line: top device. (b) Cumulative histogram counts of forming voltages, which are defined as the sum of all previous counts up to the current forming voltage. (c) I-Vs for all 2 x 10 x 10 devices with two representative curves being highlighted for comparison. (Red dotted line: bottom device. Blue dashed line: top device.) obtained by applying quasi-dc current ramp 300  $\mu$ A and reset voltage of -1.8 V. (d) Cumulative histogram for the devices' on- and off-state conductances, measured at 0.3 V, when using quasi-dc current ramp with 300  $\mu$ A for set and quasi-dc voltage ramp with -2.4 V for reset transition. (e) Device conductance evolution, measured at 0.3 V, under applied write voltage ramps of opposite polarities. (f) Cumulative counts for the effective threshold voltages for set and reset transition for both bottom (red dotted line) and top crossbars (blue dashed line). All the devices in both layers were characterized. The average threshold set voltages for bottom and top layer were 1.04 and 1.06 V, respectively, with a corresponding standard deviations of 0.2 and 0.17 V. For the threshold reset voltage, the averages for bottom and top layer were -0.98 and -1.04 V, respectively, with a corresponding standard deviations of 0.22 and 0.25 V.

and slurry rate 50 sccm) etched ~450 nm of SiO<sub>2</sub> in 2 min and provided a planar surface with a good uniformity across the 4-in wafer. The middle electrode was partially exposed in a controlled fashion using dry etch and atomic force microscope (AFM) as explained further. We used short dryetching steps in a CHF3 atmosphere in a Panasonic E626I inductively coupled plasma chamber to remove the remaining SiO<sub>2</sub>. AFM imaging with a Bruker ICON AFM in the tapping mode was used to test after each etching step if the middle electrode was exposed so that no extra etching steps would be required. This planarization technique had  $\sim$ 74% yield across the wafer, as 74 out of 100 crossbar dies had the middle electrode properly exposed and the remaining dies had the middle electrode still covered with SiO2 due to CMP nonuniformities. The step of the exposed middle electrode varied slightly from die to die, with an average of 11.8 nm and a maximum of 24 nm. The top device layers were deposited using reactive sputtering and patterned with DUV lithography and Ar IBE similarly to the bottom ones. The top electrode was patterned a few nanometers wider, to ensure complete coverage of the exposed middle electrode. Finally, the pads of the bottom and middle electrodes were exposed through a CHF3 etch of the sacrificial SiO2, which was used for planarization. The photoresist was then stripped in the 1165 solvent (from Shipley Microposit) for 24 h at 80 °C. To facilitate the wireboding, the pads of the bottom and middle electrodes were filled with 15 nm of Cr and 450 nm of Au

deposited using a four pocket electron beam evaporator from Sharon Vacuum Co.

All the electrical characterizations were performed at room temperature using an Agilent B1500A Semiconductor Device Parameter Analyzer and an Agilent B1530A Waveform Generator/Fast Measurement Unit together with a low-leakage Agilent E5250A Switch Matrix. The crossbar was wirebonded and mounted on a custom made board connected to the Agilent measurement tools. The setup was controlled through a computer via General Purpose Interface Bus (GPIB) and custom Visual C++ code. Three different modes of operation were utilized for crossbar circuit testing and characterization [39]. A "ground configuration" was used for a state read at 0.3 V, a "floating configuration" was used for forming and I-V sweeps, and finally, a "V/2-biasing configuration" was used for state tuning.

### III. RESULTS

Both bottom and top crossbar layers have similar electrical behavior and satisfactory device-to-device uniformity. In particular, the virgin (preforming) devices have an average conductivity and standard deviation, respectively, of 1.7 and 0.62 nS for the bottom crossbar and 0.56 and 0.38 nS for the top one [Fig. 2(d)]. The bottom crossbar has a slightly higher conductivity despite the fact that the bottom and top active layers were deposited in the same chamber conditions. A likely reason for this slight difference is the sample heating in an  $O_2$

atmosphere at 175 °C during the sacrificial SiO<sub>2</sub> deposition, which might have caused minor stoichiometry or crystallinity shifts in the bottom active layer.

All  $10 \times 10$  devices in both layers were successfully formed [Fig. 2(a) and (b)]. The forming was done sequentially by applying quasi-dc current ramps with a 3 V compliance provided by the measurement tool to the selected column, first for the bottom devices and then for the top ones. Immediately after successful forming, the device was turned OFF using a quasi-dc voltage of -2.4 V. The average forming voltage was  $\sim 2.5$  V for the bottom devices and  $\sim 2$  V for the top ones. The difference is probably due to the different virgin conductances as explained above. Initially, devices were formed at  $\sim 10-50~\mu\text{A}$ , though the forming current increased to  $\sim 100-700~\mu\text{A}$  as more devices were getting formed due to the increased leakage. The thermal crosstalk was negligible during the forming process with the devices adjacent to the device being formed maintaining their virgin or OFF state.

The bottom and top devices have similar electrical characteristics as shown by the I-V curves for all the 100 bottom and 100 top devices of the crossbars [Fig. 2(c)]. These curves are taken by applying a conservative -1.8 V reset voltage and  $300-\mu\text{A}$  set current more desirable for analog switching behavior, and show an ON/OFF current ratio of  $\sim$ 10 at small biases. The application of more aggressive reset voltage of -2.4 V increases the ON/OFF ratios to >100 [Fig. 2(d)].

The device-to-device variations in switching behavior were investigated by characterizing the effective switching thresholds for all devices in the circuit. Each device was first tuned to a high conductive state of 200 k $\Omega$ . The device was then set to 70 k $\Omega$  using write voltage pulses of gradually increasing positive amplitude, and after that reset back to 200 k $\Omega$  using write voltage pulses of gradually increasing negative amplitude [Fig. 2(e)]. The bottom and top devices have similar threshold distributions, as shown in Fig. 2(f), which show set and reset threshold voltages calculated as the smallest voltages at which the cumulative changes in resistance were at least 10%. For all tuning measurements,  $500-\mu$ s-long write voltage pulses were applied in a V/2-biasing configuration, while read measurements were performed in ground configuration with 0.3 V read pulses.

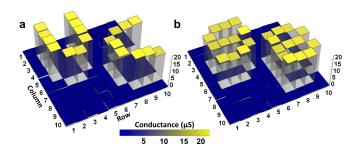

The most exciting feature of the developed memristive crossbar circuits is their analog memory property. The devices in both layers show good analog tunability. For example, Fig. 3(a) and (b) shows the results of tuning of the selected bottom and top layer devices to a  $20-\mu S$  desired conductance with an excellent accuracy and state uniformity. Fig. 4(a) and (b) shows results of tuning individual device to 16 clearly distinguishable states equally spaced in the 2-32-µS range. The devices were tuned to 1% precision using the tuning algorithm presented in [21] with 500- $\mu$ S-long voltage pulses of maximum amplitudes  $\pm 2.6$  V and a step of  $\pm 0.01$  V. The ultimate precision was not investigated, but the previous work [21] showed that it is dependent on the noise level and on the state. Moreover, there is no noticeable drift in conductance at room temperature over a measured  $\sim$ 5 h period [Fig. 4(c)]. Low frequency (1/f) noise is rather high for some devices [Fig. 4(d)], however, it was only observed in a small

Fig. 3. Crossbar programming. (a) Results of tuning 19 bottom crossbar devices to  $20~\mu S$ . Average device conductance and its standard deviation were 21.33 and 1.08  $\mu S$ , respectively. (b) Results of tuning 25 devices in the top crossbar to  $20~\mu S$  with 10% precision. Average device conductance and its standard deviation were 19.52 and 1.13  $\mu S$ , respectively. The tuning was performed using previously developed algorithm [21] with 500- $\mu S$  voltage pulses with maximum  $\mu S$ . V and a step of  $\mu S$ . W, which was extended to crossbar circuits by applying write voltages in V/2-bias configuration [20], [39].

Fig. 4. Multistate tuning and retention. (a) and (b) Tuning results to 16 different conductive states with 1% precision using the algorithm in [21] and Fig. 3, equally spaced from 2 to 32  $\mu$ S, for (a) R2C2 bottom and (b) R2C2 top devices. The state was read in virtual ground configuration every 10 ms by applying 500- $\mu$ s-long 0.3 V high-voltage pulse for a total of 100 readouts. (c) Retention of the OFF (dark), ON (light), and intermediate states (medium brightness) for bottom and top devices, measured at room temperature. (d) Representative worst case low frequency (1/f) noise for a top device.

fraction ( $\sim$ 20%) of the devices, and was more pronounced in the top-layer crossbar, probably due to surface defects introduced during the planarization process.

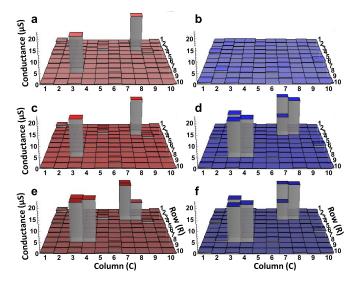

The high switching temperature and the thin shared middle electrode posed a risk for thermal crosstalk in the structure. Forming and switching of the bottom and top devices did not disturb the state of others (Fig. 5), thus suggesting that thermal crosstalk is negligible.

Fig. 5. Reliable crossbar operation, free of thermal crosstalk. (a) and (b) Switching on two bottom devices—R3C8 and R8C3 [see (a)]. The neighboring device states are unaffected. (c) and (d) Switching on six top devices—R2C7, R3C7, R3C8, R7C3, R8C3, and R8C4 [see (d)]. The neighboring device states are unaffected. (e) and (f) Switching on four more bottom devices—R2C7, R3C7, R7C3, and R8C4 [see (e)]. The neighboring device states are unaffected, but the R3C8 device state is changed slightly, probably due to the half-select problem. The conductance maps were read at 0.3 V in the "virtual ground" configuration. Left: bottom crossbar conductances. Right: top crossbar conductances.

### IV. DISCUSSION

We believe that the presented results are encouraging in that fully functional two-layer memristive crossbar circuits with analog memory functionality that can be fabricated in academic settings. The fabrication process has a low temperature budget, with the highest temperature being 175 °C during the sacrificial  ${\rm SiO_2}$  deposition for planarization. Therefore, such a developed process is compatible with back-end-of-line integration with CMOS circuits and can be extended to the fabrication of multiple (>2) crossbar layers.

By utilizing industry-grade fabrication tools, it should be straightforward to increase the scale, lateral density, and the number of layers. Indeed, the crossbar line pitch in this paper was limited by the resolution of the available DUV patterning tool. Recent studies showed that similar metal-oxide devices based on the same bilayer stack of materials could be scaled to  $<10\times10$  nm² dimensions and still preserve excellent analog memory functionality [22], [40]. In fact, many memristor characteristics, which are particularly important for increasing the crossbar size, are improved upon scaling down the device's lateral dimensions. For example, switching threshold variations and switching currents have been shown to reduce upon scaling in metal-oxide devices [23], [40] likely due to reduced parasitic leakage and secondary switching [41].

Some of the immediate future works could be targeted on improving fabrication process to further reduce device variations in multilayer crossbar circuits. For example, a better wafer scale yield for planarization could be achieved through a back-end-of-line polishing technique [42], [43], which removes all the sacrificial dielectric while only slightly

polishing the metal lines, and thus making sure that all the middle electrodes are fully exposed before the deposition on the new crossbar layer. The impact of the electrode slope on the device performance should be further investigated.

Finally, let us mention that though we have not tried to optimize device I-V nonlinearity in this paper, it was not absolutely crucial for the considered crossbar size. Selector functionality is not essential for the operation of neuromorphic circuits. During operation, all crossbar lines are biased to certain voltages, and currents from all devices are collected, so that there are no leakage or stray currents flowing in the circuit [20]. It might be beneficial to have selector functionality to reduce leakages in the half-selected devices during the write operation, i.e., upon tuning, to avoid voltage drops across wires. However, this problem can also be solved by reducing line resistance, which should be possible with industrial-grade fabrication tools. By comparison with previous lift-off techniques, the developed fabrication process could be modified to increase metal line thickness through the use of a thicker hard mask for the Ar IBE.

# V. CONCLUSION

In summary, we have experimentally demonstrated analog memory functionality in a passive stack of two monolithically integrated  $10 \times 10 \text{ TiO}_2$ -based memristor crossbar circuits. To ensure reliable stacking and compatibility with a CMOS process, a <175 °C temperature budget was used during the fabrication. The active layers of precisely controlled stoichiometry were deposited *in situ* via reactive sputtering and patterned with Ar ion beam milling. The bottom crossbar layer was planarized to reduce the step height and to provide a smooth surface for the top device deposition. As a result, 74% die yield was achieved across the 4-in wafer.

All of the 100 bottom and 100 top devices were formed and switched successfully. The devices in the two layers showed fairly similar behavior and threshold characteristics with good retention for the ON, OFF, and intermediate states. The devices were tuned to 16 clearly distinguishable states equally spaced in the 2–32- $\mu$ S range showing good analog behavior. The demonstrated results are an important step toward multilayer passive memristive crossbar circuits that can be efficiently integrated with CMOS circuits, in particular of the 3-D CMOL variety, for neuromorphic and analog computing applications.

### REFERENCES

- R. Waser, R. Dittmann, G. Staikov, and K. Szot, "Redox-based resistive switching memories-nanoionic mechanisms, prospects, and challenges," *Adv. Mater.*, vol. 21, nos. 25–26, pp. 2632–2663, 2009.

- [2] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *Nature*, vol. 453, pp. 80–83, May 2008.

- [3] H.-S. P. Wong et al., "Metal-oxide RRAM," Proc. IEEE, vol. 100, no. 6, pp. 1951–1970, Jun. 2012, doi: 10.1109/JPROC.2012.2190369.

- [4] K. K. Likharev, "Hybrid CMOS/nanoelectronic circuits: Opportunities and challenges," *J. Nanoelectron. Optoelectron.*, vol. 3, no. 3, pp. 203–230, 2008.

- [5] J. J. Yang, D. B. Strukov, and D. R. Stewart, "Memristive devices for computing," *Nature Nanotechnol.*, vol. 8, no. 1, pp. 13–24, 2013.

- [6] Q. Xia et al., "Memristor-CMOS hybrid integrated circuits for reconfigurable logic," Nano Lett., vol. 9, no. 10, pp. 3640–3645, 2009.

- [7] C. J. Chevallier *et al.*, "A 0.13μm 64Mb multi-layered conductive metal-oxide memory," in *Proc. IEEE ISSCC*, San Francisco, CA, USA, Feb. 2010, pp. 260–261.

- [8] K.-H. Kim et al., "A functional hybrid memristor crossbar-array/CMOS system for data storage and neuromorphic applications," Nano Lett., vol. 12, no. 1, pp. 389–395, 2011.

- [9] T.-Y. Liu et al., "A 130.7 mm<sup>2</sup> 2-layer 32-Gb ReRAM memory device in 24-nm technology," *IEEE J. Solid-State Circuits*, vol. 49, no. 1, pp. 140–153, Jan. 2014.

- [10] C. H. Wang et al., "Three-dimensional 4F<sup>2</sup> ReRAM with vertical BJT driver by CMOS logic compatible process," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2466–2472, Aug. 2011.

- [11] M. J. Lee et al., "2-stack 1D-1R cross-point structure with oxide diodes as switch elements for high density resistance RAM applications," in *Proc. IEDM*, Washington, DC, USA, Dec. 2007, pp. 771–774.

- [12] M. C. Hsieh et al., "Ultra high density 3D via RRAM in pure 28nm CMOS process," in Proc. IEDM, Washington, DC, USA, Dec. 2013, pp. 10.3.1–10.3.4.

- [13] S. H. Jo, T. Kumar, S. Narayanan, W. D. Lu, and H. Nazarian, "3D-stackable crossbar resistive memory based on field assisted superlinear threshold (FAST) selector," in *Proc. IEDM*, Washington, DC, USA, Dec. 2014, pp. 6.7.1–6.7.4.

- [14] L. Y. Huang et al., "ReRAM-based 4T2R nonvolatile TCAM with 7x NVM-stress reduction, and 4x improvement in speed-wordlengthcapacity for normally-off instant-on filter-based search engines used in big-data processing," in Symp. VLSI Circuits Dig. Tech. Papers, Honolulu, HI, USA, Jun. 2014, pp. 1–2.

- [15] K. K. Likharev, "CrossNets: Neuromorphic hybrid CMOS/ nanoelectronic networks," Sci. Adv. Mater., vol. 3, no. 3, pp. 322–331, 2011.

- [16] S. H. Jo, T. Chang, I. Ebong, B. B. Bhadviya, P. Mazumder, and W. Lu, "Nanoscale memristor device as synapse in neuromorphic systems," *Nano Lett.*, vol. 10, no. 4, pp. 1297–1301, 2010.

- [17] G. S. Snider, "Self-organized computation with unreliable, memristive nanodevices," *Nanotechnology*, vol. 18, no. 36, p. 365202, 2007.

- [18] D. Kuzum, S. Yu, and H. P. Wong, "Synaptic electronics: Materials, devices and applications," *Nanotechnology*, vol. 24, no. 38, p. 382001, 2013

- [19] F. Alibart, E. Zamanidoost, and D. B. Strukov, "Pattern classification by memristive crossbar circuits using ex situ and in situ training," Nature Commun., vol. 4, p. 2072, May 2013.

- [20] M. Prezioso, F. Merrikh-Bayat, B. D. Hoskins, G. C. Adam, K. K. Likharev, and D. B. Strukov, "Training and operation of an integrated neuromorphic network based on metal-oxide memristors," *Nature*, vol. 521, pp. 61–64, May 2015, doi: 10.1038/nature14441.

- [21] F. Alibart, L. Gao, B. D. Hoskins, and D. B. Strukov, "High precision tuning of state for memristive devices by adaptable variation-tolerant algorithm," *Nanotechnology*, vol. 23, no. 7, p. 075201, 2012.

[22] B. Govoreanu *et al.*, "10×10 nm² Hf/HfO<sub>x</sub> crossbar resistive RAM with

- [22] B. Govoreanu *et al.*, "10×10 nm² Hf/HfO<sub>x</sub> crossbar resistive RAM with excellent performance, reliability and low-energy operation," in *Proc. IEDM*, Washington, DC, USA, Dec. 2011, pp. 31.6.1–31.6.4.

- [23] J. Lee, J. Park, S. Jung, and H. Hwang, "Scaling effect of device area and film thickness on electrical and reliability characteristics of RRAM," in *Proc. IEEE Int. Interconnect Technol. Conf. (IITC)*, Dresden, Germany, May 2011, pp. 1–3.

- [24] D. B. Strukov, "Nanotechnology: Smart connections," *Nature*, vol. 476, pp. 403–405, Aug. 2011.

- [25] D. B. Strukov and R. S. Williams, "Topological framework for three-dimensional circuits with multilayer crossbar arrays," *Proc. Nat. Acad. Sci. USA*, vol. 106, pp. 20155–20158, Dec. 2009.

- [26] S. G. Park et al., "A non-linear ReRAM cell with sub-1μA ultralow operating current for high density vertical resistive memory (VRRAM)," in Proc. IEDM, Washington, DC, USA, Dec. 2012, pp. 8–20.

- [27] I. Baek et al., "Realization of vertical resistive memory (VRRAM) using cost effective 3D process," in Proc. IEDM, Washington, DC, USA, Dec. 2011, pp. 8–31.

- [28] H. Li et al., "Four-layer 3D vertical RRAM integrated with FinFET as a versatile computing unit for brain-inspired cognitive information processing," in Proc. IEEE Symp. VLSI Technol., Honolulu, HI, USA, Jun. 2016, pp. 1–2.

- [29] Y. Bai et al., "Study of multi-level characteristics for 3D vertical resistive switching memory," Sci. Rep., vol. 4, p. 5780, Jul. 2014.

- [30] S. Yu, H. Y. Chen, B. Gao, J. Kang, and H. S. P. Wong, "HfO<sub>x</sub>-based vertical resistive switching random access memory suitable for bit-costeffective three-dimensional cross-point architecture," ACS Nano, vol. 7, no. 3, pp. 2320–2325, 2013.

- [31] L. Zhang, S. Cosemans, D. J. Wouters, B. Govoreanu, G. Groeseneken, and M. Jurczak, "Analysis of vertical cross-point resistive memory (VRRAM) for 3D RRAM design," in *Proc. IEEE Int. Memory Workshop (IMW)*, May 2013, pp. 155–158.

- [32] P. Y. Chen, Z. Li, and S. Yu, "Design tradeoffs of vertical RRAM-based 3-D cross-point array," *IEEE Trans. Very Large Scale Integr. (VLSI)* Syst., vol. 23, no. 12, pp. 3460–3467, Dec. 2016.

- [33] A. Jain, R. E. Jones, R. Chatterjee, and S. Pozder, "Analytical and numerical modelling of the thermal performance of three-dimensional integrated circuits," *IEEE Trans. Compon. Packag. Technol.*, vol. 33, no. 1, pp. 56–63, Mar. 2010.

- [34] J. L. Ayala, A. Sridhar, and D. Cuesta, "Thermal modelling and analysis of 3D multi-processor chips," *Integr. VLSI J.*, vol. 43, no. 4, pp. 327–341, 2010

- [35] J. P. Strachan, D. B. Strukov, J. Borghetti, J. J. Yang, G. Medeiros-Ribeiro, and R. S. Williams, "The switching location of a bipolar memristor: Chemical, thermal and structural mapping," *Nanotechnology*, vol. 22, no. 25, p. 254015, 2011.

- [36] P. Sun et al., "Thermal crosstalk in 3-dimensional RRAM crossbar array," Sci. Rep., vol. 5, p. 13504, Jul. 2015.

- [37] G. C. Adam, B. D. Hoskins, M. Prezioso, and D. B. Strukov, "Optimized stateful material implication logic for three dimensional data manipulation," *Nano Res.*, vol. 9, no. 12, pp. 3914–3923, 2016.

- [38] M. Prezioso *et al.*, "Modelling and implementation of firing-rate neuromorphic-network classifiers with bilayer Pt/Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2-x</sub>/Pt memristors," in *Proc. IEDM*, Washington, DC, USA, Dec. 2015, pp. 17.4.1–17.4.4.

- [39] D. B. Strukov and K. K. Likharev, "Reconfigurable Nano-crossbar architectures," in *Nanoelectronics and Information Technology*, R. Waser, Ed., 3rd ed. New York, NY, USA: Wiley, 2012.

- [40] S. Pi, P. Lin, and Q. Xia, "Cross point arrays of 8 nm × 8 nm memristive devices fabricated with nanoimprint lithography," *J. Vac. Sci. Technol. B*, vol. 31, no. 6, p. 06FA02, 2013.

- [41] F. M. Bayat, B. Hoskins, and D. B. Strukov, "Phenomenological modeling of memristive devices," *Appl. Phys. A*, vol. 118, no. 3, pp. 770–786, 2015.

- [42] M. S. Islam *et al.*, "Ultra-smooth platinum surfaces for nanoscale devices fabricated using chemical mechanical polishing," *Appl. Phys. A*, vol. 80, no. 6, pp. 1385–1389, 2005.

- [43] K. Tanwar et al., "BEOL Cu CMP process evaluation for advanced technology nodes," J. Electrochem. Soc., vol. 160, no. 12, pp. D3247–D3254, 2013.

Gina C. Adam received the B.Eng. in applied electronics from the University Politehnica of Bucharest, Bucharest, Romania, in 2010, and the M.S. and Ph.D. degrees in electrical engineering from the University of California at Santa Barbara, Santa Barbara, CA, USA, in 2012 and 2015, respectively.

She is currently a Marie Sklodowska-Curie Post-Doctoral Fellow with the National Institute for Research and Development in Microtechnologies, IMT Bucharest, Bucharest, Romania.

Brian D. Hoskins received the B.S. and M.S. degrees in materials science and engineering from Carnegie Mellon University, Pittsburgh, PA, USA, in 2010 and 2011, respectively, and the Ph.D. degree in materials from the University of California at Santa Barbara, Santa Barbara, CA, USA, in 2016.

His research interests are material growth and characterization and device engineering for hardware implementations of neuromorphic systems.

Mirko Prezioso received the M.S. degree in theoretical condensed matter physics and the Ph.D. degree in advanced materials science and technology from the University of Parma, Parma, Italy, in 2004 and 2008, respectively.

Since 2013, he has been a Research Assistant Professor with the University of California at Santa Barbara, Santa Barbara, CA, USA, where he has been working on memristors and neuromorphic hardware.

Bhaswar Chakrabarti received the B.Tech. degree in radiophysics and electronics from the University of Calcutta, Kolkata, India, in 2005, the M.Tech. degree in nanoscience and technology from Jadavpur University, Kolkata, in 2007, and the Ph.D. degree in materials science and technology from The University of Texas at Dallas, Richardson, TX, USA, in 2013.

He is currently a Post-Doctoral Researcher with the University of California at Santa Barbara, Santa Barbara, CA, USA.

Farnood Merrikh-Bayat received the B.S., M.S., and Ph.D. degrees from the Sharif University of Technology, Tehran, Iran, in 2006, 2008, and 2012, respectively, all in electrical and computer engineering, and the Ph.D. degree in electrical and computer engineering from the University of California at Santa Barbara, Santa Barbara, CA, USA, in 2015.

He is currently a Post-Doctoral Researcher in computer engineering with the University of California at Santa Barbara.

Dmitri B. Strukov (M'02–SM'16) received the M.S. degree in applied physics and mathematics from the Moscow Institute of Physics and Technology, Moscow oblast, Russia, in 1999, and the Ph.D. degree in electrical engineering from Stony Brook University, Stony Brook, NY, USA, in 2006.

He is currently an Associate Professor of Electrical and Computer Engineering with University of California at Santa Barbara, Santa Barbara, CA, USA.