As the demand for data continues to increase, optical interconnects are becoming more attractive for on-chip and short-reach data links. Our group has been developing technologies for optical interconnects to and inside data centers, and we have also been investigating the design and architecture of optically interconnected manycore processor systems. Important technologies for these applications include low-power and high-speed microring modulators, low-loss waveguides, and high-efficiency laser sources. Cross-layer floor plan optimization can assist in addressing the tradeoffs between fabrication and system complexity.

Selected Relevant Publications:

- “Photonic Interconnects for Computing Systems: Understanding and Pushing Design Challenges,” River Publishers, 2017.

- “Adaptive Tuning of Photonic Devices in a Photonic NoC Through Dynamic Workload Allocation,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 36, no. 5, pp. 801-814, 2016.

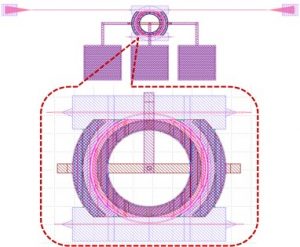

- “Sharing and Placement of On-Chip Laser Sources in Silicon Photonic NoCs,” Networks-on-Chip (NoCS), 2014.

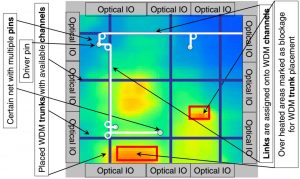

- “Cross-Layer Floorplan Optimization For Silicon Photonic NoCs In Many-Core Systems,” Design, Automation and Test in Europe (DATE), 2016.

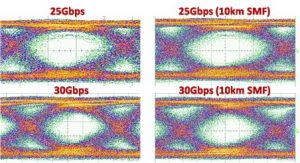

- “High-Speed Silicon Electro-Optic Microring Modulator for Optical Interconnects,” Photonics Technology Letters, vol. 26, no. 10, 2014.

- “30-Gbps Silicon Microring Modulator for Short- and Medium-Reach Optical Interconnects,” Optical Fiber Communication Conference (OFC), paper Th2A.4, 2014.

Collaborators: Integrated Circuits & Systems Group and Performance & Energy-Aware Computing Laboratory at BU, VLSI CAD Laboratory at UC San Diego, Scuola Superiore Sant’Anna, CNIT