Lab Spotlights — Computer Engineering

PQRS Computer Architecture Lab

Behrooz Parhami

High Level Systems Design Lab

Forrest Brewer

Novel Electronic Devices and Computing Systems Lab

Dmitri Strukov

PQRS Computer Architecture Lab

Behrooz Parhami

Parhami's research projects entail aspects of computer design and architecture that are captured by the abbreviation PQRS, with each aspect defined by a set of keywords:

- Performance, incorporates latency, speedup, throughput

- Quality, embodies accuracy, parts/energy economy, stability

- Reliability, encompasses correctness, timeliness, safety

- Scalability, spans modularity, packageability, expandability

In recent years, the focus has somewhat expanded to also include TUVW, as defined below:

- Testability, during design, implementation, and field use

- Usability, while requiring minimal expertise and training

- Versatility, to allow mass production for economy of scale

- Workability, a synonym for practicality in design and use

Within the rather broad field of computer design and architecture, Professor Parhami's active research interests fall within three subareas:

Professor Parhami's:

High Level Systems Design Lab

Forrest Brewer

The High Level Systems Design lab builds circuits. Our lab encompasses the stages of electronic design from the development of tools for exploring what to build to the layout of transistors for the fabrication of prototype chips. Once an integrated circuit is fabricated we test the final design to verify its construction and incorporate the results into our body of knowledge used to built the future chips.

Radiation Hardened Electronics

Space exploration, physics experiments, power plants and medical technology all share a need for electronics which survive in extreme environments, where electromagnetic radiation can destroy traditional digital electronics. Our lab develops tools that enable the design of circuits able to withstand the impact of radiation and still function successfully. This means when a circuit needs to survive inside of a particle accelerator we are able to build a design for that or if a robot needs to be controlled in space, we can build circuits for that, too.

Asynchronous Architectures & CAD Tools

Our lab explores designs where the clock is missing and the computation is carried out using event driven operations. We build CAD tools to verify and synthesize closed models of high performance asynchronous systems.

Mixed Signal Circuit/System Design

Mixed signal design intermingles the traditional paradigm of boolean logic with the physics of analog electronics to built novel integrated circuits. Our research considers how concepts like integrated charge enable successful designs of serial links in a design space where traditional metrics would predict failure.

Bitstream Control & Signal Processing

This research involves developing formal methodologies and techniques for designing digital circuits around computation on raw bitstreams. The results are digital circuits which deliver low latency, low complexity, and low power performance for applications like active noise cancellation and micro-electro-mechanical systems (MEMS) control.

Professor Brewer's:

Novel Electronic Devices and Computing Systems Laboratory

Dmitri Strukov

Research Focus:

- Novel electronic devices with a particular focus on resistive switching effects

- Circuit design for novel electronic devices

- Emerging architectures for computing and design automation

Particular Focus - CMOL Technology:

The basic idea of CMOL circuits (standing for Cmos + MOLecular-scale devices) is to combine the advantages of the CMOS technology including its flexibility and high fabrication yield with those of ultra dense stackable crosspoint devices, e.g. those based on resistive switching phenomena. The nanoscale devices are naturally incorporated into the crossbar fabric enabling very high functional density at acceptable fabrication cost. In particular, CMOL circuits are especially suitable for digital memories, reconfigurable computing and bio-inspired signal processing.

Professor Strukov's:

Scalable Energy-efficient Architecture Lab

Yuan Xie

Test and Verification Lab

Li-C. Wang

Nanoelectronics Research Lab

Kaustav Banerjee

Scalable Energy-efficient Architecture Lab (SEALab)

Yuan Xie

SEALab aims at leveraging emerging technologies (with emphasize on 3D integration and emerging nonvolatile memory) for edge-cutting applications (e.g., machine learning and bioinformatics).

SEALab distinguishes itself by strong cross-layer researches going from device to application, and works on circuit design, EDA tools, and computer architecture at the same time. Recent research highlights are as follows:

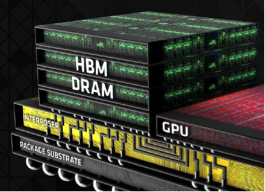

3D Design & Design Automation

The architecture we proposed in 2012 turns to the world-first 3D GPU on the market (AMD Fury X). Our recent researches including cost analysis for 2.5D/3D integration, heterogonous integration, and 3D based hardware security study.

Modeling, Architecture and Application for Emerging Nonvolatile Memory

We help the community to understand NVM’s pros and cons for better utilizing them to improve the future computing systems, e.g., IoT, GPGPU, NoC, and Data Center. We are also interested in utilizing NVM’s nonvolatility feature for normally-off computing, check-pointing, and persistent memory.

Energy-efficient Hardware for Machine Learning and Neuromorphic Computing

We explore optimizing machine learning applications on parallel and heterogonous architecture as well as reconfigurable fabric. We also leverage emerging technologies for machine learning and bio-inspired applications, e.g., 3D stacked high bandwidth memory, low-power NVM.

Professor Xie's:

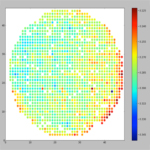

Test and Verification Lab

Li-C. Wang

The Test and Verification Lab leverages machine learning algorithms to assist in the process of knowledge discovery during the design and manufacturing process.

The application of our research lies in two fronts:

Test: During the test process, numerous measurements are performed on each chip to ensure that each chip meets its design specifications and is working properly. We examine ways to leverage this data to reveal new insights into the manufacturing process that can then be used to create positive outcomes for the company. So examples of these outcomes from previous projects include but are not limited to:

- Improving Quality: Using statistical methodologies to complement existing testing for the purpose of screening future in-field failures for high-reliability products;

- Improving Yield: Identifying the key process parameters that are contributing to abnormal yield fluctuations.

- Reducing Cost: Identifying redundant tests by constructing predictive models based on remaining tests.

Verification: Functional verification is an iterative process since the design changes over time. Tons of machine hours are spent on simulating the tests in hope of covering all corners of the design and capturing functional bugs. Valuable knowledge is embedded in the simulation data and regression tests accumulated along the verification process. Data mining techniques can be applied to extract the knowledge and leverage them to improve the verification efficiency. Here are two example applications from previous projects:

- Reducing simulation cost: Building statistical models to filter out ineffective tests for cutting down the cost of simulation time and licenses.

- Improving testbench: Extracting rules from novel tests to present to the verification engineers so that they can improve the test generation.

Professor Wang's:

Nanoelectronics Research Lab

Kaustav Banerjee

The Banerjee group focuses on various aspects of nanoelectronics research, including fundamental physics, electrical and thermal modeling, robust circuit/architecture design, as well as nanomaterial synthesis and nanostructure/device fabrication. Work in the Nanoelectronics Research Lab (NRL) falls into one of the following areas:

- Carbon Nanoelectronics: Physics, technology, and applications of graphene and carbon nanotubes in electronics, energy harvesting /storage and bio/medicine

- Green Electronics: Sub-kT/q devices such as tunneling-FETs and NEMS; ultra low-voltage circuit and system design

- Nano-Devices & 3-D ICs: Emerging CMOS technologies such as FinFET and Nanowire-FET; innovative digital and memory devices; 3-D heterogeneous ICs; device-circuit interactions

- Nanoscale Interconnects: Ultra high-frequency modeling/extraction for VLSI interconnects and passive elements; exploration of emerging interconnect/passive structures and technologies

Professor Banerjee's: